## ETSI TS 103 813 V15.1.0 (2022-02)

Smart Secure Platform (SSP); Test Specification, SPI interface (Release 15)

# Reference RTS/SCP-00T103813vf10 Keywords SPI, SSP, testing

#### **ETSI**

650 Route des Lucioles F-06921 Sophia Antipolis Cedex - FRANCE

Tel.: +33 4 92 94 42 00 Fax: +33 4 93 65 47 16

Siret N° 348 623 562 00017 - APE 7112B Association à but non lucratif enregistrée à la Sous-Préfecture de Grasse (06) N° w061004871

#### Important notice

The present document can be downloaded from: http://www.etsi.org/standards-search

The present document may be made available in electronic versions and/or in print. The content of any electronic and/or print versions of the present document shall not be modified without the prior written authorization of ETSI. In case of any existing or perceived difference in contents between such versions and/or in print, the prevailing version of an ETSI deliverable is the one made publicly available in PDF format at <a href="https://www.etsi.org/deliver">www.etsi.org/deliver</a>.

Users of the present document should be aware that the document may be subject to revision or change of status.

Information on the current status of this and other ETSI documents is available at <a href="https://portal.etsi.org/TB/ETSIDeliverableStatus.aspx">https://portal.etsi.org/TB/ETSIDeliverableStatus.aspx</a>

If you find errors in the present document, please send your comment to one of the following services: https://portal.etsi.org/People/CommiteeSupportStaff.aspx

#### Notice of disclaimer & limitation of liability

The information provided in the present deliverable is directed solely to professionals who have the appropriate degree of experience to understand and interpret its content in accordance with generally accepted engineering or other professional standard and applicable regulations.

No recommendation as to products and services or vendors is made or should be implied.

No representation or warranty is made that this deliverable is technically accurate or sufficient or conforms to any law and/or governmental rule and/or regulation and further, no representation or warranty is made of merchantability or fitness for any particular purpose or against infringement of intellectual property rights.

In no event shall ETSI be held liable for loss of profits or any other incidental or consequential damages.

Any software contained in this deliverable is provided "AS IS" with no warranties, express or implied, including but not limited to, the warranties of merchantability, fitness for a particular purpose and non-infringement of intellectual property rights and ETSI shall not be held liable in any event for any damages whatsoever (including, without limitation, damages for loss of profits, business interruption, loss of information, or any other pecuniary loss) arising out of or related to the use of or inability to use the software.

#### Copyright Notification

No part may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm except as authorized by written permission of ETSI.

The content of the PDF version shall not be modified without the written authorization of ETSI.

The copyright and the foregoing restriction extend to reproduction in all media.

© ETSI 2022. All rights reserved.

## Contents

| Intelle        | ectual Property Rights                                                  | 12 |

|----------------|-------------------------------------------------------------------------|----|

| Forew          | vord                                                                    | 12 |

| Moda           | ıl verbs terminology                                                    | 13 |

| Introd         | luction                                                                 | 13 |

| 1              | Scope                                                                   | 14 |

| 2              | References                                                              | 14 |

| 2.1            | Normative references                                                    |    |

| 2.2            | Informative references                                                  |    |

|                |                                                                         |    |

| 3              | Definition of terms, symbols, abbreviations and formats                 |    |

| 3.1            | Terms                                                                   |    |

| 3.2            | Symbols                                                                 |    |

| 3.3            | Abbreviations                                                           |    |

| 3.4            | Formats                                                                 |    |

| 3.4.1          | Format of the applicability table                                       |    |

| 3.4.2<br>3.4.3 | Format of the applicability table                                       |    |

| 3.4.3<br>3.4.4 | Format of the conformance requirements tables  Numbers and Strings      |    |

| 3.4.4          | Format of the sequences in the test procedure                           |    |

| 3.4.3          | •                                                                       |    |

| 4              | Test environments                                                       | 18 |

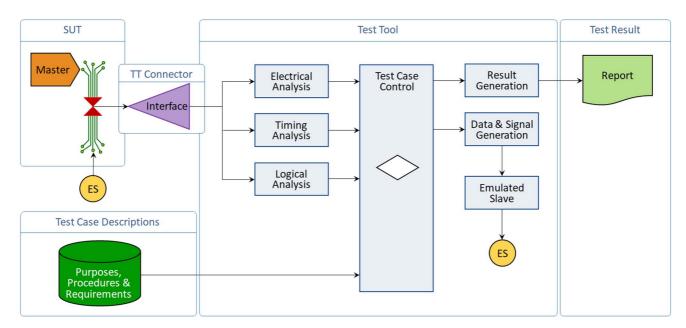

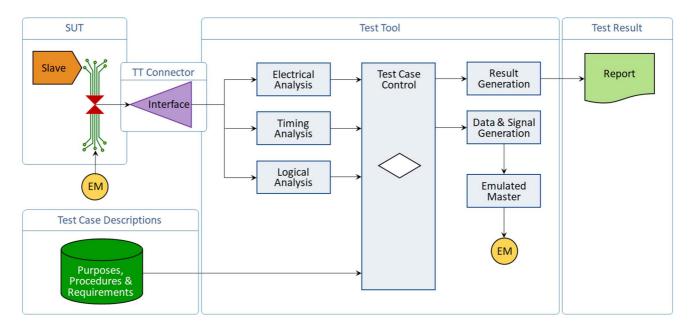

| 4.0            | Description of the test environments                                    | 18 |

| 4.1            | Testing architectures.                                                  |    |

| 4.1.0          | Description of the testing architectures                                |    |

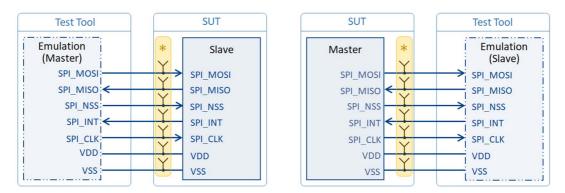

| 4.1.1          | Testing architecture - SPI with an electrical interface using 5 signals |    |

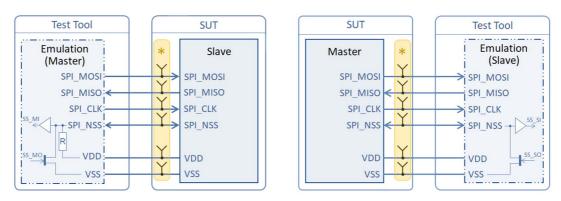

| 4.1.2          | Testing architecture - SPI with an electrical interface using 4 signals |    |

| 4.2            | Test tool                                                               |    |

| 4.2.0          | Capabilities of the test tool                                           |    |

| 4.2.1          | Adaption of the test tool                                               |    |

| 4.3            | Table of optional features                                              |    |

| 4.4            | Applicability tables                                                    |    |

| 4.4.1          | Applicability table - testing of the SPI Master                         |    |

| 4.4.2<br>4.4.3 | Applicability table - testing of the SPI Slave                          |    |

| 4.4.3<br>4.5   | Test cases and test case description                                    |    |

| 4.5.1          | Common conditions and test steps                                        |    |

| 4.5.1.1        | *                                                                       |    |

| 4.5.1.2        |                                                                         |    |

| 4.5.2          | Test case description                                                   |    |

| 4.5.2.0        | *                                                                       |    |

| 4.5.2.1        | 1                                                                       |    |

| 4.5.2.2        |                                                                         |    |

| 4.5.2.3        | 3 Test procedure                                                        | 26 |

| 4.5.2.4        |                                                                         |    |

| 4.6            | Implicit testing                                                        | 27 |

| 4.7            | Pass criterion                                                          | 27 |

| 5              | Conformance requirements                                                | 27 |

| 5.0            | Conformance requirement references                                      |    |

| 5.1            | Electrical interfaces                                                   |    |

| 5.1.0          | Electrical interfaces - common requirements                             |    |

| 5.1.1          | Physical interface with 5 signals                                       |    |

| 5.1.2          | Physical interface with 4 signals                                       |    |

| 5.1.3          | Electrical characteristics                                              |    |

| 5.1.4          | Slave state                                                             |    |

| 5.2            | Data link layer                                                         | 30 |

| 5.2.0              | Overview                                                             | 30 |

|--------------------|----------------------------------------------------------------------|----|

| 5.2.1              | MAC layer                                                            | 30 |

| 5.2.2              | Link layer frame                                                     | 32 |

| 5.2.3              | LLC layers                                                           | 34 |

| 5.2.4              | Interworking of the LLC layers                                       | 34 |

| 5.2.5              | MCT LLC definition                                                   |    |

| 5.2.6              | SHDLC LLC definition                                                 |    |

| 5.2.6.1            |                                                                      |    |

| 5.2.6.2            |                                                                      |    |

| 5.2.7              | Power management                                                     |    |

|                    | -                                                                    |    |

| 6                  | Test cases for electrical interfaces                                 |    |

| 6.0                | Initial conditions for tests of the electrical interfaces            |    |

| 6.0.1              | Common initial conditions for tests of the electrical interfaces     |    |

| 6.0.2              | Pre-conditions for the measurement of DC characteristics             | 39 |

| 6.0.3              | Pre-conditions for the measurement of AC characteristics             | 40 |

| 6.0.4              | Preparation procedure - SPI master AC testing                        | 40 |

| 6.0.5              | Preparation procedure - SPI slave AC testing                         |    |

| 6.0.6              | Post-processing procedure                                            | 41 |

| 6.1                | Electrical characteristics - 5 signals SPI - SPI Master testing      | 41 |

| 6.1.1              | 5 signals SPI - DC characteristics for operational voltage class B   | 41 |

| 6.1.1.1            | ·                                                                    |    |

| 6.1.1.2            | 1 1                                                                  |    |

| 6.1.1.3            |                                                                      |    |

| 6.1.1.4            | <u> </u>                                                             |    |

| 6.1.2              | 5 signals SPI - DC characteristics for operational voltage class C   |    |

| 6.1.2.1            |                                                                      |    |

| 6.1.2.2            |                                                                      |    |

| 6.1.2.3            |                                                                      |    |

| 6.1.2.4            | 1                                                                    |    |

| 6.1.3              | 5 signals SPI - AC characteristics for operational voltage class B   |    |

| 6.1.3.1            |                                                                      |    |

| 6.1.3.2            | 1 1                                                                  |    |

| 6.1.3.2            |                                                                      |    |

| 6.1.3.4            |                                                                      |    |

| 6.1.4              | 5 signals SPI - AC characteristics for operational voltage class C   |    |

| 6.1.4.1            |                                                                      |    |

| 6.1.4.2            | 1 1                                                                  |    |

| 6.1.4.3            |                                                                      |    |

| 6.1.4.4            | r                                                                    |    |

| 6.2                | Electrical characteristics - 5 signals SPI - SPI Slave testing       |    |

| 6.2.1              | 5 signals SPI - Class B, AC characteristics for slave driven signals |    |

| 6.2.1.1            |                                                                      |    |

| 6.2.1.1<br>6.2.1.2 | 1 1                                                                  |    |

| 6.2.1.2<br>6.2.1.3 |                                                                      |    |

| 6.2.1.3<br>6.2.1.4 |                                                                      |    |

| 6.2.1.4<br>6.2.2   | Post condition                                                       |    |

| 6.2.2<br>6.2.2.1   |                                                                      |    |

| 6.2.2.1<br>6.2.2.2 |                                                                      |    |

|                    |                                                                      |    |

| 6.2.2.3            | •                                                                    |    |

| 6.2.2.4            |                                                                      |    |

| 6.3                | Electrical characteristics - 4 signals SPI - SPI Master testing      |    |

| 6.3.1              | 4 signals SPI - DC characteristics for operational voltage class B   |    |

| 6.3.1.1            | 1 1                                                                  |    |

| 6.3.1.2            |                                                                      |    |

| 6.3.1.3            | 1                                                                    |    |

| 6.3.1.4            |                                                                      |    |

| 6.3.2              | 4 signals SPI - DC characteristics for operational voltage class C   |    |

| 6.3.2.1            | 1 1                                                                  |    |

| 6.3.2.2            |                                                                      |    |

| 6.3.2.3            | *                                                                    |    |

| 6324               | Post conditions                                                      | 53 |

| 6.3.3   | 4 signals SPI - AC characteristics for operational voltage class B            |    |

|---------|-------------------------------------------------------------------------------|----|

| 6.3.3.1 | Test purpose                                                                  |    |

| 6.3.3.2 | Initial conditions                                                            |    |

| 6.3.3.3 | Test procedure                                                                |    |

| 6.3.3.4 | Post condition                                                                |    |

| 6.3.4   | 4 signals SPI - AC characteristics for operational voltage class C            |    |

| 6.3.4.1 | Test purpose                                                                  |    |

| 6.3.4.2 | Initial conditions                                                            | 54 |

| 6.3.4.3 | Test procedure                                                                | 54 |

| 6.3.4.4 | Post condition                                                                |    |

| 6.4     | Electrical characteristics - 4 signals SPI - SPI Slave testing                |    |

| 6.4.1   | 4 signals SPI - Class B, AC characteristics for slave driven signals          |    |

| 6.4.1.1 | Test purpose                                                                  |    |

| 6.4.1.2 | Initial conditions                                                            |    |

| 6.4.1.3 | Test procedure                                                                |    |

| 6.4.1.4 | Post condition                                                                |    |

| 6.4.2   | 4 signals SPI - Class C, AC characteristics for slave driven signals          |    |

| 6.4.2.1 | Test purpose                                                                  |    |

| 6.4.2.2 | Initial conditions                                                            |    |

| 6.4.2.3 | Test procedure                                                                |    |

| 6.4.2.4 | Post condition                                                                |    |

| 6.5     | Verification of slave states - SPI Slave testing                              |    |

| 6.5.0   | Explanation of slave states                                                   |    |

| 6.5.1   | Initial state                                                                 |    |

| 6.5.1.1 | Test purpose                                                                  |    |

| 6.5.1.2 | Initial condition                                                             |    |

| 6.5.1.3 | Test procedure                                                                |    |

| 6.5.2   | Configured state                                                              |    |

| 6.5.2.1 | Test purpose                                                                  |    |

| 6.5.2.2 | Initial condition                                                             |    |

| 6.5.2.3 | Test procedure                                                                |    |

| 6.5.3   | 5 signals SPI - Pro-active state                                              |    |

| 6.5.3.1 | Test purpose                                                                  |    |

| 6.5.3.2 | Initial condition                                                             |    |

| 6.5.3.3 | Test procedure                                                                |    |

| 6.5.4   | 4 signals SPI - Pro-active state                                              |    |

| 6.5.4.1 | Test purpose                                                                  |    |

| 6.5.4.2 | Initial condition                                                             |    |

| 6.5.4.3 | Test procedure                                                                |    |

| 6.5.5   | 4 signals SPI - Busy state                                                    |    |

| 6.5.5.1 | Test purpose                                                                  |    |

| 6.5.6   | Power saving mode state                                                       |    |

| 6.5.6.1 | Test purpose                                                                  | 63 |

| 7       | Fest cases for data link layer- MAC Layer                                     | 63 |

| 7.0     | Common conditions for data link layer test cases                              |    |

| 7.0.1   | Pre-condition for data link layer test cases                                  |    |

| 7.0.2   | MAC parameter determination procedure - SPI Master testing                    |    |

| 7.0.3   | MAC parameter determination procedure - SPI Slave testing                     |    |

| 7.0.4   | Post-condition for data link layer test cases                                 |    |

| 7.1     | MAC Layer - 5 signals SPI - SPI Master testing                                |    |

| 7.1.1   | 5 signals SPI - Master behaviour during initial data transfer initiation      |    |

| 7.1.1.1 | Test purpose                                                                  |    |

| 7.1.1.2 | Initial conditions                                                            |    |

| 7.1.1.3 | Test procedure                                                                |    |

| 7.1.1.4 | Post-condition                                                                |    |

| 7.1.2   | 5 signals SPI - Master behaviour during data transfer initiation              |    |

| 7.1.2.1 | Test purpose                                                                  |    |

| 7.1.2.2 | Initial conditions                                                            |    |

| 7.1.2.3 | Test procedure                                                                |    |

| 7.1.2.4 | Post-condition                                                                |    |

| 7.1.3   | 5 signals SPI - Master behaviour during simultaneous data transfer initiation | 67 |

|         |                                                                               |    |

| 7.1.3.1 | Test purpose                                                                  | 67 |

|---------|-------------------------------------------------------------------------------|----|

| 7.1.3.2 | Initial conditions                                                            | 67 |

| 7.1.3.3 | Test procedure                                                                |    |

| 7.1.3.4 | Post-condition                                                                |    |

| 7.1.4   | 5 signals SPI - MAC deactivation                                              |    |

| 7.1.4.1 | Test purpose                                                                  |    |

| 7.1.4.2 | Initial conditions                                                            | 68 |

| 7.1.4.3 | Test procedure                                                                | 68 |

| 7.1.4.4 | Post-condition                                                                |    |

| 7.2     | MAC Layer - 5 signals SPI - SPI Slave testing                                 |    |

| 7.2.1   | 5 signals SPI - Slave behaviour at initial MAC activation                     |    |

| 7.2.1.1 | Test purpose                                                                  | 69 |

| 7.2.1.2 | Initial conditions                                                            | 69 |

| 7.2.1.3 | Test procedure                                                                |    |

| 7.2.1.4 | Post-condition                                                                | 69 |

| 7.2.2   | 5 signals SPI - Slave behaviour during data transfer initiation -nominal test | 70 |

| 7.2.2.1 | Test purpose                                                                  | 70 |

| 7.2.2.2 | Initial conditions                                                            | 70 |

| 7.2.2.3 | Test procedure                                                                | 70 |

| 7.2.2.4 | Post-condition                                                                | 70 |

| 7.2.3   | 5 signals SPI - Slave behaviour during data transfer initiation by the slave  | 70 |

| 7.2.3.1 | Test purpose                                                                  | 70 |

| 7.2.3.2 | Initial conditions                                                            | 71 |

| 7.2.3.3 | Test procedure                                                                | 71 |

| 7.2.3.4 | Post-condition                                                                | 71 |

| 7.3     | MAC Layer - 4 signals SPI - SPI Master testing                                | 71 |

| 7.3.1   | 4 signals SPI - Master behaviour during initial data transfer initiation      | 71 |

| 7.3.1.1 | Test purpose                                                                  | 71 |

| 7.3.1.2 | Initial conditions                                                            | 71 |

| 7.3.1.3 | Test procedure                                                                | 72 |

| 7.3.1.4 | Post-condition                                                                | 72 |

| 7.3.2   | 4 signal SPI - Master behaviour during data transfer initiation               | 72 |

| 7.3.2.1 | Test purpose                                                                  | 72 |

| 7.3.2.2 | Initial conditions                                                            |    |

| 7.3.2.3 | Test procedure                                                                | 73 |

| 7.3.2.4 | Post-condition                                                                |    |

| 7.3.3   | 4 signal SPI - Master behaviour during simultaneous data transfer initiation  | 74 |

| 7.3.3.1 | Test purpose                                                                  |    |

| 7.3.3.2 | Initial conditions                                                            |    |

| 7.3.3.3 | Test procedure                                                                | 74 |

| 7.3.3.4 | Post-condition                                                                |    |

| 7.3.4   | 4 signal SPI - Master behaviour during data flow control                      | 74 |

| 7.3.4.1 | Test purpose                                                                  |    |

| 7.3.4.2 | Initial conditions                                                            | 74 |

| 7.3.4.3 | Test procedure                                                                | 75 |

| 7.3.4.4 | Post-condition                                                                | 75 |

| 7.3.5   | 4 signal SPI - MAC deactivation                                               |    |

| 7.3.5.1 | Test purpose                                                                  | 75 |

| 7.3.5.2 | Initial conditions                                                            | 75 |

| 7.3.5.3 | Test procedure                                                                | 75 |

| 7.3.5.4 | Post-condition                                                                |    |

| 7.4     | MAC Layer - 4 signals SPI - SPI Slave testing                                 |    |

| 7.4.1   | 4 signal SPI - Slave behaviour during data transfer initiation                | 76 |

| 7.4.1.1 | Test purpose                                                                  |    |

| 7.4.1.2 | Initial conditions                                                            | 76 |

| 7.4.1.3 | Test procedure                                                                | 76 |

| 7.4.1.4 | Post-condition                                                                | 76 |

| 7.4.2   | 4 signal SPI - Slave behaviour during simultaneous data transfer initiation   |    |

| 7.4.2.1 | Test purpose                                                                  |    |

| 7.4.2.2 | Initial conditions                                                            |    |

| 7.4.2.3 | Test procedure                                                                |    |

| 7.4.2.4 | Post-condition                                                                | 77 |

| 8       | Test cases for data link layer- Link layer                                     | 78 |

|---------|--------------------------------------------------------------------------------|----|

| 8.1     | Link layer - SPI Master testing                                                | 78 |

| 8.1.1   | Link layer - Master frame generation                                           | 78 |

| 8.1.1.1 | Test purpose                                                                   | 78 |

| 8.1.1.2 | Initial conditions                                                             | 78 |

| 8.1.1.3 | Test procedure                                                                 | 78 |

| 8.1.1.4 | Post Condition                                                                 | 79 |

| 8.1.2   | Link layer - Master frame generation - SPI access longer than frame            | 79 |

| 8.1.2.1 |                                                                                |    |

| 8.1.2.2 |                                                                                | 79 |

| 8.1.2.3 | Test procedure                                                                 | 80 |

| 8.1.2.4 | •                                                                              |    |

| 8.1.3   | Slave frame retrieval by Master                                                |    |

| 8.1.3.1 |                                                                                |    |

| 8.1.3.2 |                                                                                |    |

| 8.1.3.3 |                                                                                |    |

| 8.1.3.4 | 1                                                                              |    |

| 8.1.4   | Bytes set to 'FF' in second SPI access                                         |    |

| 8.2     | Link layer - SPI Slave testing                                                 |    |

| 8.2.1   | Slave frame generation - SPI access longer than frame                          |    |

| 8.2.1.1 | · · · · · · · · · · · · · · · · · · ·                                          |    |

| 8.2.1.2 | 1                                                                              |    |

| 8.2.1.3 |                                                                                |    |

| 8.2.1.4 | 1                                                                              |    |

| 8.2.1.4 | Slave frame retrieval by SPI Master                                            |    |

| 8.2.2.1 |                                                                                |    |

| 8.2.2.2 |                                                                                |    |

| 8.2.2.3 |                                                                                |    |

| 8.2.2.4 | 1                                                                              |    |

| 8.3     | Link layer data transfer cases - SPI Master testing                            |    |

|         |                                                                                |    |

| 8.3.1   | Case 2 - Slave MAC access request, retrieve the slave frame                    |    |

| 8.3.1.1 | T T                                                                            |    |

| 8.3.1.2 |                                                                                |    |

| 8.3.1.3 | 1                                                                              |    |

| 8.3.1.4 |                                                                                |    |

| 8.3.2   | Case 3 - Slave frame transferred in a single access, NSD attached              |    |

| 8.3.2.1 | 1 1                                                                            |    |

| 8.3.2.2 |                                                                                |    |

| 8.3.2.3 | 1                                                                              |    |

| 8.3.2.4 |                                                                                |    |

| 8.3.3   | Case 4 - Slave MAC access request, frame partially retrieved                   |    |

| 8.3.3.1 | 1 1                                                                            |    |

| 8.3.3.2 |                                                                                |    |

| 8.3.3.3 | 1                                                                              |    |

| 8.4     | Link layer data transfer cases - SPI Slave testing                             |    |

| 8.4.1   | Case 1 - Master sends the frame, no data from the slave                        |    |

| 8.4.1.1 | T T                                                                            |    |

| 8.4.1.2 |                                                                                |    |

| 8.4.1.3 | 1                                                                              |    |

| 8.4.1.4 |                                                                                |    |

| 8.4.2   | Case 5 - Simultaneous MAC phase initiation, remaining bytes of the slave frame | 85 |

| 8.4.2.1 | · · · · · · · · · · · · · · · · · · ·                                          |    |

| 8.4.2.2 |                                                                                |    |

| 8.4.2.3 |                                                                                |    |

| 8.4.3   | Case 6 - Simultaneous MAC phase initiation, short slave frame                  |    |

| 8.4.3.1 | •                                                                              |    |

| 8.4.3.2 |                                                                                |    |

| 8.4.3.3 |                                                                                |    |

| 8.4.4   | Case 7 - Simultaneous MAC phase initiation, single access                      |    |

| 8.4.4.1 |                                                                                |    |

| 8.4.4.2 | 1 1                                                                            |    |

| 8.4.4.3 |                                                                                |    |

|         |                                                                                |    |

| 86                                                                                                 |

|----------------------------------------------------------------------------------------------------|

| 80                                                                                                 |

|                                                                                                    |

|                                                                                                    |

| 86                                                                                                 |

| 86                                                                                                 |

|                                                                                                    |

| 8′                                                                                                 |

| 87                                                                                                 |

| 87                                                                                                 |

| 87                                                                                                 |

| 8                                                                                                  |

| 8′                                                                                                 |

| 8′                                                                                                 |

| 8′                                                                                                 |

| 88                                                                                                 |

| 88                                                                                                 |

| 88                                                                                                 |

|                                                                                                    |

| 88                                                                                                 |

| 88                                                                                                 |

| 88                                                                                                 |

| 88                                                                                                 |

| 88                                                                                                 |

| 88                                                                                                 |

| 89                                                                                                 |

| 89                                                                                                 |

| 89                                                                                                 |

| 89                                                                                                 |

| 89                                                                                                 |

| 90                                                                                                 |

|                                                                                                    |

| O/                                                                                                 |

| 90                                                                                                 |

| 90                                                                                                 |

| 90<br>90                                                                                           |

| 90<br>90<br>90                                                                                     |

| 90<br>90<br>90                                                                                     |

|                                                                                                    |

|                                                                                                    |

|                                                                                                    |

|                                                                                                    |

|                                                                                                    |

|                                                                                                    |

| 90<br>90<br>90<br>90<br>90<br>91<br>91<br>92<br>92                                                 |

| 90<br>90<br>90<br>90<br>90<br>90<br>90<br>90<br>90<br>90<br>90                                     |

| 90<br>90<br>90<br>90<br>90<br>91<br>91<br>92<br>92                                                 |

| 90<br>90<br>90<br>90<br>90<br>91<br>92<br>92<br>92                                                 |

| 90<br>90<br>90<br>90<br>90<br>90<br>90<br>90<br>90<br>90<br>90<br>90<br>90<br>9                    |

| 90<br>90<br>90<br>90<br>90<br>90<br>90<br>90<br>90<br>92<br>92<br>92                               |

| 90<br>90<br>90<br>90<br>90<br>91<br>92<br>92<br>92<br>92<br>92                                     |

| 90<br>90<br>90<br>90<br>90<br>91<br>92<br>92<br>92<br>92<br>92<br>92                               |

| 90<br>90<br>90<br>90<br>90<br>91<br>92<br>92<br>92<br>92<br>92<br>92<br>92                         |

| 90<br>90<br>90<br>90<br>90<br>91<br>92<br>92<br>92<br>92<br>92<br>92<br>92<br>92                   |

| 90<br>90<br>90<br>90<br>90<br>90<br>90<br>90<br>90<br>92<br>92<br>92<br>92<br>92<br>92<br>92       |

| 90<br>90<br>90<br>90<br>90<br>90<br>90<br>90<br>90<br>90                                           |

| 90<br>90<br>90<br>90<br>90<br>90<br>90<br>90<br>90<br>92<br>92<br>92<br>92<br>92<br>92<br>92       |

| 90<br>90<br>90<br>90<br>90<br>90<br>90<br>90<br>90<br>90                                           |

| 90<br>90<br>90<br>90<br>90<br>90<br>91<br>92<br>92<br>92<br>92<br>92<br>92<br>92<br>92<br>92<br>92 |

| 90<br>90<br>90<br>90<br>90<br>91<br>92<br>92<br>92<br>92<br>92<br>92<br>92<br>92<br>92<br>92       |

| 90<br>90<br>90<br>90<br>90<br>91<br>92<br>92<br>92<br>92<br>92<br>92<br>92<br>92<br>92<br>92       |

| 90<br>90<br>90<br>90<br>90<br>91<br>92<br>92<br>92<br>92<br>92<br>92<br>92<br>92<br>92<br>92       |

| 90<br>90<br>90<br>90<br>90<br>91<br>92<br>92<br>92<br>92<br>92<br>92<br>92<br>92<br>92<br>92       |

|                                                                                                    |

| 12.3.1.1             | Test purpose                                                                       | 93  |

|----------------------|------------------------------------------------------------------------------------|-----|

| 12.3.1.2             | Initial conditions                                                                 | 93  |

| 12.3.1.3             | Test procedure                                                                     | 93  |

| 12.3.2               | Link establishment and connection time out                                         |     |

| 12.3.2.1             | Test purpose                                                                       |     |

| 12.3.2.2             |                                                                                    |     |

| 12.3.2.3             |                                                                                    |     |

| 12.3.3               | Requesting unsupported window size and/or SREJ support - link establishment by SUT |     |

| 12.3.3.1             |                                                                                    |     |

| 12.3.3.1             | <u> </u>                                                                           |     |

| 12.3.3.2<br>12.3.3.3 |                                                                                    |     |

| 12.3.3.3<br>12.3.4   |                                                                                    |     |

|                      | Discard buffered frames on link re-establishment                                   |     |

| 12.3.4.1             | · · · · · · · · · · · · · · · · · ·                                                |     |

| 12.3.4.2             |                                                                                    |     |

| 12.3.4.3             | r                                                                                  |     |

| 12.4                 | Data flow                                                                          |     |

| 12.4.1               | I-frame transmission                                                               |     |

| 12.4.1.1             | · · · · · · · · · · · · · · · · · ·                                                |     |

| 12.4.1.2             |                                                                                    |     |

| 12.4.1.3             | r                                                                                  |     |

| 12.4.2               | I-frame reception - single I-Frame reception                                       |     |

| 12.4.2.1             | 1 1                                                                                |     |

| 12.4.2.2             | Initial conditions                                                                 | 96  |

| 12.4.2.3             | Test procedure                                                                     | 97  |

| 12.4.3               | I-frame reception - multiple I-Frame reception                                     | 97  |

| 12.4.3.1             | Test purpose                                                                       | 97  |

| 12.4.3.2             | Initial conditions                                                                 | 97  |

| 12.4.3.3             |                                                                                    |     |

| 12.5                 | Reject (go N back)                                                                 |     |

| 12.5.1               | REJ transmission - multiple I-frames received                                      |     |

| 12.5.1.1             | <u> </u>                                                                           |     |

| 12.5.1.2             | 1 1                                                                                |     |

| 12.5.1.3             |                                                                                    |     |

| 12.5.2               | REJ reception                                                                      |     |

| 12.5.2.1             | •                                                                                  |     |

| 12.5.2.2             | • •                                                                                |     |

| 12.5.2.3             |                                                                                    |     |

| 12.5.2.5<br>12.6     | Last Frame Loss                                                                    |     |

| 12.6.1               | Retransmission of multiple frames                                                  |     |

| 12.6.1<br>12.6.1.1   |                                                                                    |     |

| 12.6.1.1<br>12.6.1.2 |                                                                                    |     |

|                      |                                                                                    |     |

| 12.6.1.3             | 1                                                                                  |     |

| 12.7                 | Receive and not ready                                                              |     |

| 12.7.1               | RNR reception                                                                      |     |

| 12.7.1.1             | T T                                                                                |     |

| 12.7.1.2             |                                                                                    |     |

| 12.7.1.3             | r                                                                                  |     |

| 12.7.2               | Empty I-frame transmission                                                         |     |

| 12.7.2.1             | 1 1                                                                                |     |

| 12.7.2.2             |                                                                                    |     |

| 12.7.2.3             | F                                                                                  |     |

| 12.8                 | Selective reject                                                                   |     |

| 12.8.1               | SREJ transmission                                                                  | 100 |

| 12.8.1.1             | Test purpose                                                                       | 100 |

| 12.8.1.2             | Initial conditions                                                                 | 100 |

| 12.8.1.3             |                                                                                    |     |

| 12.8.2               | SREJ reception                                                                     |     |

| 12.8.2.1             |                                                                                    |     |

| 12.8.2.2             | 1 1                                                                                |     |

| 12.8.2.3             |                                                                                    |     |

|                      | •                                                                                  |     |

| 13 T                 | Test cases for power management                                                    | 102 |

| 13.1             | Power management - SPI Master testing                                 |     |

|------------------|-----------------------------------------------------------------------|-----|

| 13.1.1           | 211 Mageer entering power saving mode                                 |     |

| 13.1.1           | 1 1                                                                   |     |

| 13.1.1           |                                                                       |     |

| 13.1.1           | I                                                                     |     |

| 13.1.2           |                                                                       |     |

| 13.1.2           | · · · · · · · · · · · · · · · · · · ·                                 |     |

| 13.1.2           |                                                                       |     |

| 13.1.2           | r                                                                     |     |

| 13.2             | Power management - SPI Slave testing                                  |     |

| 13.2.1<br>13.2.1 | 8 F 8                                                                 |     |

| 13.2.1           | · · · · · · · · · · · · · · · · · · ·                                 |     |

| 13.2.1           |                                                                       |     |

| 13.2.1           |                                                                       |     |

| 13.2.2           | · · ·                                                                 |     |

| 13.2.2           | 1 1                                                                   |     |

| 13.2.2           |                                                                       |     |

|                  | 1                                                                     |     |

| Anne             | ex A (normative): SPI Test tool functional requirements               | 108 |

| A.1              | General requirements                                                  | 108 |

| A.1.0            | Introduction                                                          | 108 |

| A.1.1            | VDD, VSS                                                              | 108 |

| A.1.1.           | .1 Default measurement uncertainties                                  | 108 |

| A.2              | 5 signal SPI                                                          | 108 |

| A.2.1            | · ·                                                                   |     |

| A.2.1.           |                                                                       |     |

| A.2.1.           | $oldsymbol{c}$                                                        |     |

| A.2.1.           |                                                                       |     |

| A.2.1.           | <del>-</del>                                                          |     |

| A.2.1.           | <del>-</del>                                                          |     |

| A.2.2            | <del>-</del>                                                          |     |

| A.2.2.           |                                                                       |     |

| A.2.3            | <u> </u>                                                              |     |

| A.2.3.           | .1 Default measurement/setting uncertainties                          | 109 |

| A.3              | SPI bus with 4 signals                                                | 109 |

| Δ Δ              | Endpoints                                                             | 110 |

|                  | 1                                                                     | -   |

| Anne             | ex B (normative): Standard frames                                     | 111 |

| B.1              | Master frames                                                         | 111 |

| B.2              | Slave frames                                                          | 113 |

| B.3              | Standard data                                                         | 116 |

|                  |                                                                       |     |

| Anne             | ex C (normative): Definition of procedures used in test sequences     | 117 |

| C.1              | Definition of procedures used with a 5 signals SPI                    | 117 |

| C.1.1            | MAC activation                                                        | 117 |

| C.1.2            | MAC deactivation                                                      | 117 |

| C.1.3            | Initiation of the data transfer from the master                       | 117 |

| C.1.4            |                                                                       |     |

| C.1.5            | Simultaneous initiation of a data transfer from both master and slave | 118 |

| C.2              | Definition of procedures used with a 4 signals SPI                    | 110 |

| C.2.1            |                                                                       |     |

| C.2.1            |                                                                       |     |

| C.2.2            |                                                                       |     |

| C.2.4            |                                                                       |     |

| C 2 5            |                                                                       |     |

| C.2.6    | Slave driven flow con | trol                                   | 119  |

|----------|-----------------------|----------------------------------------|------|

| Annex I  | ) (informative):      | Change History                         | .121 |

| Annex E  | E (informative):      | Core specification version information | .122 |

| History. |                       |                                        | .123 |

## Intellectual Property Rights

#### **Essential patents**

IPRs essential or potentially essential to normative deliverables may have been declared to ETSI. The declarations pertaining to these essential IPRs, if any, are publicly available for **ETSI members and non-members**, and can be found in ETSI SR 000 314: "Intellectual Property Rights (IPRs); Essential, or potentially Essential, IPRs notified to ETSI in respect of ETSI standards", which is available from the ETSI Secretariat. Latest updates are available on the ETSI Web server (https://ipr.etsi.org/).

Pursuant to the ETSI Directives including the ETSI IPR Policy, no investigation regarding the essentiality of IPRs, including IPR searches, has been carried out by ETSI. No guarantee can be given as to the existence of other IPRs not referenced in ETSI SR 000 314 (or the updates on the ETSI Web server) which are, or may be, or may become, essential to the present document.

#### **Trademarks**

The present document may include trademarks and/or tradenames which are asserted and/or registered by their owners. ETSI claims no ownership of these except for any which are indicated as being the property of ETSI, and conveys no right to use or reproduce any trademark and/or tradename. Mention of those trademarks in the present document does not constitute an endorsement by ETSI of products, services or organizations associated with those trademarks.

**DECT**<sup>TM</sup>, **PLUGTESTS**<sup>TM</sup>, **UMTS**<sup>TM</sup> and the ETSI logo are trademarks of ETSI registered for the benefit of its Members. **3GPP**<sup>TM</sup> and **LTE**<sup>TM</sup> are trademarks of ETSI registered for the benefit of its Members and of the 3GPP Organizational Partners. **oneM2M**<sup>TM</sup> logo is a trademark of ETSI registered for the benefit of its Members and of the oneM2M Partners. **GSM**<sup>®</sup> and the GSM logo are trademarks registered and owned by the GSM Association.

## **Foreword**

This Technical Specification (TS) has been produced by ETSI Technical Committee Secure Element Technologies (SET).

The contents of the present document are subject to continuing work within TC SET and may change following formal TC SET approval. If TC SET modifies the contents of the present document, it will then be republished by ETSI with an identifying change of release date and an increase in version number as follows:

Version x.y.z

#### where:

- x the first digit:

- 0 early working draft;

- 1 presented to TC SET for information;

- 2 presented to TC SET for approval;

- 3 or greater indicates TC SET approved document under change control.

- Y the second digit is incremented for all changes of substance, i.e. technical enhancements, corrections, updates, etc.

- z the third digit is incremented when editorial only changes have been incorporated in the document.

## Modal verbs terminology

In the present document "shall", "shall not", "should", "should not", "may", "need not", "will", "will not", "can" and "cannot" are to be interpreted as described in clause 3.2 of the <a href="ETSI Drafting Rules">ETSI Drafting Rules</a> (Verbal forms for the expression of provisions).

"must" and "must not" are NOT allowed in ETSI deliverables except when used in direct citation.

## Introduction

The present document defines tests for the specific Serial Peripheral Interface (SPI) implementations defined in ETSI TS 103 713 [1] independently of the respective manufacturer.

## 1 Scope

The present document covers the minimum characteristics which are considered necessary for the Serial Peripheral Interface (SPI) communication of an SSP in order to provide compliance to ETSI TS 103 713 [1].

The present document specifies the test cases for:

- the physical layer (electrical characteristics);

- the MAC layer;

- the data link layer; and

- the SHDLC layer (as defined in ETSI TS 102 613 [5])

of the SPI.

Tests for the usage of an SPI different to what is defined in ETSI TS 103 713 [1] are out of scope of the present document.

## 2 References

#### 2.1 Normative references

References are either specific (identified by date of publication and/or edition number or version number) or non-specific. For specific references, only the cited version applies. For non-specific references, the latest version of the referenced document (including any amendments) applies.

• In the case of a reference to a TC SET document, a non-specific reference implicitly refers to the latest version of that document in the same Release as the present document.

Referenced documents which are not found to be publicly available in the expected location might be found at <a href="https://docbox.etsi.org/Reference">https://docbox.etsi.org/Reference</a>.

NOTE: While any hyperlinks included in this clause were valid at the time of publication, ETSI cannot guarantee their long term validity.

The following referenced documents are necessary for the application of the present document.

| [1] | ETSI TS 103 713: "Smart Secure Platform (SSP); SPI interface".                                                                                                       |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2] | ISO/IEC 9646-7: "Information technology Open Systems Interconnection - Conformance testing methodology and framework Part 7: Implementation Conformance Statements". |

| [3] | IEEE 1149.1 <sup>TM</sup> -2013: "IEEE Standard for Test Access Port and Boundary-Scan Architecture".                                                                |

| [4] | ETSI TS 103 666-1: "Smart Secure Platform (SSP); Part 1: General characteristics".                                                                                   |

| [5] | ETSI TS 102 613: "Smart Cards; UICC - Contactless Front-end (CLF) Interface; Physical and data link layer characteristics".                                          |

| [6] | ISO/IEC 13239: "Information technology - Telecommunications and information exchange between systems - High-level data link control (HDLC) procedures".              |

#### 2.2 Informative references

References are either specific (identified by date of publication and/or edition number or version number) or non-specific. For specific references, only the cited version applies. For non-specific references, the latest version of the referenced document (including any amendments) applies.

• In the case of a reference to a TC SET document, a non-specific reference implicitly refers to the latest version of that document in the same Release as the present document.

NOTE: While any hyperlinks included in this clause were valid at the time of publication, ETSI cannot guarantee their long-term validity.

The following referenced documents are not necessary for the application of the present document but they assist the user with regard to a particular subject area.

Not applicable.

## 3 Definition of terms, symbols, abbreviations and formats

#### 3.1 Terms

For the purposes of the present document, the terms given in ETSI TS 103 713 [1] and the following apply:

JTAG: Joint Test Action Group, synonym for IEEE 1149.1-2013 [3]

SPI Master: expression used to describe the Master entity connected to an SPI

NOTE: Descriptive text may use "master" or "SPI\_M" as synonyms.

SPI Slave: expression used to describe the Slave entity connected to an SPI

NOTE: Descriptive text may use "slave" or "SPI\_S" as synonyms.

**test case:** textual description of conditions, procedures and functions appropriate to verify specific conformance requirements

NOTE: The present document is not providing test cases as test scripts or part of an ATS. In general, a test case as defined here consists of initial conditions and a specific test case description.

test tool: test implementation fulfilling the requirements of test environment defined for the particular test case

NOTE: The present document uses "test tool" and "conformance test system" as synonyms.

## 3.2 Symbols

For the purposes of the present document, the symbols given in ETSI TS 103 713 [1] apply.

#### 3.3 Abbreviations

For the purposes of the present document, the abbreviations given in ETSI TS 103 713 [1] and the following apply:

ATS Abstract Test Suite

ICS Implementation Conformance Statement

PCB Printed Circuit Board

POT Power On Time

SPI\_M SPI Master

SPI S SPI Slave

SUT System Under Test

TT Test Tool

## 3.4 Formats

## 3.4.1 Format of the table of optional features

The columns in the optional features table, Table 4.1, have the following meaning:

| Column   | Meaning                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Item     | Item number, incrementing with each item added to the table                                                                                                                                                                                                                                                                                                                                                           |

| Option   | Description of the optional feature that might be supported by the implementation                                                                                                                                                                                                                                                                                                                                     |

| Status   | The status of the optional feature is described following notations defined in ISO/IEC 9646-7 [2]:  O optional - the feature may be supported or not (default value)  O.i qualified optional - for mutually exclusive or selectable options from a set. "i" is an integer which identifies a unique group of related optional items and the logic of their selection which is defined immediately following the table |

| Release  | Number of the version the feature was introduced in                                                                                                                                                                                                                                                                                                                                                                   |

| Support  | The column is blank in the pro forma and shall be filled in by the supplier of the implementation. The following common notations, defined in ISO/IEC 9646-7 [2], are used for the support column in Table 4.1:                                                                                                                                                                                                       |

|          | Y or y supported by the implementation                                                                                                                                                                                                                                                                                                                                                                                |

|          | N or n not supported by the implementation                                                                                                                                                                                                                                                                                                                                                                            |

|          | N/A, n/a or - no answer required (allowed only if the status is N/A, directly or after evaluation of a conditional status)                                                                                                                                                                                                                                                                                            |

| Mnemonic | The "Mnemonic" column contains mnemonic identifiers for each optional feature                                                                                                                                                                                                                                                                                                                                         |

## 3.4.2 Format of the applicability table

The columns in the applicability tables, Table 4.2a, Table 4.3a and Table 4.4, have the following meaning:

| Column       | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Test/Seq.    | A reference to the test case number(s) detailed in the present document and required to validate the implementation of the corresponding item in the "Description" column.  Tests consisting of more than one logical part are split into sequences. The sequence number is given after the slash.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Description  | A short non-exhaustive description of the test purpose is given here. In general, the description text used will equal the test case name used in the present document.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Release      | Number of the version the tested feature was introduced in.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Rel- <x></x> | For a given Release, the corresponding "Rel- <x>" column lists the tests required for the SPI to be declared compliant to this Release.  Each entry shows the status following notations defined in ISO/IEC 9646-7 [2]:  M mandatory - the capability is required to be supported.  O optional - the capability may be supported or not.  N/A not applicable - in the given context, it is impossible to use the capability.  X prohibited (excluded) - there is a requirement not to use this capability in the given context.  Oi qualified optional - for mutually exclusive or selectable options from a set. "i" is an integer which identifies a unique group of related optional items and the logic of their selection which is defined immediately following the table.  Ci conditional - the requirement on the capability ("M", "O", "X" or "N/A") depends on the support of other optional or conditional items. "i" is an integer identifying an unique conditional status expression which is defined immediately following the table. For nested conditional expressions, the syntax "IF THEN (IF THEN ELSE) ELSE" shall be used to avoid ambiguities.</x> |

| Support      | Is blank in the pro forma and is to be completed by the manufacturer in respect of each particular requirement to indicate the choices, which have been made in the implementation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

## 3.4.3 Format of the conformance requirements tables

The columns in the requirement tables in clause 5 have the following meaning:

| Column      | Meaning                                                                                                 |

|-------------|---------------------------------------------------------------------------------------------------------|

| Req.ID      | This column shows the ordinal term assigned to a requirement identified in the referenced               |

|             | specification. The following syntax has been used to define the unique R(equirement) terms:             |

|             | R <n><xx><yy>_<zzz></zzz></yy></xx></n>                                                                 |

|             | n: Identification letter for the referenced specification                                               |

|             | Q: ETSI TS 103 713 [1]                                                                                  |