# ETSI TS 101 493-3 V1.1.1 (2000-09)

**Technical Specification**

Broadband Radio Access Networks (BRAN); HIPERLAN Type 2; Packet based convergence layer; Part 3: IEEE 1394 Service Specific Convergence Sublayer (SSCS)

Reference DTS/BRAN-0024004-3

Keywords access, broadband, radio, HIPERLAN

#### ETSI

#### 650 Route des Lucioles F-06921 Sophia Antipolis Cedex - FRANCE

Tel.: +33 4 92 94 42 00 Fax: +33 4 93 65 47 16

Siret N° 348 623 562 00017 - NAF 742 C Association à but non lucratif enregistrée à la Sous-Préfecture de Grasse (06) N° 7803/88

Important notice

Individual copies of the present document can be downloaded from: <u>http://www.etsi.org</u>

The present document may be made available in more than one electronic version or in print. In any case of existing or perceived difference in contents between such versions, the reference version is the Portable Document Format (PDF). In case of dispute, the reference shall be the printing on ETSI printers of the PDF version kept on a specific network drive within ETSI Secretariat.

Users of the present document should be aware that the document may be subject to revision or change of status. Information on the current status of this and other ETSI documents is available at <a href="http://www.etsi.org/tb/status/">http://www.etsi.org/tb/status/</a>

If you find errors in the present document, send your comment to: editor@etsi.fr

#### **Copyright Notification**

No part may be reproduced except as authorized by written permission. The copyright and the foregoing restriction extend to reproduction in all media.

> © European Telecommunications Standards Institute 2000. All rights reserved.

# Contents

| Intelle        | ectual Property Rights                                                                       | 7  |

|----------------|----------------------------------------------------------------------------------------------|----|

| Forew          | /ord                                                                                         | 7  |

| 1              | Scope                                                                                        | 8  |

| 2              | References                                                                                   | 8  |

| 3              | Definitions, symbols and abbreviations                                                       | 8  |

| 3.1            | Definitions                                                                                  |    |

| 3.2            | Symbols                                                                                      | 10 |

| 3.3            | Abbreviations                                                                                |    |

| 4              | Overview                                                                                     | 11 |

| 4.1            | The 1394 SSCS                                                                                |    |

| 4.2            | HIPERLAN/2 Bus                                                                               |    |

| 4.3            | Numbering and coding conventions                                                             | 13 |

| 5              | User plane services                                                                          | 14 |

| 5.1            | General                                                                                      |    |

| 5.2            | Primitives (informative)                                                                     | 14 |

| 5.2.1          | Primitive types                                                                              | 14 |

| 5.2.2          | Parameter definitions                                                                        |    |

| 5.2.3          | Interface to the upper layer                                                                 |    |

| 5.2.3.1        |                                                                                              |    |

| 5.2.3.1        |                                                                                              |    |

| 5.2.3.1        |                                                                                              |    |

| 5.2.3.2        | · · · · · · · · · · · · · · · · · · ·                                                        |    |

| 5.2.3.2        |                                                                                              |    |

| 5.2.3.2        | ······································                                                       |    |

| 5.2.4          | Interface to the common part                                                                 |    |

| 5.3            | Clock synchronization service                                                                |    |

| 5.3.1          | General                                                                                      |    |

| 5.3.2          | SSCS PDU format                                                                              |    |

| 5.3.3          | Procedures.                                                                                  |    |

| 5.3.3.1        |                                                                                              |    |

| 5.3.3.2<br>5.4 | Procedure in a wireless cycle slave (WCS)<br>Asynchronous transaction data transport service |    |

| 5.4<br>5.4.1   | General                                                                                      |    |

| 5.4.2          | Asynchronous SSCS PDU coding                                                                 |    |

| 5.4.3          | Asynchronous packets management                                                              |    |

| 5.4.4          | Procedures.                                                                                  |    |

| 5.4.4.1        |                                                                                              |    |

| 5.4.4.2        |                                                                                              |    |

| 5.5            | Stream data transport service                                                                |    |

| 5.5.1          | Isochronous stream data transport service                                                    |    |

| 5.5.1.1        | •                                                                                            |    |

| 5.5.1.2        | Isochronous stream SSCS PDU coding                                                           |    |

| 5.5.1.3        | Procedure                                                                                    |    |

| 5.5.1.3        | Procedure in the sender                                                                      | 24 |

| 5.5.1.3        |                                                                                              |    |

| 5.5.2          | Asynchronous stream data transport service                                                   |    |

| 5.5.2.1        |                                                                                              |    |

| 5.5.2.2        |                                                                                              |    |

| 5.5.2.3        |                                                                                              |    |

| 5.5.2.3        |                                                                                              |    |

| 5.5.2.3        | Procedure in the receiver                                                                    |    |

| 6              | Control plane services                                                                       | 27 |

| 6.1            | General                                                                                      |    |

|                |                                                                                              |    |

| 6.2                | Primitives (informative)                                        |    |

|--------------------|-----------------------------------------------------------------|----|

| 6.2.1              | CL_CONTROL {request, confirm}                                   |    |

| 6.2.2              | CL_SELF_ID {indication}                                         | 29 |

| 6.3                | Association - Initialization                                    |    |

| 6.4                | Bus reset service                                               |    |

| 6.4.1              | General                                                         |    |

| 6.4.2              | Procedures                                                      |    |

| 6.4.2.1            | CC or WT initiated bus reset                                    |    |

| 6.4.2.2            | Bus reset worst case duration                                   |    |

| 6.4.2.3            | Procedure in the CC side                                        |    |

| 6.4.2.4            | Procedure in the WT side                                        |    |

| 6.4.3              | Assignment of physical_IDs                                      |    |

| 6.5                | Clock information connection control                            |    |

| 6.5.1              | General                                                         |    |

| 6.5.2              | Wireless cycle master procedure                                 |    |

| 6.5.2.1            | Wireless cycle master election                                  |    |

| 6.5.2.2            | Wireless cycle master operation                                 |    |

| 6.5.3              | Wireless cycle slave procedure                                  |    |

| 6.5.4              |                                                                 |    |

|                    | CC specific procedure                                           |    |

| 6.6                | CL responsibility handover                                      |    |

| 6.7                | HL2 Address Resolution service (HARP)                           |    |

| 6.7.1              | General                                                         |    |

| 6.7.2              | Procedures                                                      |    |

| 6.7.2.1            | Procedure in the sender                                         |    |

| 6.7.2.2            | Procedure in the receiver                                       |    |

| 6.8                | Asynchronous transaction connection control service             |    |

| 6.8.1              | Asynchronous transaction mapping to a DLC connection            |    |

| 6.8.1.1            | General                                                         |    |

| 6.8.1.2            | Procedures                                                      |    |

| 6.8.2              | Clean closing service                                           |    |

| 6.8.2.1            | General                                                         |    |

| 6.8.2.2            | Clean closing SSCS PDU format                                   |    |

| 6.8.2.3            | Procedures                                                      |    |

| 6.8.2.3.1          | Procedure at the initiating side                                |    |

| 6.8.2.3.2          |                                                                 |    |

| 6.9                | Isochronous stream connection control service                   |    |

| 6.9.1              | General                                                         |    |

| 6.9.2              | SSCS procedure                                                  |    |

| 6.9.2.1            | General                                                         |    |

| 6.9.2.1.1          |                                                                 |    |

| 6.9.2.1.2          |                                                                 |    |

| 6.9.2.1.3          |                                                                 |    |

| 6.9.2.1.4          |                                                                 |    |

| 6.9.2.1.5          |                                                                 |    |

| 6.9.2.2            | Procedure at the talker side                                    |    |

| 6.9.2.2<br>6.9.2.3 | Procedure at the listener side                                  |    |

| 6.9.2.3            | Procedure at the IRM side                                       |    |

|                    | Asynchronous streams connection control service                 |    |

| 6.10               |                                                                 |    |

| 6.10.1             | IRM and PCR functions                                           |    |

| 6.10.2             | Asynchronous stream relaying                                    |    |

| 6.10.2.1           |                                                                 |    |

| 6.10.2.2           |                                                                 |    |

| 6.10.2.2           |                                                                 |    |

| 6.10.2.2           | .2 Procedure in the CC side                                     | 46 |

| 7 0                | Convergence layer specific parameters                           | 16 |

| 7.1                | Convergence layer identifier                                    |    |

| 7.1                | Convergence layer version                                       |    |

|                    |                                                                 |    |

| 7.3                | Maximum transmission unit<br>Information elements for 1394 SSCS |    |

| 7.4                |                                                                 |    |

| 7.4.1              | Information element format                                      |    |

| 7.4.2              | Information element type coding                                 | 47 |

| 7.4.3 HARP_REQUEST information element                                                            |            |

|---------------------------------------------------------------------------------------------------|------------|

| 7.4.4 HARP_RESPONSE information element                                                           |            |

| 7.4.5 EUI_64 information element                                                                  |            |

| <ul><li>7.4.6 CHANNEL information element</li><li>7.4.7 BUS_SUSPEND information element</li></ul> |            |

| 7.4.7 BUS_SUSPEND information element                                                             |            |

| 7.4.9 BUS_RESET information element                                                               |            |

| 7.4.10 TRANSACTION_INDICATOR information element                                                  |            |

| Annex A (normative): HIPERLAN/2 CSRs                                                              | 51         |

| A.1 CSR registers                                                                                 | 51         |

| A.1.1 Standard CSR registers                                                                      |            |

| A.1.2 Unimplemented wired-1394 registers                                                          |            |

| A.1.3 INTERRUPT_TARGET register                                                                   |            |

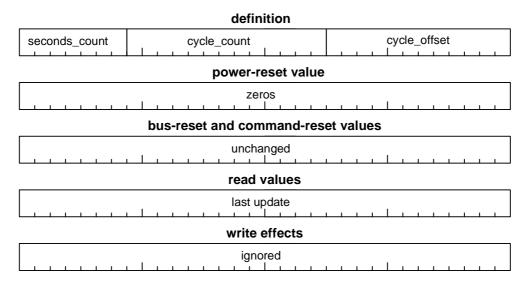

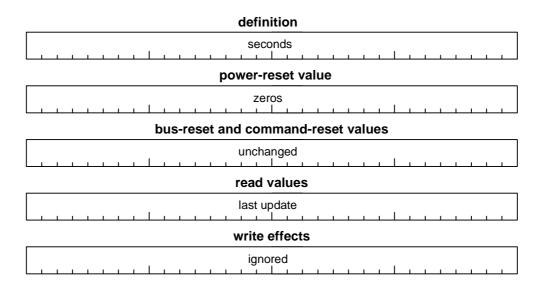

| A.1.4 CYCLE_TIME register                                                                         |            |

| A.1.5 BUS_TIME register                                                                           |            |

| <ul><li>A.1.6 LOCAL_CYCLES register</li><li>A.1.7 LOCAL_SECONDS register</li></ul>                |            |

| A.1.8 SPLIT_TIMEOUT register                                                                      |            |

| -                                                                                                 |            |

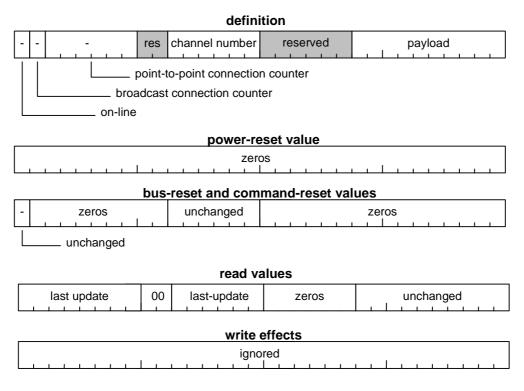

| A.2 PCRs                                                                                          |            |

| A.2.1 oPCR format<br>A.2.2 iPCR format                                                            |            |

| A.2.2 iPCR format<br>A.2.3 PCR error codes                                                        |            |

|                                                                                                   |            |

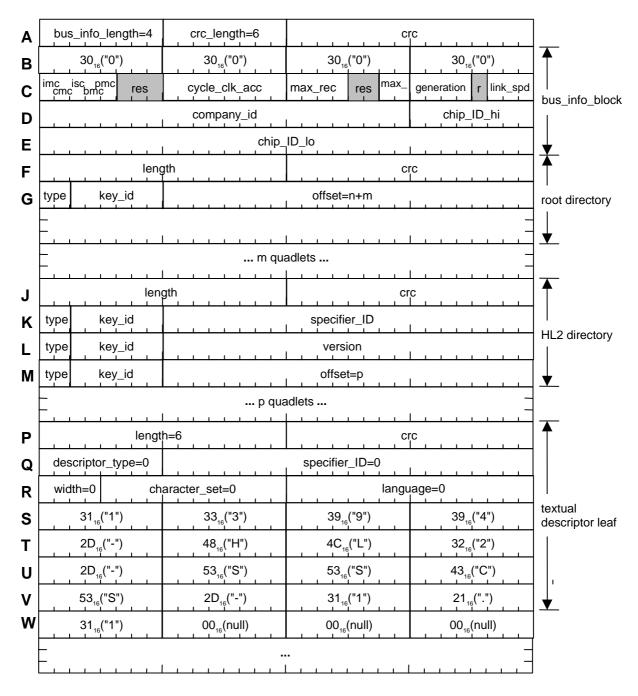

| A.3 ROM information                                                                               |            |

| A.4 Locked messages                                                                               | 60         |

| A.4.1 Locked message formats                                                                      |            |

| A.4.2 ALLOCATE_SOME                                                                               |            |

| A.4.2.1 ALLOCATE_SOME request                                                                     |            |

| A.4.2.2 ALLOCATE_SOME response<br>A.4.3 MODIFY_BANDWIDTH                                          |            |

| A.4.3.1 MODIFY_BANDWIDTH request                                                                  |            |

| A.4.3.2 MODIFY_BANDWIDTH response                                                                 |            |

| A.4.4 RECLAIM_THIS                                                                                |            |

| A.4.4.1 RECLAIM_THIS request                                                                      |            |

| A.4.4.2 RECLAIM_THIS response                                                                     |            |

| A.4.5 RELEASE_THIS<br>A.4.5.1 RELEASE_THIS request                                                |            |

| A.4.5.1 RELEASE_THIS request                                                                      |            |

| — <b>I</b>                                                                                        |            |

|                                                                                                   | s66        |

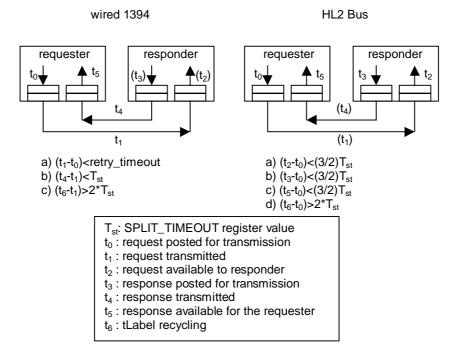

| B.1 Asynchronous subaction                                                                        |            |

| B.2 Isochronous streams                                                                           |            |

| B.3 Asynchronous streams                                                                          |            |

| Annex C (normative): Nonbridge upper layer                                                        | 68         |

| C.1 Primitives (informative)                                                                      |            |

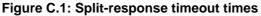

| C.2 Time stamps for split-response timeouts (normative)                                           |            |

| C.3 User plane                                                                                    | 60         |

| C.3.1 Isochronous stream transport service                                                        |            |

| C.3.1.1 HL2 Bus maximum transmission delay (informative)                                          |            |

| C.3.1.2 Relative CIP time stamps (normative)                                                      |            |

| C.3.2 Asynchronous transactions                                                                   |            |

| C.3.2.1 Subaction rt field (normative)<br>C.3.2.2 Available self-ID information (informative)     |            |

|                                                                                                   | 1 <i>2</i> |

6

# Intellectual Property Rights

IPRs essential or potentially essential to the present document may have been declared to ETSI. The information pertaining to these essential IPRs, if any, is publicly available for **ETSI members and non-members**, and can be found in ETSI SR 000 314: "Intellectual Property Rights (IPRs); Essential, or potentially Essential, IPRs notified to ETSI in respect of ETSI standards", which is available from the ETSI Secretariat. Latest updates are available on the ETSI Web server (http://www.etsi.org/ipr).

7

Pursuant to the ETSI IPR Policy, no investigation, including IPR searches, has been carried out by ETSI. No guarantee can be given as to the existence of other IPRs not referenced in ETSI SR 000 314 (or the updates on the ETSI Web server) which are, or may be, or may become, essential to the present document.

# Foreword

This Technical Specification (TS) has been produced by ETSI Project Broadband Radio Access Networks (BRAN).

The present document defines the functionality required for interworking HIgh PErformance Radio Local Area Network Type 2 (HIPERLAN/2) with IEEE 1394 [6]. Separate ETSI documents provide details on the system overview, data link control layer, radio link control sublayer, other convergence sublayers and conformance testing requirements for HIPERLAN/2.

The present document is Part 3 of a multi-part deliverable covering the Packet based Convergence Layer of HIPERLAN/2, as identified below:

Part 1: "Common Part";

Part 2: "Ethernet Service Specific Convergence Sublayer (SSCS)";

Part 3: "IEEE 1394 Service Specific Convergence Sublayer";

Part 4: "IEEE 1394 bridge layer".

Part 1, Common Part, describes the functionality for adapting variable length packets/frames to the fixed size used in the Data Link Control (DLC) layer. Further parts, each defining a Service Specific Convergence Sublayer (SSCS), describe the functionality required to support a certain protocol, e.g. IEEE 1394 [6] or Ethernet protocols. The SSCSs all use the services of the Common Part and the DLC [2]. It is envisioned that several, independent, service specific parts will be defined in the future as market requirements develop. As a result, further parts may be added in the future.

# 1 Scope

The present document is applicable to HIPERLAN/2 equipment supporting interworking with 1394 buses.

The present document only addresses the functionality required to transfer IEEE 1394 [6] traffic over the radio interface between HIPERLAN/2 devices. It does not address the requirements and technical characteristics for wired network interfaces at a HIPERLAN/2 device.

The present document uses the services provided by the Common Part of the Packet based Convergence Layer and by the Data Link Control layers of HIPERLAN/2.

The present document does not address the requirements and technical characteristics for type approval and conformance testing. These are covered in separate Technical Specifications.

# 2 References

The following documents contain provisions which, through reference in this text, constitute provisions of the present document.

- References are either specific (identified by date of publication, edition number, version number, etc.) or non-specific.

- For a specific reference, subsequent revisions do not apply.

- For a non-specific reference, the latest version applies.

- A non-specific reference to an ETS shall also be taken to refer to later versions published as an EN with the same number.

- [1] ETSI TS 101 493-1: "Broadband Radio Access Networks (BRAN); HIPERLAN 2; Packet based Convergence Layer; Part 1: Common Part".

- [2] ETSI TS 101 761-2: "Broadband Radio Access Networks (BRAN); HIPERLAN Type 2; Data Link Control (DLC) Layer; Part 2: Radio Link Control (RLC) sublayer".

- [3] ETSI TS 101 761-1: "Broadband Radio Access Networks (BRAN); HIPERLAN Type 2; Data Link Control (DLC) Layer; Part 1: Basic Data Transport Functions".

- [4] ETSI TS 101 764-4: "Broadband Radio Access Networks (BRAN); HIPERLAN Type 2; Data Link Control (DLC) Layer; Part 4: Extension for Home Environment".

- [5] IEC 61883 (1998): "Consumer audio/video equipment Digital interface".

- [6] IEEE Std 1394 (1995): "Standard for a High Performance Serial Bus".

- [7] IEEE Std 1394a (2000): "IEEE Standard for a High Performance Serial Bus Amendment 1".

# 3 Definitions, symbols and abbreviations

# 3.1 Definitions

For the purposes of the present document, the following terms and definitions apply:

1394 controller: 1394 application that establishes an isochronous connection on a Serial Bus.

1394 SSCS: abbreviation for IEEE 1394 SSCS, the contents of the present document.

**HL2 1394 bridge layeraccess point:** term access point used in the basic specifications is replaced by the term central controller throughout this document to reflect that in home environment multiple HL2 devices can act as the access point to a fixed network, whereas the whole HL2 network is still controlled by a single entity, the central controller.

**bridge:** pair of two closely coupled serial bus nodes, called portals, capable of connecting two buses in a Serial Bus net. The bridge selectively forwards asynchronous and isochronous packets according to route information contained within the portals.

bus\_ID: 10-bit number uniquely specifying a particular bus within a Serial Bus net.

**central controller (CC):** provides control functionality for the DLC layer equivalent to that of an access point as defined by HIPERLAN/2, but is not necessarily attached to a fixed network. The central controller functionality may be embedded in a wireless device.

**extended unique identifier (EUI-64):** 64-bit unique number identifiers derived from the IEEE/RAC-provided *company\_id* value These EUI-64 values are, by definition, unique among themselves.

**HIPERLAN/2:** HIgh PErformance Radio Local Area Network Type 2, a short-range wireless LAN providing broadband local access. Standardized by ETSI Project BRAN.

HL2 1394 bridge layer: refers to the HIPERLAN/2 IEEE 1394 bridge layer (see Bibliography).

HL2 Bus: protocols that provide 1394 asynchronous and isochronous services on a HL2 wireless network.

**information element:** message used to transfer convergence layer specific information and that is transferred transparently by RLC messages.

listener: device that can sink isochronous streams is called a listener.

**mac\_ID:** each WT is assigned a MAC ID that is unique for the AP by the AP RLC entity during association. The MAC ID is coded with 8 bits.

**mobile terminal:** term mobile terminal used in the basic specifications is replaced by the term wireless terminal throughout this document to reflect that in home environment not all HL2 terminals need to be mobile.

**node\_ID:** 16-bit address which distinguishes the node from other nodes in the system. The 10 most significant bits are the same for all nodes on the same bus; this is called the bus\_ID. The 6 least-significant bits are unique for each node on the same bus; this is called the physical\_ID.

octet: eight bits of data.

**overlaid connection:** IEC 61883 [5] specification defines this operation that allows adding additional listeners to an existing connection.

physical\_ID: 6-bit number uniquely specifying a particular node on a 1394 bus.

portal: node that connects a bridge to a Serial Bus.

protocol data unit (PDU): data unit exchanged between entities at the same ISO layer.

quadlet: four bytes, or 32 bits, of data.

**reserved codes:** set of values for a defined field that are not used within the present document, but are reserved for future revisions of the present document. A reserved code shall not be generated or, upon development of a future standard, may be used as specified by such a standard. The recipient of a *reserved* code shall check its value and shall reject code values that were not defined at the time of its inception.

**reserved fields:** set of bits not defined by the present document, but reserved for future revisions of the present document. A reserved field shall be zeroed or, upon development of a future standard, set to a value specified by such a standard. The recipient of a *reserved* field shall not check its value.

service data unit (SDU): data unit exchanged between adjacent ISO layers.

talker: device that can source isochronous streams is called a talker.

wired 1394: refers to a wired bus as specified in IEEE Std 1394-1995 as amended by IEEE Std 1394a-2000, and supplemented with IEC 61883 [5].

wireless bridge: bridge which a least one of its portals is wireless.

wireless cycle master: refers to the cycle master on the HL2 Bus.

**wireless node:** device that belongs to the HL2 Bus and that implements the 1394 SSCS without any bridging functions on top of it. A wireless node is identical to a wireless terminal. The term *wireless node* is used when describing HL2 Bus behaviour.

10

wireless portal: wireless node that implements the HL2 1394 bridge layer, in addition of the 1394 SSCS.

**wireless terminal (WT):** HL2 home device, which is not acting as a central controller for a subnet. A wireless terminal is identical to a wireless node which is not acting as a central controller. The term *wireless terminal* is used when describing WT behaviour compared to CC behaviour.

# 3.2 Symbols

For the purposes of the present document, the following symbols apply:

0516Hexadecimal notation0000 01012Binary notation

### 3.3 Abbreviations

For the purposes of the present document, the following abbreviations apply:

| AP      | Access Point                                      |

|---------|---------------------------------------------------|

| BRAN    | Broadband Radio Access Networks (Project)         |

| CC      | Central Controller                                |

| CL      | Convergence Layer                                 |

| CPCS    | Common Part Convergence Sublayer                  |

| C-SAP   | Control Service Access Point                      |

| CSR     | Control and Status Register                       |

| DLC     | Data Link Control                                 |

| DUC     | DLC User Connection                               |

| ETSI    | European Telecommunications Standards Institute   |

| EUI-64  | Extended Unique Identifier                        |

| HARP    | HIPERLAN/2 Address Resolution Protocol            |

| HL2     | HIPERLAN/2                                        |

| IE      | Information Element                               |

| IEEE    | Institute of Electrical and Electronics Engineers |

| iPCR    | input Plug Control Register                       |

| IRM     | Isochronous Resource Manager                      |

| LAN     | Local Area Network                                |

| LSB     | Least Significant Bit                             |

| MAC     | Medium Access Control                             |

| MSB     | Most Significant Bit                              |

| oPCR    | output Plug Control Register                      |

| PCR     | Plug Control Register                             |

| PDU     | Protocol Data Unit                                |

| RLC     | Radio Link Control                                |

| SAP     | Service Access Point                              |

| SDU     | Service Data Unit                                 |

| Self_ID | Self IDentify                                     |

| SSCS    | Service Specific Convergence Sublayer             |

| WCM     | Wireless Cycle Master                             |

| WCS     | Wireless Cycle Slave                              |

| WT      | Wireless Terminal                                 |

# 4 Overview

# 4.1 The 1394 SSCS

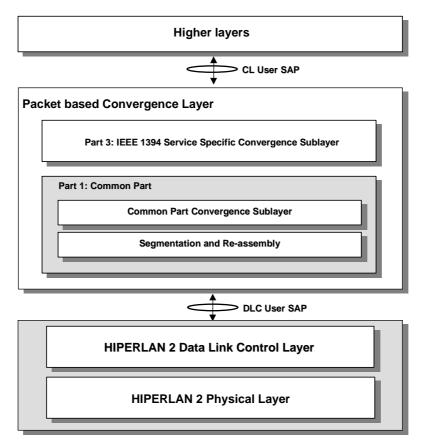

The IEEE 1394 Service Specific Convergence Sublayer (SSCS) is a part of the Packet based Convergence Layer and it resides on top of the Common Part and the DLC, as shown in Figure 1. The support of the DLC extensions for the home environment, as described in [4], is mandated by the 1394 SSCS.

The aim of this sublayer is to mimic the functions provided by IEEE 1394 [6] link layer. Bridge functions are out of the scope of this document. They are defined in the HIPERLAN/2 1394 bridge layer (see Bibliography). The HIPERLAN/2 protocol stack defined in the present document replaces the wired 1394 physical and link layer. The services and primitives provided by the 1394 SSCS are a subset of those provided by the wired 1394 physical and link stacks. Basic wired 1394 services and primitives are provided by the 1394 SSCS. Some of the wired 1394 services and primitives are related to the cable environment and the corresponding physical layer. They are not relevant for the HIPERLAN/2 environment, and thus not provided by the 1394 SSCS.

The 1394 SSCS allows the transportation of wired-1394 asynchronous and isochronous packets over HIPERLAN/2. It also provides 1394 clock propagation over HIPERLAN/2.

Figure 1: IEEE 1394 [6] packet based convergence layer

The 1394 SSCS consists of a user plane and a control plane.

The user plane, described in clause 5, provides services to the higher layer via the CL-Service Access Point (SAP) and uses the services of the Common Part of the Packet based Convergence Layer [1].

The control plane, described in clause 6, interacts with the DLC control plane, i.e. the RLC sublayer, via the DLC Control SAP. It also uses the services of the Common Part of the Packet based Convergence Layer [1]. The DLC Control SAP is defined in [2] and [4].

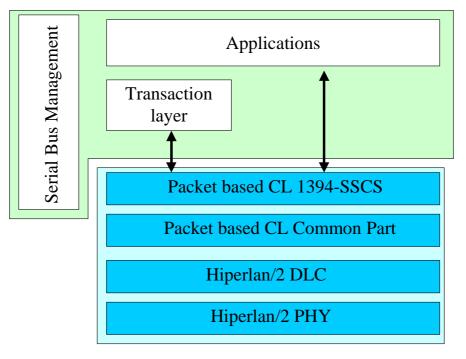

The 1394 SSCS may be present in two types of devices:

- Wireless 1394 bridge devices: these devices contain bridge functions to allow the connection of a HIPERLAN/2 network to a wired-1394 bus or to another wireless network. A wireless bridge device has at least one of its portals that belong to the HIPERLAN/2 network. The wireless portal shall implement both the 1394 SSCS and the HIPERLAN/2 1394 bridge layer.

- Wireless 1394 devices: these devices implement only the 1394 SSCS, and thus they do not provide any bridge functions (see in Figure 2).

Figure 2: Protocol stack of a non-bridge wireless 1394 device

# 4.2 HIPERLAN/2 Bus

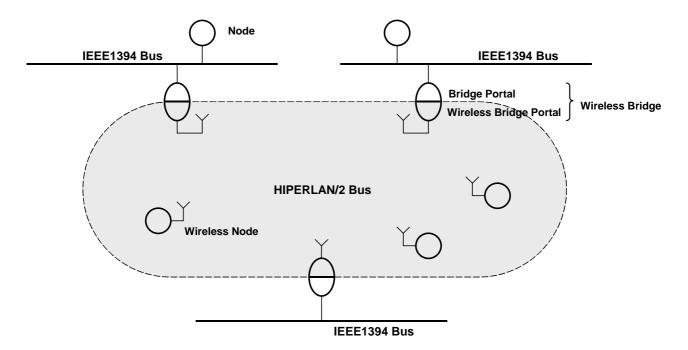

The net topology when applied to HIPERLAN/2 is shown in Figure 3. The HIPERLAN/2 network appears as a wired-1394 bus for all the attached nodes. This bus is called a HIPERLAN/2 Bus, which is often abbreviated as HL2 Bus. Regarding the HL2 Bus, all wireless nodes are peers (there is no particular base station). Regarding the HIPERLAN/2 network there is however one device in the cell which acts as the CC.

Figure 3: HL2 Bus connecting bridge and non-bridge 1394 devices

# 4.3 Numbering and coding conventions

Information elements and PDU are transferred between the 1394 SSCS and the underlying protocol layers in units of octets, in ascending numerical octet order (i.e. octet 1, 2, ..., n-1, n), see Figure 4.

|           | MSB |   |   | Bi | its |   |   | LSB |

|-----------|-----|---|---|----|-----|---|---|-----|

|           | 8   | 7 | 6 | 5  | 4   | 3 | 2 | 1   |

| Octet 1   |     |   |   |    |     |   |   |     |

| Octet 2   |     |   |   |    |     |   |   |     |

|           |     |   |   |    |     |   |   |     |

| Octet N-1 |     |   |   |    |     |   |   |     |

| Octet N   |     |   |   |    |     |   |   |     |

#### Figure 4: Format convention

When a bit is contained within a single octet, the highest bit number (i.e. labelled 8) represents the high order or most significant bit (MSB).

In a multi-octet field, the order (i.e. the significance) of bit values within each octet decreases as the octet number increases. For example, a 16-bit field is coded in Figure 5.

|         | MSB                   |                 |                 | В               | its             |                 |                | LSB                  |

|---------|-----------------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------|----------------------|

|         | 8                     | 7               | 6               | 5               | 4               | 3               | 2              | 1                    |

| Octet 1 | 2 <sup>15</sup> (MSB) | 2 <sup>14</sup> | 2 <sup>13</sup> | 2 <sup>12</sup> | 2 <sup>11</sup> | 2 <sup>10</sup> | 2 <sup>9</sup> | 2 <sup>8</sup>       |

| Octet 2 | 2′                    | 2 <sup>6</sup>  | 2 <sup>5</sup>  | 2 <sup>4</sup>  | 2 <sup>3</sup>  | 2 <sup>2</sup>  | 2 <sup>1</sup> | 2 <sup>0</sup> (LSB) |

| Figure 5:  | Corres | pondina | codina | in | an       | IE o | r PDU |

|------------|--------|---------|--------|----|----------|------|-------|

| 1 19410 0. | 001100 | ponanig | ocanig |    | <b>u</b> |      |       |

13

# 5 User plane services

# 5.1 General

The user plane procedures of the 1394 SSCS provide the capabilities to transfer 1394 SSCS SDUs between two wireless 1394 devices over the HIPERLAN/2 network.

14

The behaviour of the user plane procedures for CC and WT is identical.

User plane services cover:

- a) Transport of 1394 SSCS SDU for both asynchronous and isochronous data;

- b) Clock synchronization service: this function provides a mechanism that allows any isochronous capable node to have its own cycle clock synchronized to the cycle clock of a single node.

# 5.2 Primitives (informative)

The higher layers (node or bridge applications) access to the 1394 SSCS is defined by the service primitives defined in this subclause. Normative definitions are therefore contained in [7] and HL2 1394 bridge layer (see Bibliography), for node and bridge applications respectively.

NOTE: The primitives are defined only for the purpose of describing layer-to-layer and sublayer-to-sublayer interactions. These primitives are defined as an abstract list of parameters, and their concrete realization may vary between implementations. No formal testing of primitives is intended. The following primitive definitions have no normative significance.

### 5.2.1 Primitive types

#### Interface between layers

Four primitive types may be used between different layers:

- request, for a higher layer to request service from a lower layer;

- confirm, for the layer providing the service to confirm the activity has been completed;

- indication, for a layer providing service to notify the next higher layer of any specific service related activity;

- response, for a layer to acknowledge receipt of an indication primitive from the next lower layer.

#### Interface between sublayers

Two different primitives may be used between different sublayers. To indicate the absence of a Service Access Point these primitives differ to the primitives between different layers:

- invoke, for a higher layer to request service from a lower layer;

- signal, for a layer providing service to notify the next higher layer of any specific service related activity.

The defined types for each category of primitive are shown as a list in curly brackets.

#### EXAMPLE: CL\_UNITDATA {request, indication}

In this example, the defined types are request and indication but not confirm or response.

# 5.2.2 Parameter definitions

**Message unit**: each piece of higher layer information that is included in the primitive is called a message unit. A series of one or more message units may be associated with each primitive where each separate unit is related to one information element in the corresponding DLC layer message. The list of message units is derived from the message definitions by reference to the information elements that may contain information from or (to) the CL.

### 5.2.3 Interface to the upper layer

### 5.2.3.1 Primitives related to isochronous traffic

These primitives are used either by a HL2 1394 bridge layer entity (see Bibliography) or by a streaming application.

#### 5.2.3.1.1 CL\_ISOCH\_STREAM {request, indication}

This primitive is used to transmit isochronous packets on the bus, using parameters specified in Table 1. This primitive is not confirmed.

#### Table 1: CL\_ISOCH\_STREAM parameters

| parameter                         | request | confirm | indication | response |

|-----------------------------------|---------|---------|------------|----------|

| Message units (possible elements) |         |         |            |          |

| time_stamp                        | always  |         | always     |          |

| isoch_header                      | always  |         | always     | —        |

| interface_data (SSCS SDU)         | always  |         | always     |          |

The time\_stamp parameter specifies a 32 bits time stamp that shall be inserted in the 1394 SSCS PDU.

The *isoch\_header* parameter includes *tag*, *channel*, *tcode*, and *sy* field, as defined by wired 1394.

The *interface\_data* parameter consists of the *data* and *pad* bytes, as well as *data\_CRC* fields, as defined by wired 1394.

### 5.2.3.1.2 CL\_CYCLE\_SYNCH {indication}

The 1394 SSCS entity uses this primitive to indicate to the upper layer that an isochronous period has passed (i.e. that CYCLE\_TIME.*offset\_count* has overflowed), using parameters specified in Table 2. This primitive is not confirmed.

#### Table 2: CL\_CYCLE\_SYNCH parameters

| parameter                         | request | confirm | indication | response |

|-----------------------------------|---------|---------|------------|----------|

| Message units (possible elements) |         |         |            |          |

| current_seconds_count             | _       |         | always     | _        |

| current_cycle_count               | —       | —       | always     | —        |

|                                   |         |         |            |          |

The *current\_seconds\_count* parameter contains the current value of the BUS\_TIME register.

The *current\_cycle\_count* parameter contains the current CYCLE\_TIME.cycle\_count value.

### 5.2.3.2 Primitives related to asynchronous traffic

These primitives are used by a 1394 Transaction Layer.

### 5.2.3.2.1 CL\_ASYNC\_ACTION {request, indication, confirm, response}

This primitive is used to transmit one primary asynchronous packet on the HIPERLAN/2 bus, using parameters specified in Table 3.

| parameter                         | request | confirm | indication | response |

|-----------------------------------|---------|---------|------------|----------|

| Message units (possible elements) |         |         |            |          |

| time_of_life                      | always  | —       | always     |          |

| response_flag                     | always  | —       | always     |          |

| interface_data (SSCS SDU)         | always  | —       | always     |          |

| crc_result                        | _       | —       | always     | always   |

| reply                             | —       | always  | _          | always   |

The *time\_of\_life* parameter is used to indicate how long this packet is allowed to live in the HL2 Bus. It may be negative, in that case an upper layer receiving it in an indication could take appropriate actions (such as discard the packet).

The *response\_flag* parameter differentiates between request and response packets, for the purposes of determining which DUC shall be used.

The *interface\_data* parameter consists of an asynchronous subaction (request or response) packet, as defined by wired 1394.

The *reply* code has one of the following values:

| reply_accepted | the interface data was accepted, but has not necessarily been transferred over the HL2 Bus. |

|----------------|---------------------------------------------------------------------------------------------|

| reply_busy     | the interface data was rejected because buffer space was temporarily unavailable.           |

| reply_missing  | the interface data could not be delivered because the <i>destination_ID</i> is invalid.     |

The crc\_result parameter indicates when the data\_CRC was found to be invalid.

#### 5.2.3.2.2 CL\_ASYNC\_STREAM {request, indication}

This primitive is used to transmit asynchronous stream packets on the bus, using parameters specified in Table 4. This primitive is not confirmed.

| parameter                         | request | confirm | indication | response |

|-----------------------------------|---------|---------|------------|----------|

| Message units (possible elements) |         |         |            |          |

| time_of_life                      | always  | —       | always     | —        |

| async_header                      | always  | —       | always     |          |

| interface_data (SSCS SDU)         | always  | —       | always     |          |

| crc_result                        |         | —       | always     | —        |

#### Table 4: CL\_ASYNC\_STREAM parameters

The *time\_of\_life* is used to indicate how long this packet is allowed to live in the HL2 Bus. It may be negative, in that case an upper layer receiving it in an indication could take appropriate actions (such as discard the packet).

The *async\_header* parameter consists of the asynchronous stream packet header as defined by wired 1394.

The *interface\_data* parameter consists of the header, header\_CRC, data, pad, and data\_CRC fields, as defined by wired 1394.

The *crc\_result* parameter indicates when the data\_CRC was found to be invalid.

### 5.2.4 Interface to the common part

The primitive CPCS\_UNITDATA {invoke, signal}, defined in [1], is used by the user plane procedures of the 1394 SSCS.

# 5.3 Clock synchronization service

### 5.3.1 General

Clock synchronization service aims to provide the means to synchronize clock registers of wireless nodes to their corresponding registers at the wireless cycle master (WCM) node. Clock registers are the following:

- BUS\_TIME,

- CYCLE\_TIME,

- LOCAL\_SECONDS,

- LOCAL\_CYCLES.

BUS\_TIME and CYCLE\_TIME registers are related to isochronous traffic, and shall be implemented by all isochronous capable wireless nodes. These registers are synchronized to the BUS\_TIME and CYCLE\_TIME registers of the WCM.

LOCAL\_SECONDS and LOCAL\_CYCLES maintain a local time within the HL2 Bus and shall be implemented by all wireless nodes. These registers are synchronized to the LOCAL\_SECONDS and LOCAL\_CYCLES registers of the WCM. The characteristic of these two registers is that they have to ensure that the time passes continuously. LOCAL\_SECONDS and LOCAL\_CYCLES registers of the WCM shall not be modified by the network cycle master in order to prevent any time discontinuities (see also in 6.5.2.2). LOCAL\_SECONDS and LOCAL\_CYCLES registers have only local significance. Time maintained by these registers is used by wireless nodes to timestamp asynchronous transactions (see subclause 5.4).

Detailed description of all these registers is given in Annex A; clauses A.1.4, A.1.5, A.1.6 and A.1.7.

Synchronization principles for BUS\_TIME, CYCLE\_TIME, LOCAL\_SECONDS and LOCAL\_CYCLES with their corresponding registers at the WCM are similar. The following principle is mainly focused on the synchronization of the CYCLE\_TIME register.

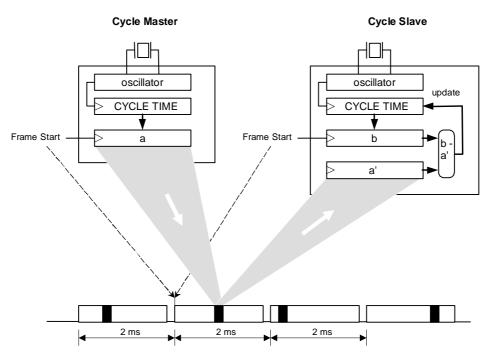

Synchronization principle of the CYCLE\_TIME register between the cycle master and a cycle slave is depicted in Figure 6. Referring to this illustration, when a frame start is observed by the cycle master the CYCLE\_TIME register is latched in the *a* register, and when the frame start is observed by a cycle slave the CYCLE\_TIME register is latched in the *b* register. The contents of the *a* register is transmitted to the cycle slave *a*' register. The time difference between *b* and *a*' is used to adjust the CYCLE\_TIME register of the cycle slave.

NOTE: The offset of the clock PDU in the frame is not constant; it may change as depicted in Figure 6.

17

Figure 6: Synchronization principle of the CYCLE\_TIME register

# 5.3.2 SSCS PDU format

The WCM shall broadcast clock information into clock PDU, which contains synchronized and local time values, as illustrated in Figure 7.

|          | 8 | 7            | 6        | 5       | 4        | 3      | 2       | 1 |

|----------|---|--------------|----------|---------|----------|--------|---------|---|

| Octet 1  |   |              |          |         |          |        |         |   |

| Octet 2  | 1 |              |          | isoch_s | seconds  |        |         |   |

| Octet 3  | 1 |              |          |         |          |        |         |   |

| Octet 4  | 1 |              |          |         |          |        |         |   |

| Octet 5  |   |              |          | isoch_  | cycles   |        |         |   |

| Octet 6  | ] |              |          |         |          |        |         |   |

| Octet 7  |   |              |          | isoch_  | _offset  | -      |         |   |

| Octet 8  |   |              | reserved |         |          | frame_ | counter |   |

| Octet 9  |   |              |          |         |          |        |         |   |

| Octet 10 |   |              |          | local_s | econds   |        |         |   |

| Octet 11 |   |              |          |         |          |        |         |   |

| Octet 12 |   |              |          |         |          |        |         |   |

| Octet 13 |   |              |          | local_  | cycles   |        |         |   |

| Octet 14 |   |              |          |         |          |        |         |   |

| Octet 15 |   | local_offset |          |         |          |        |         |   |

| Octet 16 | [ |              |          |         | reserved |        |         |   |

Figure 7: Clock SSCS PDU format

Clock PDU fields are defined as follows:

- The 32-bit *isoch\_seconds* field shall contain the value of the BUS\_TIME register at the time when the DLC\_MAC\_FRAME\_START primitive was received by the 1394 SSCS entity of the WCM.

- The 13-bit *isoch\_cycle* field shall contain the value of CYCLE\_TIME. *cycle\_count* at the time when the DLC\_MAC\_FRAME\_START primitive was received by the 1394 SSCS entity of the WCM.

- The 12-bit *isoch\_offset* field shall contain the value of the CYCLE\_TIME. *cycle\_offset* at the time when the DLC\_MAC\_FRAME\_START primitive was received by the 1394 SSCS entity of the WCM.

- The 32-bit *local\_seconds*, 13-bit *local\_cycles* and 12-bit *local\_offset* fields are copies of like named fields from the LOCAL\_SECONDS and LOCAL\_CYCLES registers at the time when the DLC\_MAC\_FRAME\_START primitive was received by the 1394 SSCS entity of the WCM.

- The 4-bit *frame\_counter* identifies the number of the MAC frame which preamble was taken as a reference point for the initialization of the all other fields of the SSCS PDU. DLC\_MAC\_FRAME\_NUMBER primitive furnishes the MAC frame number.

### 5.3.3 Procedures

#### 5.3.3.1 Procedure in the wireless cycle master (WCM)

Each time the MAC frame start preamble is detected by means of the DLC\_MAC\_FRAME\_START indication primitive, the WCM shall take a snap-shot of its BUS\_TIME, CYCLE\_TIME, LOCAL\_SECONDS, LOCAL\_CYCLES registers, and shall construct a SSCS PDU as follows:

- *isoch\_seconds* contains the BUS\_TIME.*seconds* value,

- *isoch\_cycles* contains the CYCLE\_TIME.*cycle\_count* part,

- *isoch\_offset* contains the CYCLE\_TIME.cycle\_offset part,

- *local\_seconds* contains the LOCAL\_SECONDS.seconds register value,

- *local\_cycles* contains the LOCAL\_CYCLES.cycle\_count part,

- *frame\_counter* contains the number of the frame which preamble was taken as reference point to all wireless nodes.

The WCM sends this SSCS PDU using the CPCS\_UNITDATA invoke primitive to the CPCS entity.

#### 5.3.3.2 Procedure in a wireless cycle slave (WCS)

Each time the MAC frame start preamble is detected by means of the DLC\_MAC\_FRAME\_START indication primitive, the WCS shall take a snap-shot of its BUS\_TIME (if any), CYCLE\_TIME (if any), LOCAL\_SECONDS, LOCAL\_CYCLES registers, and shall store the result in a temporary register along with the *frame\_counter* of the MAC\_FRAME\_START primitive.

When the WCS receives a CPCS\_UNITDATA signal primitive for the clock DLC Connection, it shall check whether the received SSCS PDU corresponds to a measured snap-shot (by checking the *frame\_counter field*). If the frame\_counter matches, the WCS is able to update its clock registers. The way registers are updated is implementation dependent.

In the case the 1394 SSCS entity receives SSCS PDUs from the forwarding channel (see in 6.5), then snap-shots for the two last frames shall be stored in a temporary register.

# 5.4 Asynchronous transaction data transport service

### 5.4.1 General

The purpose of the asynchronous transaction service is to reliably communicate asynchronous transaction components, i.e. request or response subaction packets, between two 1394 SSCS peer entities. A busy-acknowledge based flow control limits the flow rate of the higher level transmitter to that which can be supported by the lower layers.

The upper layer is responsible for creation and checking of 1394 specified packets, including their *header\_CRC* and *data\_CRC* values. Higher level CRC coverage is a necessity because the undetected error rate of the lower level transport (approximately  $10^{-11}$ ) is less than that expected by 1394.

At the higher level, losses of asynchronous packets are detected through timeouts. In support of such timeout protocols, higher level transmitters send each packet to the 1394 SSCS entity with a time\_of\_life parameter, thereby limiting its effective lifetime within the HL2 Bus. At the higher level, receivers are required to check the time\_of\_life parameter, discarding these packets if their allocated time-to-live has expired.

When passing through the 1394 SSCS entity, the packet's time\_of\_life parameter shall be converted to a time\_of\_death label, by adding the current time to the time\_of\_life parameter. The time\_of\_death label uses the clock synchronization service (at least only the seconds and cycle counts of it). When passed to the higher level, the packet's time\_of\_death parameter shall be returned to a time\_of\_life parameter, thereby insulating the higher level protocols from the lowest level timing parameters.

# 5.4.2 Asynchronous SSCS PDU coding

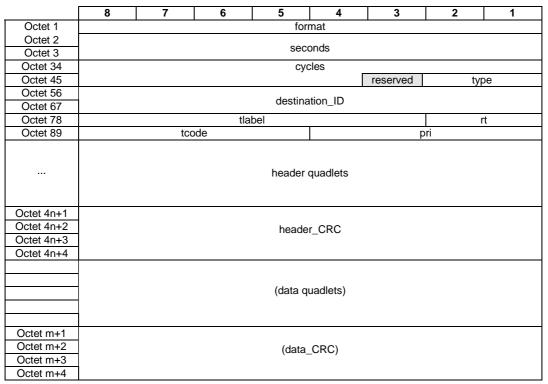

The 1394 SSCS asynchronous subaction PDU consists of a format, a time-stamp and a wired-1394 asynchronous packet, as illustrated in Figure 8.

#### Figure 8: Asynchronous subaction SSCS PDU format

Each PDU starts with a *format* field that describes which encapsulation scheme is applied for this asynchronous subaction packet PDU. *Format* values are described in Table 5.

#### Table 5: format values

| Value | Name                    | Description                                             |

|-------|-------------------------|---------------------------------------------------------|

| 0     | iso_stream_bus_packet   | Encapsulation of wired-1394 isochronous stream packets  |

| 1     | async_stream_bus_packet | Encapsulation of wired-1394 asynchronous stream packets |

| 2     | async_subaction         | Encapsulation of asynchronous subaction packets         |

| 3-254 | -                       | Reserved                                                |

The 1394 SSCS PDU also contains a time\_of\_death label. This time\_of\_death label has 16-bit *seconds* and 13-bit *cycles* field components, representing time in seconds and multiples of 125 µs units respectively.

The 2-bit type field specifies the packet type, as specified in Table 6.

| Value | Name           | Description                                                        |

|-------|----------------|--------------------------------------------------------------------|

| 0     | ASYNC_REQUEST  | Asynchronous request and response packet with time_of_death header |

| 1     |                | Reserved                                                           |

| 2     | CLOSE_REQUEST  | Clean-closing request (header quadlet only), see 6.8.2             |

| 3     | CLOSE_RESPONSE | Clean closing response (header quadlet only), see 6.8.2            |

The remainder of the packet consists of a subaction as defined by wired 1394. The *tlabel*, *rt*, *pri* fields, the remaining header quadlets, and the data quadlets are processed as user data and (except for their inclusion in the CRC calculations) are ignored by the 1394 SSCS entity. Other fields are described in the remainder of this subclause and can effect the 1394 SSCS entity processing.

The *destination\_ID* that consists of a 10-bit *bus\_ID* and 6-bit *physical\_ID* components specifies which node is intended to receive the packet.

The *header\_CRC* value is located at a *tcode*-dependent offset (as defined in [6]) and covers the fourth through preceding bytes. The initial four bytes are not covered by the *header\_CRC* value.

Some packets contain data after the header\_CRC value. For such packets, the *data\_CRC* value covers these data bytes and the zero-valued pad bytes defined in [6].

### 5.4.3 Asynchronous packets management

To transfer asynchronous transaction between two nodes A and B, a single duplex DUC shall be opened, as defined in 6.8. One DUC is used to send requests from A to B and responses from B to A, which is sufficient if A is the requester and B is the responder. A different DUC (if necessary) would be used to send requests from B to A and responses from A to B. This prevents deadlocks that may appear if requests and responses are using a single DLC connection.

Thus, the opening of a DUC necessarily involves the passing of an information element, that specifies whether the opening node is the requester or responder. This is further described in 6.8.1.

When a 1394 SSCS receives a CL\_CONTROL.asynchronous\_path\_reset, all open DUCs shall be closed as described in 6.8.2.

#### 5.4.4 Procedures

#### 5.4.4.1 Procedure in the sender

This service is started on the upper layer request, when using the CL\_ASYNC\_ACTION request primitive. The service involves a sequence of steps, listed below.

- 1) If the *destination\_ID.busID* and request/response property (see 5.4.3) are associated with an open DUC, then skip to step 5.

- 2) The *destination\_ID* field is processed to generate physicalAddr, the HL2-bus destination's physical\_ID address:

- a) If *destination\_ID.bus\_ID* equals NODE\_IDS.*bus\_ID* (NODE\_IDS is a CSR described in Annex A), then physicalAddr equals *destination\_ID.physical\_ID*.

- b) Otherwise, the *destination\_ID.bus\_ID* value is used as a parameter of a HARP operation (see 6.7) that returns a physicalAddr address. If the HARP operation fails to return a valid physicalAddr address, then a CL\_ASYNC\_ACTION confirm, with a *reply\_missing* code, is returned.

- 3) The physicalAddr value is processed to retrieve the mac\_ID address of the destination node by checking self-ID information (see 5.4.3 and 6.4). If no mac\_ID address is found, then a CL\_ASYNC\_ACTION confirm, with a *reply\_missing* code, is returned.

- 4) If no currently open DUC supports communications with the mac\_ID address, then a DUC is opened for this purpose as described in 6.8. For efficiency, the *destination\_ID.bus\_ID* value may remain associated with the open DUC until the DUC is closed.

- 5) If the *time\_of\_life* value is negative, the packet shall be discarded. Otherwise, the *time\_of\_life* is added to the time values contained in LOCAL\_SECONDS/LOCAL\_CYCLES (these are CSRs described in Annex A) to generate a *time\_of\_death* value. The *time\_of\_death* value shall then be placed in the *seconds/cycles* fields of the packet.

- 6) If buffer space is not available in the lower layer, then a CL\_ASYNC\_ACTION confirm, with a *reply\_busy* code, is returned. Otherwise, the 1394 SSCS PDU is posted to the CPCS in a CPCS\_UNITDATA invoke primitive and a CL\_ASYNC\_ACTION confirm, with a *reply\_accepted* code is returned.

### 5.4.4.2 Procedure in receiver

The *header\_CRC* is checked. If the header is found to be corrupted, the packet is discarded.

The time values contained in LOCAL\_SECONDS/LOCAL\_CYCLES (these are CSRs described in Annex A) are subtracted from the *time\_of\_death* value to generate the time\_of\_life value that is included in the CL\_ASYNC\_ACTION indication primitive.

The *data\_CRC* is checked and the result of this check is included in the CL\_ASYNC\_ACTION indication primitive.

NOTE: For efficiency, a *source\_ID.bus\_ID* of a packet received from the requester (see 6.8.1) may be associated (as described in 5.4.4.1) with the DUC. This has the effect of eliminating the need to do an additional HARP when the expected response is returned.

# 5.5 Stream data transport service

### 5.5.1 Isochronous stream data transport service

#### 5.5.1.1 General

The purpose of the isochronous stream data transport service is to reliably transmit isochronous streams between two 1394 SSCS peer entities.

The upper layer is responsible for the generation and the reception of SDUs, representing individual 125  $\mu$ s isochronous packets. Each SDU is received from the upper layer with a time stamp. This time represents the time when the packet was generated. It is encoded in the PDU, as described below, and thus transmitted by the 1394 SSCS entity to its peer so that the SDU is delivered to the destination upper layer with the time stamp. The time stamp may then be used by the upper layer to provide a constant delay service.

Each SDU is protected by a 32 bits CRC. Corrupted data are discarded by the 1394 SSCS entity.

The sending 1394 SSCS entity is responsible for concatenating the product of multiple SDUs into a single larger 2ms PDU. The receiving 1394 SSCS entity is responsible for regenerating multiple SDUs, representing individual 125  $\mu$ s isochronous packets from a 2 ms PDU.

### 5.5.1.2 Isochronous stream SSCS PDU coding

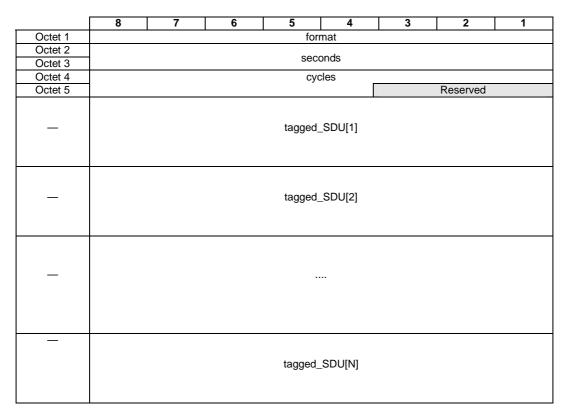

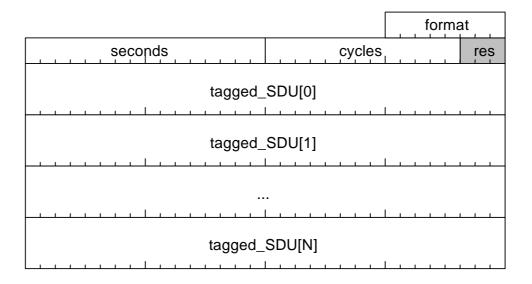

For efficiency, several SDUs are collected into a single PDU, as illustrated in Figure 9 and described in the remainder of this Part.

#### Figure 9: Isochronous SSCS PDU format

A SDU is defined here as a 1394 isochronous packet as defined by wired 1394. The associated 1394 isochronous packet header is not part of the SDU, but is one of the parameters of the associated primitive (as described in 5.2.3.1.1).

Each PDU starts with a *format* field that describes which encapsulation scheme is applied for this stream PDU. *Format* values are described in Table 5.

A quadlet time-stamp label indicates then the isochronous cycle when the first SDU within the PDU was created. The time stamp label has 16-bit *seconds* and 13-bit *cycles* field components, representing BUS\_TIME/CYCLE\_TIME specified time in seconds and cycles (multiples of 125 µs units) respectively.

The remainder of the packet consists of the concatenation of tagged SDUs. For each SDU, the tag consists of its corresponding wired-1394 header, except that the channel number is replaced by 6-bits of the primitive supplied time-stamp value.

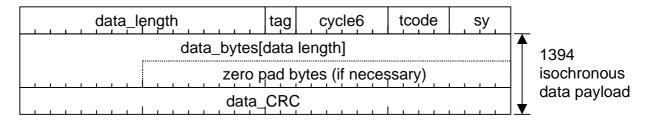

#### Figure 10: Isochronous tagged SDU format

*data\_length* field represents the length of the following tagged SDU. It contains the length of the data field of the 1394 packet (without comprising the 1394 packet padding bytes). The *data\_length* field is the same as the *data\_length* field of the corresponding wired-1394 packet header (retrieved from or sent in the primitive).

*tag* field contains the *tag* field value of the corresponding wired-1394 packet header (retrieved from or sent in the primitive).

*cycle\_low* field contains the 6 least significant bits of the *cycle\_count* field from the time stamp that came to the 1394 SSCS entity along with the SDU.

24

*tcode* field contains the *tcode* field value of the corresponding wired-1394 packet header (retrieved from or sent in the primitive).

sy field contains the sy field value of the corresponding wired-1394 packet header (retrieved from or sent in the primitive).

*data\_quadlets* represent data bytes as they were received in the SDU. They may contain padding bytes (the total number of data\_quadlet bytes represents an integer number of quadlets).

data\_CRC is the data CRC as defined by wired 1394.

NOTE: data\_length field does not necessarily give the SDU size. Some padding bytes may be necessary to add to the data\_length in order to get the total SDU size.

#### 5.5.1.3 Procedure

#### 5.5.1.3.1 Procedure in the sender

Upon the reception of a CL\_ISOCH\_STREAM request primitive, the 1394 SSCS entity shall check whether a multicast DUC is open for this SDU: the 1394 SSCS entity shall extract the 1394 *channel* field from the isoch\_header primitive parameter. It shall then check whether there is an active DLC User Connection for a multicast channel corresponding to this 1394 channel (see 6.9). If there is no such open DUC, then the SDU shall be discarded. Otherwise, the 1394 SSCS entity collects several SDUs, received in several CL\_ISOCH\_STREAM request primitives into a single PDU.

The 1394 SSCS entity shall encode the *seconds* and *cycles* fields of the PDU with the time\_stamp value of the first SDU (that was received in the CL\_ISOCH\_STREAM request primitive).

For each SDU, all the 1394 header fields, except the *channel* and the *header CRC* (that were received in the CL\_ISOCH\_STREAM request primitive) are copied into the corresponding fields tagging the SDU (*tag, tcode, sy*).

For each SDU, the *cycle\_low* field is encoded with the 6 less significant bits of the time\_stamp.*cycle\_offset* primitive parameter.

*data\_CRC* field is also encoded with the data\_CRC from the CL\_ISOCH\_STREAM request primitive. This corresponds to a wired-1394 data CRC.

The 1394 SSCS entity shall build and post a PDU to the CPCS every HL2 frame. A DLC primitive (DLC\_MAC\_FRAME\_START), described in [4] is available to determine when a HL2 frame starts.

Each PDU nominally contains 16 SDUs, although the number of SDUs can be less than 16 (if an isochronous packet is not sent in every cycle), 15 (if an isochronous packet is sent in every cycle, but the isochronous cycle duration is larger than 1/16 of the HL2 frame duration), or 17 (if an isochronous packet is sent in every cycle, but the isochronous cycle duration is shorter than 1/16 of the HL2 frame duration).

SDUs shall not be fragmented among different PDUs.

If the upper layer does not generate CL\_ISOCH\_STREAM request primitives within some 2 ms periods, empty PDUs may also be generated (a PDU with no SDU). In this case the empty PDU shall contain at least an empty SDU (i.e. data\_length field encoded with 0, no data\_quadlet field and a data\_CRC encoded with 0). An empty PDU shall have 0 in the *seconds* and *cycles* fields as well as in the *tag*, *tcode*, *sy* and *cycle\_low* fields.

#### 5.5.1.3.2 Procedure in the receiver

The 1394 SSCS entity shall regenerate individual SDUs. It shall parse the PDU, and the individual *data\_length* fields to recover individual SDUs. Since every *data\_quadlets* field is quadlet aligned (i.e. it corresponds to an integer number of quadlets), the *data\_length* field does not necessarily point to the end of the *data\_quadlets* field.

- The 1394 SSCS entity shall compute the *data\_CRC* field, and discard corrupted SDUs.

- Based on the *cycle\_low* field of every SDU tag, and on the *seconds* and *cycles* fields of the PDU, the 1394 SSCS entity shall generate a time\_stamp parameter.

- Based on the SDU tag, the 1394 SSCS entity shall generate the isoch\_header primitive parameter corresponding to the SDU: *tag*, *tcode* and *sy* are extracted from the received SDU tag and copied as they are in the corresponding isoch\_header fields. The PDU was received on a multicast channel for which there is a correspondence to a 1394 channel, which is used to fill the *channel* field of the isoch\_header primitive parameter.

- The 1394 SSCS entity shall send the SDU along with the time\_stamp and isoch\_header parameters to the upper layer in a CL\_ISOCH\_STREAM indication primitive.

The receiver of isochronous streams shall be prepared for these streams to experience a maximum transmission delay of 8 ms as described in C.4.2.

### 5.5.2 Asynchronous stream data transport service

#### 5.5.2.1 General

The purpose of the asynchronous stream data transport service is to reliably transmit asynchronous streams between two 1394 SSCS peer entities.

The upper layer is responsible for the generation and the reception of SDUs, representing individual asynchronous stream packets. Each SDU is received from the upper layer with a time\_of\_life.

When passing through the 1394 SSCS entity, the packet's time\_of\_life parameter shall be converted to a time\_of\_death label, by adding the current time to the time\_of\_life parameter. The time\_of\_death label uses the clock synchronization service (at least only the seconds and cycle counts of it). When passed to the higher level, the packet's time\_of\_death parameter shall be returned to a time\_of\_life parameter, thereby insulating the higher level protocols from the lowest level timing parameters.

Each SDU is also protected by a 32 bits CRC. Corrupted data are detected by the 1394 SSCS entity, and are signalled to the upper layer as corrupted.

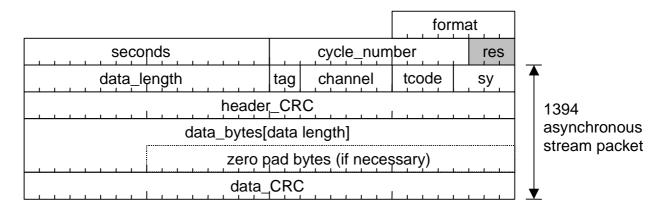

### 5.5.2.2 Asynchronous stream SSCS PDU coding

An SDU is defined here as a 1394 asynchronous stream packet as defined by wired 1394. The associated 1394 asynchronous stream packet header is not part of the SDU, but is one of the parameters of the associated primitive (as described in 5.2.3.2.2)

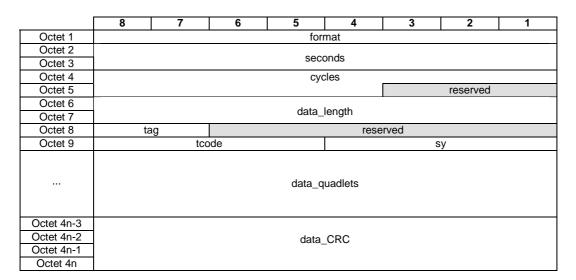

#### Figure 11: Asynchronous stream PDU format

Each PDU starts with a *format* field that describes which encapsulation scheme is applied for this stream PDU. *Format* values are described in Table 5.

A quadlet time\_of\_death label having a 16-bit *seconds* and 13-bit *cycles* field components represents time in seconds and multiples of 125 µs units respectively.

*data\_length* field represents the length of the following SDU. It contains the length of the data field of the 1394 packet (without comprising the 1394 packet padding bytes). The *data\_length* field is the same as the *data\_length* field of the corresponding wired-1394 packet header (retrieved from or sent in the primitive).

*tag* field contains the *tag* field value of the corresponding wired-1394 packet header (retrieved from or sent in the primitive).

reserved field corresponds to the channel field of the wired-1394 packet header, and shall be filled with 0.

*tcode* field contains the *tcode* field value of the corresponding wired-1394 packet header (retrieved from or sent in the primitive).

*sy* field contains the *sy* field value of the corresponding wired-1394 packet header (retrieved from or sent in the primitive).

*data\_quadlets* represent data bytes as they were received in the SDU. They may contain padding bytes (the total number of data\_quadlet bytes represents an integer number of quadlets).

*data\_CRC* is the data CRC as defined by wired 1394.

#### 5.5.2.3 Procedure

#### 5.5.2.3.1 Procedure in the sender

Upon the reception of a CL\_ASYNC\_STREAM request primitive, the 1394 SSCS entity shall check whether a DLC multicast group is existing for this SDU: the 1394 SSCS entity shall extract the 1394 *channel* field from the *async\_header* primitive parameter. It shall then check whether there is a DLC multicast group corresponding to this 1394 channel (at least whether the 1394 SSCS entity has joined such a DLC multicast group as described in 6.10). If the 1394 SSCS entity did not join such a DLC multicast group, then the SDU shall be discarded. Otherwise, the 1394 SSCS entity shall build a PDU according to 5.5.2.2.

If the *time\_of\_life* value is negative, the packet shall be discarded. Otherwise, the *time\_of\_life* is added to the time values contained in LOCAL\_SECONDS/LOCAL\_CYCLES (these are CSRs described in Annex A) to generate a *time\_of\_death* value. The *time\_of\_death* value shall then be placed in the *seconds/cycles* fields of the packet.

All the 1394 header fields, except the *channel* and the *header CRC* (that were received in the CL\_ISOCH\_STREAM request primitive) are copied into the corresponding fields of the PDU (*data\_length tag, tcode, sy*).

#### Reserved bits are set to 0.

If the *data\_quadlets* field is present *data\_CRC* field is also encoded with the data\_CRC from the CL\_ISOCH\_STREAM request primitive. This corresponds to a wired-1394 data CRC. If the *data\_quadlets* field is absent (as can occur, when a channel is active but no data is available to be transmitted), then the *data\_CRC* value is not included on the wired-1394 packet and is therefore not included in the 1394 SSCS PDUs.

The 1394 SSCS entity shall build and post a PDU to the CPCS in a CPCS\_UNITDATA invoke primitive.

#### 5.5.2.3.2 Procedure in the receiver

Upon the reception of a CPCS\_UNITDATA signal primitive from the CPCS:

- The 1394 SSCS entity shall compute the *data\_CRC* field, if present. The result of this operation is included in the CL\_ASYNC\_STREAM indication primitive. Based on the *cycle\_low* field of every SDU tag, and on the *seconds* and *cycles* fields of the PDU, the 1394 SSCS entity shall generate a time\_stamp parameter.

- The 1394 SSCS entity shall generate the *async\_header* primitive parameter. It shall extract the *tag*, *tcode* and *sy* PDU fields and copy as they are in the corresponding isoch\_header fields. The PDU was received on a multicast channel for which there is a correspondence to a 1394 channel that is used to fill the *channel* field of the isoch\_header primitive parameter.

- *time of life* primitive parameter is generated by subtracting the time values contained in LOCAL\_SECONDS/LOCAL\_CYCLES (these are CSRs described in Annex A) from the *time\_of\_death* value.

- The 1394 SSCS entity shall send the SDU along with the *time\_of\_life* and *isoch\_header* parameters to the upper layer in a CL\_ISOCH\_STREAM indication primitive.

# 6 Control plane services

# 6.1 General

The control plane of the 1394 SSCS interacts with the DLC control plane (i.e. the RLC sublayer) via the DLC Control Service Access Point defined in [2]. It also uses the services of the Common Part of the Packet based Convergence Layer [1].

The following functions are performed by the control plane procedures of the 1394 SSCS:

- a) Triggering of DLC connection setup. This includes:

- Clock information DLC Connections (done at association time, and when connectivity to the wireless cycle master changes);

- Isochronous and asynchronous streams. This is done on upper layer request using isochronous resource manager (IRM) services (as described in 6.8);

- Asynchronous transaction data. This is done when the address resolution mechanism requests it (as described in 6.5).

- b) Triggering of DLC multicast and broadcast join procedures. This includes:

- Clock information DLC Connections (done at association time, and when connectivity to the wireless cycle master changes);

- Isochronous and asynchronous streams. This is done on upper layer request using plug control register (PCR) services (as described in 6.8).

- c) Triggering of a bus reset process. This includes:

- 1394 physical\_ID allocation;

• Distribution of all the 1394 physical\_IDs of the HL2 Bus.

The following DLC C-SAP primitives defined in [4] are used by the control plane procedures of the 1394 SSCS:

- DLC\_SETUP {request, indication};

- DLC\_CONNECT {request, confirm, indication, response};

- DLC\_RELEASE { request, confirm, indication, response };

- DLC\_MULTICAST\_JOIN {request, confirm, indication, response};

- DLC\_MULTICAST\_LEAVE {request, indication};

- DLC\_MULTICAST\_CONNECT {request, confirm, indication, response};

- DLC\_MULTICAST\_RELEASE {request, confirm, indication, response};

- DLC\_MULTICAST\_MODIFY {request, confirm, indication, response};

- DLC\_INFO\_TRANSFER {request, confirm, indication, response};

- DLC\_MAC\_FRAME\_START {indication, response};

- DLC\_MAC\_FRAME\_NUMBER {indication, response};

- DLC\_START\_CL\_HO {indication, response};

- DLC\_START\_CC {indication, response}.

The DLC\_INFO\_TRANSFER primitive corresponds to the RLC\_INFO primitive in the RLC layer. The RLC\_INFO function, which is optional in RLC layer (as described in [2]), shall be mandatory for a RLC that supports the 1394 SSCS services.

# 6.2 Primitives (informative)

These primitives are used by the upper layer in a wireless 1394 device.

# 6.2.1 CL\_CONTROL {request, confirm}

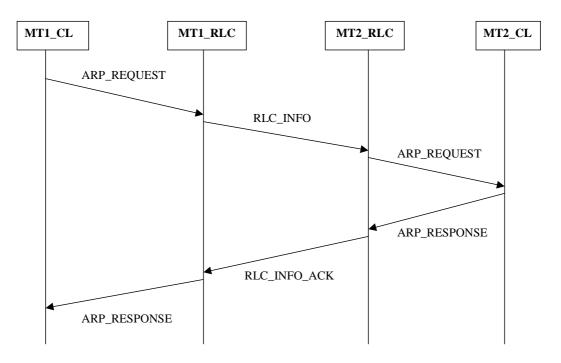

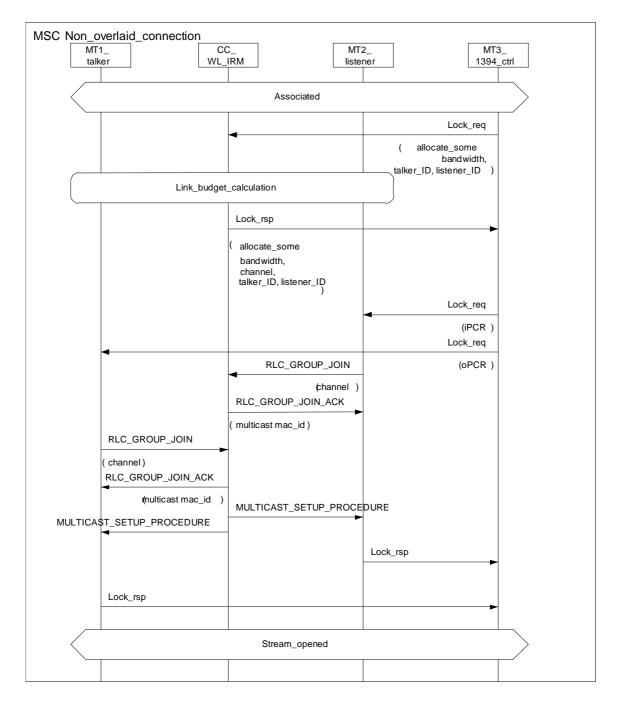

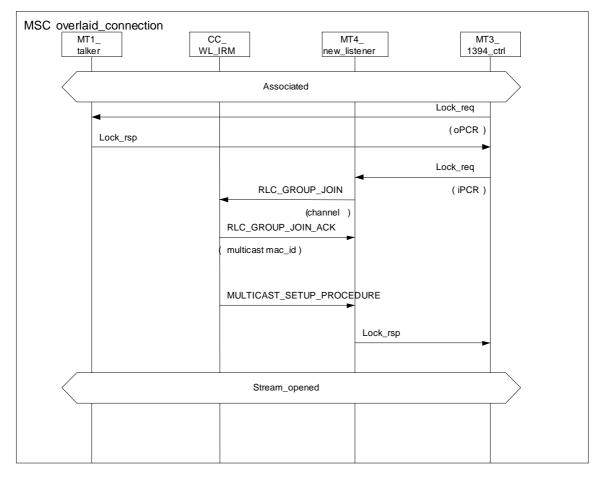

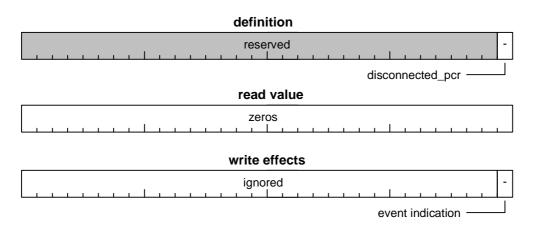

The upper layer uses this service to request the convergence layer to perform specific actions. This service is confirmed.