# EUROPEAN TELECOMMUNICATION STANDARD

Source: ETSI TC-BTC

Reference: DE/BTC-02057

**FINAL DRAFT**

pr ETS 300 689

October 1996

ICS: 33.040.40

Key words: Access, digital, interface, leased line, ONP, terminal

Business TeleCommunications (BTC); 34 Mbit/s digital leased lines (D34U and D34S); Terminal equipment interface

## ETSI

European Telecommunications Standards Institute

## **ETSI Secretariat**

**Postal address:** F-06921 Sophia Antipolis CEDEX - FRANCE **Office address:** 650 Route des Lucioles - Sophia Antipolis - Valbonne - FRANCE **X.400:** c=fr, a=atlas, p=etsi, s=secretariat - **Internet:** secretariat@etsi.fr

Tel.: +33 92 94 42 00 - Fax: +33 93 65 47 16

**Copyright Notification:** No part may be reproduced except as authorized by written permission. The copyright and the foregoing restriction extend to reproduction in all media.

Page 2 Final draft prETS 300 689: October 1996

Whilst every care has been taken in the preparation and publication of this document, errors in content, typographical or otherwise, may occur. If you have comments concerning its accuracy, please write to "ETSI Editing and Committee Support Dept." at the address shown on the title page.

## Contents

| Forew  | vord           |              |                 |                                            | 5  |

|--------|----------------|--------------|-----------------|--------------------------------------------|----|

| Introd | uction         |              |                 |                                            | 5  |

| 1      | Scope          |              |                 |                                            | 7  |

| 2      | Normativ       | e reference  | s               |                                            |    |

| -      |                |              | •               |                                            |    |

| 3      |                |              |                 |                                            |    |

|        | 3.1            |              |                 |                                            |    |

|        | 3.2            | Abbreviatio  | ons             |                                            | 8  |

| 4      | Requiren       | nents        |                 |                                            | Q  |

| -      | 4.1            |              |                 | S                                          |    |

|        |                | 4.1.1        |                 |                                            |    |

|        |                | 4.1.2        |                 |                                            |    |

|        | 4.2            | Electrical c |                 |                                            |    |

|        |                | 4.2.1        |                 |                                            |    |

|        |                |              | 4.2.1.1         | Signal coding                              |    |

|        |                |              | 4.2.1.2         | Waveform shape                             |    |

|        |                |              | 4.2.1.3         | Output timing                              | 11 |

|        |                |              | 4.2.1.4         | Output return loss                         | 12 |

|        |                |              | 4.2.1.5         | Output jitter                              | 12 |

|        |                |              | 4.2.1.6         | Output frame structure                     | 12 |

|        |                | 4.2.2        | Input port      | -                                          | 13 |

|        |                |              | 4.2.2.1         | Signal coding                              | 13 |

|        |                |              | 4.2.2.2         | Input return loss                          | 13 |

|        |                |              | 4.2.2.3         | Input loss tolerance                       |    |

|        |                |              | 4.2.2.4         | Immunity against reflections               | 13 |

|        |                |              | 4.2.2.5         | Input jitter tolerance                     | 13 |

|        |                |              | 4.2.2.6         | Input clock tolerance                      |    |

|        |                |              | 4.2.2.7         | Input frame structure                      |    |

|        |                |              | 4.2.2.8         | Frame alignment procedure                  |    |

|        | 4.3            |              |                 |                                            |    |

|        | 4.4            |              |                 |                                            |    |

|        | 4.5            | ElectroMag   | gnetic Compat   | ibility (EMC)                              | 15 |

| Annex  | k A (norm      | ative): T    | est methods     |                                            | 16 |

|        |                |              |                 |                                            |    |

| A.1    |                |              |                 |                                            |    |

|        | A.1.1          |              |                 | support the test                           |    |

|        | A.1.2          | Equipment    | connection      |                                            |    |

| A.2    | Tost mot       | hode         |                 |                                            | 17 |

| A.Z    | A.2.1          |              |                 | ut port                                    |    |

|        | A.2.1<br>A.2.2 |              |                 | putput port                                |    |

|        | A.2.2<br>A.2.3 |              |                 |                                            |    |

|        | A.2.3<br>A.2.4 |              |                 | tolerance and immunity against reflections |    |

|        | A.2.4<br>A.2.5 | • •          | -               |                                            |    |

|        | A.2.5<br>A.2.6 |              |                 |                                            |    |

|        | A.2.7          |              |                 |                                            |    |

|        | A.2.8          |              |                 |                                            |    |

|        | A.2.9          |              |                 | ure                                        |    |

|        |                | Ũ            |                 |                                            |    |

| Annex  | k B (norm      | ative): D    | efinition of HE | DB3 code                                   | 26 |

#### Page 4 Final draft prETS 300 689: October 1996

| B.1    | General                   |                                                                                                                                                                                                 |  |

|--------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| B.2    | Definition                |                                                                                                                                                                                                 |  |

| Annex  | c C (normative):          | Definition of frame structure                                                                                                                                                                   |  |

| C.1    | C.1.1 Trail ac<br>C.1.1.1 | at 34 368 kbit/s<br>cess point identifier format<br>CRC-7 calculation - multiplication and division process<br>CRC-7 calculation - encoding procedure<br>CRC-7 calculation - decoding procedure |  |

| Annex  | c D (normative):          | ETS Requirements Table (ETS-RT)                                                                                                                                                                 |  |

| Annex  | KE (informative):         | Bibliography                                                                                                                                                                                    |  |

| Histor | у                         |                                                                                                                                                                                                 |  |

## Foreword

This final draft European Telecommunication Standard (ETS) has been produced by the Business TeleCommunications (BTC) Technical Committee of the European Telecommunications Standards Institute (ETSI), and is now submitted for the Voting phase of the ETSI standards approval procedure.

This final draft ETS resulted from a mandate from the Commission of the European Community (CEC) to provide harmonized standards for the support of the Directive on Open Network Provision (ONP) of leased lines (92/44/EEC).

There are two other standards directly related to this ETS:

- ETS 300 686: "Business TeleCommunications (BTC); 34 Mbit/s and 140 Mbit/s digital leased lines (D34U, D34S, D140U and D140S); Network interface presentation";

- ETS 300 687: "Business TeleCommunications (BTC); 34 Mbit/s digital leased lines (D34U and D34S); Connection characteristics".

| Proposed transposition dates                                                               |                                 |  |  |  |

|--------------------------------------------------------------------------------------------|---------------------------------|--|--|--|

| Date of latest announcement of this ETS (doa):                                             | 3 months after ETSI publication |  |  |  |

| Date of latest publication of new National Standard<br>or endorsement of this ETS (dop/e): | 6 months after doa              |  |  |  |

| Date of withdrawal of any conflicting National Standard (dow):                             | 6 months after doa              |  |  |  |

This ETS is based on information from ITU-T Recommendations and ETSI publications and the relevant documents are quoted where appropriate.

### Introduction

The Council Directive on the application of ONP to leased lines (92/44/EEC) concerns the harmonisation of conditions for open and efficient access to, and use of, the leased lines provided over public telecommunications networks, and the availability throughout the European Union of a minimum set of leased lines with harmonized technical characteristics.

The 34 Mbit/s unstructured and structured leased lines are not part of the minimum set of leased lines under the leased line Directive, however these standards are being written with the intention that where 34 Mbit/s leased lines are offered, they will be in accordance with these harmonized standards.

Two classes of standard will be used for the interfaces of terminal equipment designed for connection to the ONP leased lines. European Telecommunication Standards (ETSs), which are voluntary, give the full technical specifications for these interfaces, whereas Technical Basis for Regulations (TBRs) give the essential requirements under the Second Phase Directive (91/263/EEC) for attachment to the leased lines. The TBR (TBR 24) will be a subset of the corresponding ETS. This standard, which is an ETS, belongs to the first category.

ETS 300 166 and ITU-T Recommendation G.703 are used as the basis for the terminal equipment interface.

Blank page

### 1 Scope

This ETS specifies the full mechanical and electrical characteristics, the necessary functional characteristics and the corresponding conformance tests for a terminal equipment interface for:

- connection to the network termination points of 34 368 kbit/s digital unstructured leased lines (D34U); and

- connection to the network termination points of 34 368 kbit/s digital structured leased lines (D34S) which support an unstructured 33 920 kbit/s information transfer rate.

These leased lines are defined in ETS 300 686 and ETS 300 687.

This ETS is not written for regulatory purposes.

This ETS is written only to ensure that the interface of the terminal equipment is compatible with the 34 Mbit/s digital unstructured or structured leased line. This ETS is applicable to all interfaces designed for connection to the leased line, however in the cases of apparatus that carries a particular service, of complex apparatus and of apparatus in private networks, other ETSs may apply in addition to this ETS.

Customer premises wiring and installation between the terminal equipment and the Network Termination Point (NTP) are outside the scope of this ETS.

## 2 Normative references

This ETS incorporates by dated or undated reference, provisions from other publications. These normative references are cited at the appropriate places in the text and the publications are listed hereafter. For dated references, subsequent amendments to, or revisions of any of these publications apply to this ETS only when incorporated into it by amendment or revision. For undated references the latest edition of the publication referred to applies.

- [1] EN 60950 (1992): "Safety of information technology equipment including electrical business equipment".

- [2] IEC 169-8:1978: "Radio frequency connectors; Part 8: R.F coaxial connectors with inner diameters of outer conductor 6,5 mm (0,256 in) with bayonet lock -Characteristic impedance 50 ohms (Type BNC)".

- [3] IEC 169-13 (1976): "Radio frequency connectors; Part 13: R.F. coaxial connectors with inner diameter of outer conductor 5,6 mm (0,22 in) Characteristic impedance 75 ohms (Type 1,6/5,6) Characteristic impedance 50 ohms (Type 1,8/5,6) with similar mating dimensions".

- [4] ISO/IEC 10173 (1991): "Information technology Integrated Services Digital Network (ISDN) primary access connector at reference points S and T".

- [5] ITU-T Recommendation G.703 (1991): "Physical/electrical characteristics of hierarchical digital interfaces".

- [6] ITU-T Recommendation O.151 (1992): "Error performance measuring equipment for digital systems at the primary rate and above".

- [7] ITU-T Recommendation O.171 (1992): "Timing jitter measuring equipment for digital systems".

- NOTE: This ETS also contains a number of informative references which have been included to indicate the sources from which various material has been derived, hence they do not have an associated normative reference number. Details of these publications are given in annex E. In some cases the same publication may have been referenced in both a normative and an informative manner.

## Page 8 Final draft prETS 300 689: October 1996

## 3 Definitions and abbreviations

For the purposes of this ETS, the following definitions apply:

#### 3.1 Definitions

**frame:** A repetitive set of consecutive bits in which the position of each bit can be identified by reference to a frame alignment signal.

frame alignment signal: The distinctive signal inserted in every frame always occupying the same relative position within the frame and used to establish and maintain frame alignment.

**leased lines:** The telecommunications facilities provided by a public telecommunications network that provide defined transmission characteristics between network termination points and that do not include switching functions that the user can control, (e.g. on-demand switching).

**Network Termination Point (NTP):** All physical connections and their technical access specifications which form part of the public telecommunications network and are necessary for access to and efficient communication through that public network.

**PRBS(2<sup>23-1</sup>):** A Pseudo Random Bit Sequence (PRBS) (as defined in subclause 2.2 of ITU-T Recommendation O.151 [6]).

**Safety Extra-Low Voltage (SELV) circuit:** A secondary circuit which is so designed and protected that under normal and single fault conditions, the voltage between any two accessible parts and, for class 1 equipment, between any accessible part and the equipment protective earthing terminal does not exceed a safe value (subclause 1.2.8.5 of EN 60950 [1]).

terminal equipment: Equipment intended to be connected to the public telecommunications network, i.e.:

- to be connected directly to the termination of a public telecommunication network; or

- to interwork with a public telecommunications network being connected directly or indirectly to the termination of a public telecommunications network,

in order to send, process, or receive information.

#### 3.2 Abbreviations

For the purposes of this ETS, the following abbreviations apply:

| MA<br>MSB | Maintenance and Adaptation<br>Most Significant Bit                                 |

|-----------|------------------------------------------------------------------------------------|

| NR        | Network operator byte                                                              |

| NTP       | Network Deration Byte                                                              |

| ONP       | Open Network Provision                                                             |

| ppm       | parts per million                                                                  |

| PRBS      | Pseudo Random Bit Sequence                                                         |

| RDI       | Remote Defect Indication                                                           |

| REI       | Remote Error Indication                                                            |

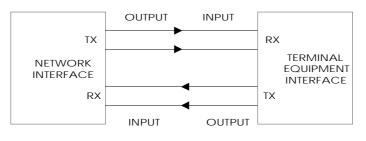

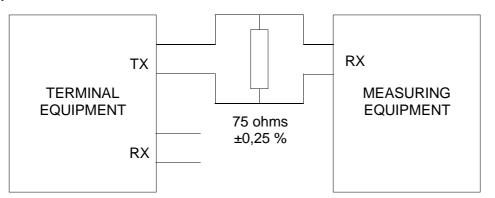

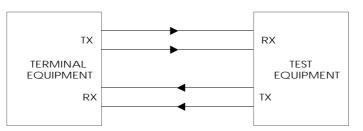

| RX        | RX is a signal input (at either the terminal equipment or the test equipment, see  |

|           | figure 1)                                                                          |

| SDH       | Synchronous Digital Hierarchy                                                      |

| SELV      | Safety Extra-Low Voltage                                                           |

| ТМ        | Timing Marker                                                                      |

| TU        | Tributary Unit                                                                     |

| TR        | TRail trace                                                                        |

| ТТІ       | Trail Trace Identifier                                                             |

| ТХ        | TX is a signal output (at either the terminal equipment or the test equipment, see |

|           | figure 1)                                                                          |

| UI        | Unit Interval                                                                      |

## 4 Requirements

The D34U 34 368 kbit/s unstructured leased line provides a bi-directional point-to-point digital leased line for the support of an unstructured 34 368 kbit/s information transfer rate. Any structuring of the data is the responsibility of the user.

The D34S 34 368 kbit/s structured leased line provides a bi-directional point-to-point digital leased line for the support of an unstructured 33 920 kbit/s information transfer rate. Any structuring of the data within the transparent 33 920 kbit/s part of the frame is the responsibility of the user.

For both D34U and D34S the provision of timing is the responsibility of the user; however, in certain installations the leased line provider may be able to offer a leased line that is synchronised to the network.

#### 4.1 Mechanical characteristics

The terminal equipment shall provide at least one of the methods of connection given in subclauses 4.1.1 and 4.1.2.

- NOTE 1: When connecting the terminal equipment to the NTP, any difference in ground potential between the two equipments may produce a voltage across the signal ground connection and may cause damage. See DEN/EE-02004 for details of earthing requirements within the customer's premises.

- NOTE 2: The transmit pair is the output from the terminal equipment interface. The receive pair is the input to the terminal equipment interface, as shown in figure 1. Where the terms "output" and "input" are used without qualification in this ETS, they refer to the terminal equipment interface.

- NOTE 3: Normal practice is for the outer conductors of the input and output connectors to be connected via a dc path to the signal ground and thence to ground. This connection is to reduce EMC emissions. If there is a difference in ground potential between the terminal equipment and the NTP, this arrangement may result in high currents in the outer conductors and cause damage.

To prevent this problem, dc isolation may be introduced between the terminal equipment and the NTP, for example by introducing dc isolation between the outer conductor and the signal ground in the terminal equipment. Careful attention should be given to the requirements of standards on installation earthing practice.

### Page 10 Final draft prETS 300 689: October 1996

Figure 1

#### 4.1.1 Sockets

**Requirement:** The terminal equipment interface shall provide two coaxial 75  $\Omega$  sockets, one each for transmit and receive; these sockets being either:

- a) 75  $\Omega$  sockets (type 1,6/5,6) complying with IEC 169-13 [3]; or

- b) 75  $\Omega$  BNC sockets complying with the general requirements of IEC 169-8 [2] with the mating dimensions specified in annex B of ISO/IEC 10173 [4].

The outer conductor of the coaxial pair shall be connected to signal ground both at the input port and at the output port.

**Test:** There shall be a visual inspection that the sockets are of the correct type.

#### 4.1.2 Plugs

**Requirement:** The terminal equipment interface shall provide two coaxial 75  $\Omega$  plugs at the end of a cord (or cords), one each for transmit and receive; these plugs being either:

- a) 75  $\Omega$  plugs (type 1,6/5,6) complying with IEC 169-13 [3]; or

- b) 75  $\Omega$  BNC plugs complying with the general requirements of IEC 169-8 [2] with the mating dimensions specified in annex B of ISO/IEC 10173 [4].

The outer conductor of the coaxial pair shall be connected to signal ground both at the input port and at the output port.

NOTE: There is no requirement on the method of connection of the cord (or cords) to the terminal equipment.

**Test:** There shall be a visual inspection that the plugs are of the correct type.

#### 4.2 Electrical characteristics

## 4.2.1 Output port

#### 4.2.1.1 Signal coding

**Requirement:** The signal transmitted at the output port shall comply with the High Density Bipolar code 3 (HDB3) encoding rules (see annex B).

**Test:** The test shall be conducted according to subclause A.2.1.

#### 4.2.1.2 Waveform shape

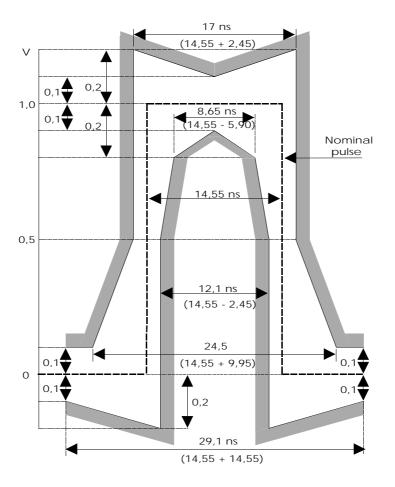

**Requirement:** The pulse at the output port shall comply with the requirements given in table 1 and figure 2; based on ITU-T Recommendation G.703.

| Pulse shape (nominally rectangular)                                                         | All marks of a valid signal shall conform with the mask (see figure 2). The value V corresponds to the |  |

|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|

|                                                                                             | nominal peak voltage of a mark.                                                                        |  |

| Test load impedance                                                                         | 75 $\Omega$ non-reactive                                                                               |  |

| Nominal peak voltage V of a mark                                                            | 1,0 V                                                                                                  |  |

| Peak voltage of a space                                                                     | 0 ± 0,1 V                                                                                              |  |

| Nominal pulse width                                                                         | 14,55 ns                                                                                               |  |

| Ratio of the amplitudes of positive and negative pulses at the centre of the pulse interval | 0,95 to 1,05                                                                                           |  |

| Ratio of the widths of positive and negative pulses at the nominal half amplitude           | 0,95 to 1,05                                                                                           |  |

#### Table 1: Waveform shape at output port

#### Figure 2: Pulse mask for 34 Mbit/s pulse

**Test:** The test shall be conducted according to subclause A.2.2.

#### 4.2.1.3 Output timing

The terminal equipment may derive its timing from:

- a) an internal source (e.g. an internal clock);

- b) an external reference signal input;

- c) the received signal at the input port.

**Requirement:** For each of the timing arrangements intended for use, the bit rate at the output port shall be within the limits of 34 368 kbit/s  $\pm$  20 parts per million (ppm), when any relevant external signal, including the received signal at the input port, is within its stated tolerance.

#### Page 12 Final draft prETS 300 689: October 1996

NOTE: The tolerance of  $\pm 20$  ppm relates to the transmission capability of the leased line. Tighter limits may be needed to ensure satisfactory end to end interworking with the distant terminal equipment.

**Test:** The test shall be conducted according to subclause A.2.3.

#### 4.2.1.4 Output return loss

**Requirement:** The output return loss at the terminal equipment interface, with respect to 75  $\Omega$ , shall be greater than or equal to the values given in table 2, which is taken from annex 3 of ETS 300 166.

#### Table 2: Output port minimum return loss

| Frequency range         | Return loss |  |

|-------------------------|-------------|--|

| 860 kHz to 1 720 kHz    | 6 dB        |  |

| 1 720 kHz to 51 550 kHz | 8 dB        |  |

**Test:** The test shall be conducted according to subclause A.2.6.

#### 4.2.1.5 Output jitter

**Requirement:** The peak-to-peak output jitter shall not exceed the limits of table 3 when measured with a bandpass filter with linear cut-off with the defined cut-off frequencies. At frequencies below the lower 3 dB point, the attenuation of the high pass filter shall rise with a value greater than, or equal to, 20 dB per decade. At frequencies above the upper 3 dB point, the attenuation of the low pass filtration shall rise with a value greater than, or equal to, 60 dB per decade.

For the purpose of testing, any signal input from which the output timing is derived shall be provided with the maximum tolerable input jitter, and with the maximum tolerable input frequency deviation, as specified by the manufacturer.

Where the output timing of the terminal equipment is taken from the leased line, the input to the terminal equipment shall be provided with components of sinusoidal jitter at points on the curve of figure 3 and table 5.

|                                                                                                                                 | Measurement f | Output jitter               |                                               |  |

|---------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------------|-----------------------------------------------|--|

| Lower cut-off<br>(high pass)                                                                                                    |               | Upper cut-off<br>(low pass) | Unit Interval (UI) peak-<br>to-peak (maximum) |  |

| 100 Hz                                                                                                                          |               | 800 kHz                     | 0,4                                           |  |

| 10 kHz                                                                                                                          |               | 800 kHz                     | 0,15                                          |  |

| NOTE: These values are chosen to allow for jitter build-up in user<br>networks and may be different from ITU-T Recommendations. |               |                             |                                               |  |

#### Table 3: Maximum output jitter

**Test:** The test shall be conducted according to subclause A.2.7.

#### 4.2.1.6 Output frame structure

The requirement of this subclause applies to terminal equipment for connection to the D34S leased line. For terminal equipments for connection to the D34U leased line, there is no requirement on the structure of the output bit stream.

**Requirement:** For terminal equipments for connection to the D34S leased line, the bit stream transmitted at the output of the terminal equipment shall be structured as defined in annex C.

Bit 1 of byte Maintenance and Adaptation (MA), a Remote Defect Indication (RDI), shall be set to "1" within 250  $\mu$ s of the detection of loss of received frame alignment (see subclause 4.2.2.8), and set to "0" within 250  $\mu$ s on gaining frame alignment.

Test: The test shall be conducted according to subclause A.2.8 and A.2.9.

#### 4.2.2 Input port

#### 4.2.2.1 Signal coding

**Requirement:** The input port shall decode without error HDB3 encoded signals in accordance with HDB3 encoding rules (see annex B).

**Test:** The test shall be conducted according to subclause A.2.4.

#### 4.2.2.2 Input return loss

**Requirement:** The input return loss with respect to 75  $\Omega$  at the interface shall be greater than or equal to the values given in table 4, which is taken from subclause 8.3.3 of ITU-T Recommendation G.703.

#### Table 4: Input port minimum return loss

| Frequency range          | Return loss |  |

|--------------------------|-------------|--|

| 860 kHz to 1 720 kHz     | 12 dB       |  |

| 1 720 kHz to 34 368 kHz  | 18 dB       |  |

| 34 368 kHz to 51 550 kHz | 14 dB       |  |

**Test:** The test shall be conducted according to subclause A.2.5.

#### 4.2.2.3 Input loss tolerance

**Requirement:** The input port shall decode without errors a 34 368 kbit/s signal as defined in subclauses 4.2.1.1 and 4.2.1.2 above but modified by a cable or artificial cable with the following characteristics:

- a) attenuation that follows a  $\sqrt{f}$  law with values throughout the range 0 dB to 12 dB at 17 184 kHz; and

- b) characteristic impedance of 75  $\Omega$  with a tolerance of ± 20 % over the frequency range from 860 kHz to 51 550 kHz.

**Test:** The test shall be conducted according to subclause A.2.4.

#### 4.2.2.4 Immunity against reflections

**Requirement:** When a signal comprising a combination of a normal signal and an interfering signal is applied to the input port, via an artificial cable with a loss in the range 0 dB to 12 dB at 17 184 kHz, no errors shall result due to the interfering signal. The normal signal shall be a signal encoded according to HDB3, shaped according to the mask of figure 2, with a binary content in accordance with a PRBS( $2^{23-1}$ ). The interfering signal shall be the same as the normal signal except that the level shall be attenuated by 20 dB, the bit rate shall be within 34 368 kbit/s ± 20 ppm and the timing shall not be synchronised to the normal signal.

**Test:** The test shall be conducted according to subclause A.2.4.

#### 4.2.2.5 Input jitter tolerance

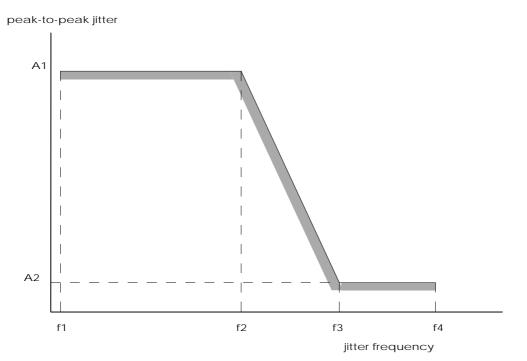

**Requirement:** The terminal equipment shall tolerate at its input port the maximum input jitter as shown in figure 3 and table 5 (taken from ITU-T Recommendation G.823).

NOTE: Terminal equipment with more than one input will normally need to be designed with a wander buffer of at least 18 microseconds, however, to accommodate the wander that may be produced by Synchronous Digital Hierarchy (SDH) networks, up to 40 microseconds may be needed.

## Page 14 Final draft prETS 300 689: October 1996

Figure 3: Input jitter tolerance

Table 5: Input jitter tolerance

| Peak-to-peak amplitude (UI) |      | Frequency |       |        |         |

|-----------------------------|------|-----------|-------|--------|---------|

| A1                          | A2   | f1        | f2    | f3     | f4      |

| 1,5                         | 0,15 | 100 Hz    | 1 kHz | 10 kHz | 800 kHz |

Test: The test shall be conducted according to subclause A.2.7.

#### 4.2.2.6 Input clock tolerance

**Requirement:** The terminal equipment shall decode without error HDB3 encoded signals, as defined in annex B, for all bit rates within the limits of 34 368 kbit/s ± 20 ppm.

Test: The test shall be conducted according to subclause A.2.7.

#### 4.2.2.7 Input frame structure

The requirement of this subclause applies to terminal equipment for connection to the D34S leased line. For terminal equipments for connection to the D34U leased line, there is no requirement on the structure of the input bit stream.

**Requirement:** The input port shall accept an input bit stream with a frame structure as defined in annex C. The terminal equipment shall be capable of achieving frame alignment, as detailed in subclause 4.2.2.8, in order to separate the user data from the frame information.

**Test:** The test shall be conducted according to subclause A.2.4.

#### 4.2.2.8 Frame alignment procedure

The requirement of this subclause applies to terminal equipment for connection to the D34S leased line. For terminal equipments for connection to the D34U leased line, there is no requirement on the frame alignment procedure.

**Requirement:** The terminal equipment shall perform a frame alignment procedure on the 34 368 kbit/s signal in order to gain or to recover frame alignment. To obtain frame alignment, the terminal equipment shall search for the FA1, FA2 bytes contained within the received bit stream. Frame alignment shall be continuously checked with the presumed frame start position for the correct frame alignment.

Frame alignment shall be considered to have been obtained, or recovered, when three consecutive non-errored frame alignment signals (FA1 and FA2) have been found.

Frame alignment shall be considered to have been lost when either:

- a) four consecutive frame alignment signals (FA1 and FA2) are detected in error (i.e. ≥ 1 error in each FA1 and FA2); or

- b) 986 or more frames with one or more BIP-8 violations are detected in a block of 1 000 frames.

When frame alignment is achieved, even bit parity (BIP-8) shall be computed by the terminal equipment for each bit n of every byte of the preceding frame and compared with bit n of the EM byte recovered from the current frame. A difference between the computed BIP-8 and the EM value shall be taken as evidence of one or more errors in the previous frame.

Should a research for frame alignment be initiated for any reason, then the new search for frame alignment should start 1 bit displaced forward from the position of the last indication of frame alignment.

NOTE: The above is recommended in order to avoid repeated alignment on to a simulation of the framing location.

**Test:** The test shall be conducted according to subclause A.2.9.

#### 4.3 Safety

**Requirement:** The terminal equipment interface shall comply with the requirements for accessible parts of an SELV circuit.

Test: The test shall be conducted according to EN 60950 [1].

#### 4.4 Overvoltage protection

There are no overvoltage protection requirements under this ETS.

- NOTE 1: Requirements for overvoltage protection requirements on a 75  $\Omega$  interface are under study. Requirements may be added to this ETS when appropriate specifications become available.

- NOTE 2: If the cables between the NTP and the terminal equipment leave the building, additional protection may be required as detailed in draft IEC 801-5, with a test level of 4,0 kV, applying failure criteria A from clause 7 of ITU-T Recommendation K.20.

#### 4.5 ElectroMagnetic Compatibility (EMC)

There are no EMC requirements under this ETS.

NOTE: General EMC requirements are imposed under the EMC Directive (89/336/EEC). Requirements for conducted emissions and immunity to continuous conducted signals will be added to this ETS when appropriate specifications become available if these requirements are not imposed under the EMC Directive.

## Annex A (normative): Test methods

## A.1 General

This annex describes the test principles to determine the compliance of a terminal equipment against the requirements of this ETS.

It is outside the scope of this annex to identify the specific details of the implementation of the tests.

A terminal equipment may be designed for through-connecting and may fulfil the electrical requirements only if through-connected. In these cases the requirements of this ETS are valid and the tests shall be carried out with the through-connection terminated as specified by the manufacturer.

Details of test equipment accuracy and the specification tolerance of the test devices are not included in all cases. Where such details are provided they shall be complied with, but the way they are expressed shall not constrain the method of implementing the test.

NOTE: Attention is drawn to the issue of measurement uncertainty which may be addressed in future documents. Not all the required test results make allowance for spurious events during testing (e.g. errors due to EMC effects), which may make it necessary to repeat a test.

The test configurations given do not imply a specific realisation of test equipment or test arrangement, or the use of specific test devices for conformance testing. However, any test configuration used shall provide those test conditions specified under "interface state", "stimulus" and "monitor" for each individual test.

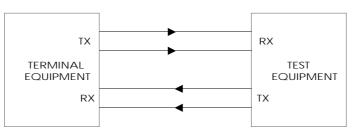

The test equipment shall be a device, or a group of devices, that is capable of generating a stimulus signal conforming to this ETS and capable of monitoring the signal received from the interface.

#### A.1.1 Additional information to support the test

The following facilities shall be provided by the terminal equipment interface under test:

- a) an ability to configure the terminal equipment such that it provides a transparent loopback of the data contained within the payload at the input to the output; and

- b) an ability to transmit a given bit pattern, e.g. PRBS(2<sup>23-1</sup>), within the payload;

or

- c) where a or b cannot be provided, an alternative means of performing the test.

- NOTE: Where the terminal equipment is for connection to the D34S leased line, the REI bit may be used as an alternative to a transparent loopback in order to determine if data at the input has been correctly received.

#### A.1.2 Equipment connection

The tests shall be applied at the sockets or plugs defined in subclauses 4.1.1 and 4.1.2. Connecting cable between the sockets and test equipment shall be kept to a minimum, except where cable is specified as part of the test.

Where plugs are provided at the end of a cord as defined in subclause 4.1.2, the tests specified in subclauses A.2.2, A.2.5 and A.2.6 may be performed at the point of connection of the cord to the terminal equipment, since the requirements are based on ITU-T Recommendation G.703 which makes no allowance for any plug and cord.

## A.2 Test methods

One test may cover more than one requirement. The scope of each test is defined under the heading "purpose".

#### A.2.1 Signal coding at the output port

Purpose:

To verify that the signal coding at the terminal equipment output port complies with the HDB3 coding rules as required by subclause 4.2.1.1.

**Test configuration:** Figure A.1.

#### Figure A.1: Signal coding at output port

Interface state: Powered.

Stimulus: The terminal equipment shall transmit a bit stream including the sequences <0000><even number of binary ONEs><0000> and <0000><odd number of binary ONEs><0000> which shall be encoded into HDB3; where 0 = space and 1 = mark input to the HDB3 encoder, (see note).

- NOTE: A pseudo random bit stream, e.g. PRBS(2<sup>23-1</sup>), will be acceptable if the bit patterns of the above subclause are included in the bit stream. For terminal equipment which can generate a structured signal in accordance with annex C, the PRBS may be transmitted in the payload section of the frame. For terminal equipment which cannot generate such a structured signal, the PRBS should be transmitted in the whole bit stream.

- Monitor: The output bit stream for a test period of sufficient time to allow transmission of 100 occurrences of the above patterns plus the latency period of the error detection mechanism.

**Results:** There shall be no errors in the HDB3 encoding.

#### A.2.2 Waveform shape at the output port

- **Purpose:** To verify conformance of the output waveform shape with the requirements of subclause 4.2.1.2.

- **Test configuration:** Figure A.2.

#### Page 18 Final draft prETS 300 689: October 1996

Figure A.2: Waveform shape at output port

| Interface state: | Powered. |

|------------------|----------|

| interrace state. | Fowered. |

Stimulus: Undefined.

**Monitor:** Marks and spaces transmitted from the terminal equipment, measuring the amplitude and shape of positive and negative pulses (measured at the centre of the pulse interval) and the time duration of positive and negative pulses (measured at the nominal half of the pulse amplitude, i.e. 0,5 V).

The overall measurement accuracy shall be better than 30 mV. All the measurements shall be performed using measuring equipment capable of recording dc. A bandwidth of 200 MHz or greater shall be used to ensure the capture of over or undershoot of the pulse.

**Results:** Both positive and negative pulses shall be within the mask of figure 2, where the nominal pulse amplitude is 1 V.

The bit interval corresponding to a space shall not present voltages higher than  $\pm 0.1$  V.

The ratio between the amplitude of positive and negative pulses shall be in the range from 0,95 to 1,05.

The ratio between the pulse widths of positive and negative pulses shall be in the range from 0,95 to 1,05.

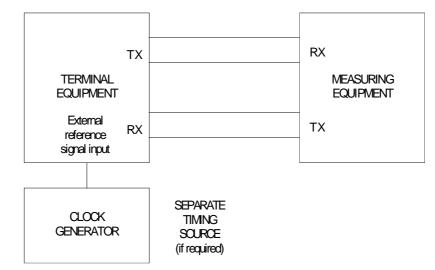

#### A.2.3 Output timing

**Purpose:** To measure the output timing as defined in subclause 4.2.1.3.

**Test Configuration:** Figure A.3.

Figure A.3: Output timing

Interface state: Powered.

**Stimulus:** The terminal equipment shall be configured to provide output timing from each of its intended timing arrangements. Any external reference signal input, including the input port, from which timing can be derived, shall be provided with timing at the bit rate limits as specified by the terminal equipment manufacturer.

Monitor: The bit rate of the signal decoded from output port of the terminal equipment.

**Results:** The bit rate shall be within the limits given in subclause 4.2.1.3.

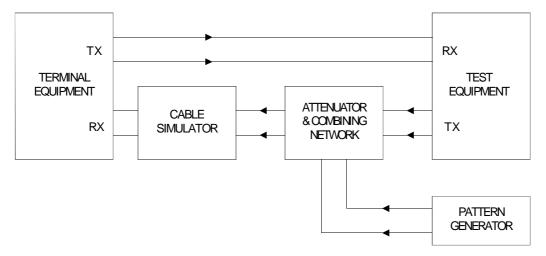

#### A.2.4 Input signal coding, loss tolerance and immunity against reflections

- **Purpose:** To verify the input port signal coding (subclause 4.2.2.1) and immunity against an interfering signal combined with the input signal, (subclause 4.2.2.4), both without cable (i.e. 0 dB attenuation loss) and with a cable attenuation of 12 dB (subclause 4.2.2.3).

- Test configuration: Figure A.4.

The interfering signal shall be combined with the main signal in a combining network of impedance 75  $\Omega$ , with zero dB loss in the main path and an attenuation in the interference path of 20 dB.

The cable simulator shall have an attenuation of 12 dB measured at 17 184 kHz and an attenuation characteristic that follows a  $\sqrt{f}$  law over the frequency range 860 kHz to 51 550 kHz.

The conformance of the interface shall be verified in the following test conditions:

- a) without cable simulator and without interfering signal; and

- b) with cable simulator and without interfering signal; and

- c) without cable simulator and with interfering signal; and

- d) with cable simulator and with interfering signal.

#### Page 20 Final draft prETS 300 689: October 1996

#### Figure A.4: Input coding, loss tolerance and immunity against reflections

Interface state: Powered, with received data looped back to the output port.

**Stimulus:** The output signal of the test equipment shall be HDB3 encoded and conform to a pulse shape as defined in figure 17 of ITU-T Recommendation G.703 [5], which is reproduced in figure 2 of this ETS. For terminal equipment which can generate a structured signal in accordance with annex C, the bit stream shall be structured into frames according to annex C. The binary content of the data contained in the payload of the frame shall be a PRBS(2<sup>23-1</sup>). For terminal equipment which cannot generate such a structured signal, the PRBS should be transmitted in the whole bit stream.

The bit rate shall be within the limits 34 368 kbit/s  $\pm$  20 ppm.

The interfering signal from the pattern generator shall:

- a) be HDB3 encoded and conform to a pulse shape as defined in figure 17 of ITU-T Recommendation G.703 [5], which is reproduced in figure 2 of this ETS; and

- b) have a binary content with a  $PRBS(2^{23-1})$ ; and

- c) have a nominal bit rate of 34 368 kbit/s, not synchronised to the output signal of the test equipment.

Monitor: Data at the output port of the terminal equipment.

**Results:** There shall be no bit errors for at least one minute.

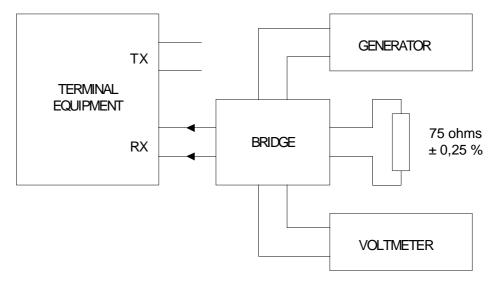

- A.2.5 Input return loss

- **Purpose:** To verify the return loss of the input port of the terminal equipment complies with the requirement of subclause 4.2.2.2.

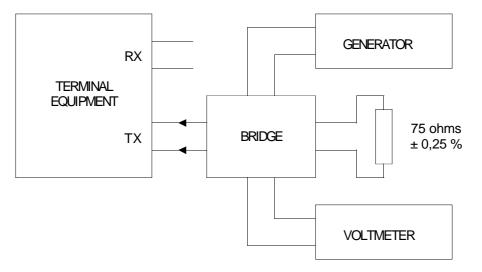

**Test configuration:** Figure A.5.

#### Page 21 Final draft prETS 300 689: October 1996

Figure A.5: Return loss at input port

Interface state: Powered.

Stimulus:Sinusoidal signal of 1 V peak applied to the input of the terminal equipment with<br/>a frequency variable between the limits of 860 kHz and 51 550 kHz.

**Monitor:** Voltage measured across the bridge, representing a terminating resistor of 75  $\Omega$  using a selective voltmeter with a bandwidth of less than 10 kHz.

**Results:** The measured return loss shall be greater than or equal to the values specified in subclause 4.2.2.2.

- NOTE 1: The characteristics of the generator and of the voltmeter may be different depending on the implementation of the bridge, however the total error of the test set-up should be less than 0,5 dB in the range between 10 dB and 20 dB. When connected to a 75  $\Omega$  $\pm$  0,25 % resistor, the measured return loss of the bridge should be 20 dB higher than the limits specified for the interface.

- NOTE 2: Where the generator and voltmeter are implemented by means of a network analyser, a measurement bandwidth of 100 Hz and a sweep time of 10 s is recommended.

#### A.2.6 Output return loss

**Purpose:** To verify the return loss of the output port of the terminal equipment complies with the requirement of subclause 4.2.1.4.

Test configuration: Figure A.6.

Interface state: Powered.

## Page 22 Final draft prETS 300 689: October 1996

Figure A.6: Return loss at output port

Stimulus: Sinusoidal signal of 1 V peak applied to the output of the terminal equipment interface with a frequency variable between the limits of 860 kHz and 51 550 kHz.

The output return loss shall be measured under dynamic conditions with a PRBS(2<sup>23-1</sup>) transmitted at the output. For a terminal equipment which can generate a structured signal in accordance with this ETS, the PRBS may be transmitted in the payload section of the frame. For a terminal equipment which cannot generate such a structured signal, the PRBS should be transmitted in the whole bit stream.

## Monitor:Voltage measured across the bridge, representing a terminating resistor of 75 $\Omega$ <br/>using a selective voltmeter with a bandwidth of less than 10 kHz.

## **Results:** The measured return loss shall be greater than or equal to the values specified in subclause 4.2.1.4.

- NOTE 1: The characteristics of the generator and of the voltmeter may be different depending on the implementation of the bridge however the total error of the test set-up should be less than 0,5 dB in the range between 10 dB and 20 dB. When connected to a 75  $\Omega$  $\pm$  0,25 % resistor the measured return loss of the bridge should be 20 dB higher than the limits specified for the interface.

- NOTE 2: Where the generator and voltmeter are implemented by means of a network analyser, a measurement bandwidth of 100 Hz and a sweep time of 10 s is recommended to restrict the influence of the output signal on the test result.

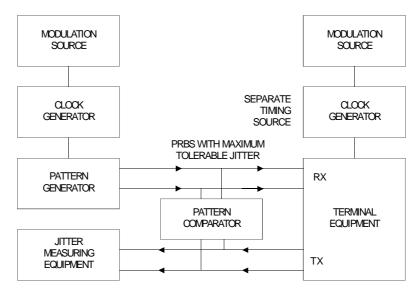

#### A.2.7 Input and output jitter

- **Purpose:** To measure tolerance to input jitter (subclause 4.2.2.5), maximum output jitter (subclause 4.2.1.5) and operation over the specified input timing range (subclause 4.2.2.6).

- NOTE: Further information on the measurement of jitter can be found in CCITT Supplement number 3.8, Fascicle IV.4 (1988).

#### Test Configuration: Figure A.7.

The terminal equipment shall be tested in each of the following configurations (where these modes of operation are supported):

a) output timing referenced to the internal clock; and

b) output timing referenced to any external clock source from which timing can be derived (including derivation from the input signal).

NOTE: The modulation source may be included in the clock generator and/or the pattern generator, or it may be provided separately.

#### Figure A.7: Jitter measurement

**Interface state:** Powered, with received data looped back to the output port.

**Stimulus:** The output signal of the test equipment shall be HDB3 encoded and conform to a pulse shape as defined in figure 17 of ITU-T Recommendation G.703 [5], which is reproduced in figure 2 of this ETS. For terminal equipment which can accept a structured signal in accordance with annex C, the bit stream shall be structured into frames according to annex C. The binary content of the data contained in the payload of the frame shall be a PRBS(2<sup>23-1</sup>). For terminal equipment which cannot accept such a structured signal, the PRBS should be transmitted in the whole bit stream.

Measurements shall be made with both the input signals at the digital rate limits of 34 368 kbit/s  $\pm$  20 ppm and between these limits, sufficient to verify jitter compliance over the specified frequency range. As a minimum the test shall be performed at the upper and lower limits and at the nominal rate.

The modulation source for the terminal equipment input bit stream shall generate individual components of sinusoidal jitter at points on the curve of figure 3 and table 4 of this ETS.

The modulation source for the external timing (if needed) shall be independent from that for the input signal and shall generate the maximum tolerable jitter, and maximum frequency deviation, as specified by the manufacturer of the terminal equipment.

It may be necessary to synchronise the two clock generators to avoid a high occurrence of slips.

- Monitor: a) The signal transmitted by the terminal equipment; and

- b) the jitter extracted from this signal using equipment complying with ITU-T Recommendation 0.171 [7].

- Results: a) There shall be no bit errors reported by the test equipment within the period of the test; and

#### Page 24 Final draft prETS 300 689: October 1996

b) the peak-to-peak jitter shall comply with the requirements of subclause 4.2.1.5.

#### A.2.8 Frame structure

**Purpose:** To verify compliance with the requirements for terminal equipment output structure defined in subclause 4.2.1.6. The test verifies the presence of the frame alignment signals (FA1 and FA2), the BIP-8, trail trace, MA byte (RDI, REI, payload type, payload dep and TM) and the general purpose communications channel.

**Test configuration:** See figure A.8.

#### Figure A.8: Structure

Interface state: Powered.

**Stimulus:** The following HDB3 encoded stimuli shall be applied to the input of the terminal equipment at a bit rate within the limits of 34 368 kbit/s ± 20 ppm:

- a) a bit stream structured in accordance with annex C;

- b) a bit stream structured in accordance with annex C, with bit errors introduced in the payload following calculation of the BIP-8;

- c) a continuous all one signal (AIS);

- d) no signal (input disconnected);

- e) a continuous  $PRBS(2^{23-1})$  with no frame structure.

Monitor: The bit stream at the output of the terminal equipment.

**Results:** The output bit stream shall comprise frames of octets commencing with the two octets FA1 and FA2 as defined in annex C.

- a) The BIP-8 contained in the EM byte shall correspond to the previous frame in accordance with the requirements of annex C; RDI = 0; REI = 0; the trail trace byte, payload type, payload dependent bits and TM shall be as declared by the terminal equipment manufacturer;

- b) REI shall be set to 1 for a period of 1 frame, for each frame received where the BIP-8 does not correspond with the data;

- c) RDI = 1;

- d) RDI = 1;

- e) RDI = 1.

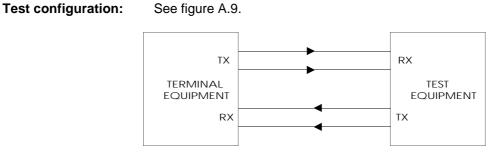

#### A.2.9 Frame alignment procedure

**Purpose:** To verify the compliance with the requirements for frame alignment procedure (see subclause 4.2.2.8). The test verifies the detection of loss of frame and regaining of frame and the associated setting of the RDI (see subclause 4.2.1.6).

Figure A.9: Frame alignment

Interface state: Powered.

Stimulus:

The following HDB3 encoded signal shall be applied to the input of the terminal equipment at a bit rate within the limits of 34 368 kbit/s  $\pm$  20 ppm. The bit stream shall be structured in accordance with annex C but with the following modification of the frame alignment word and the EM byte.

#### Table A.1: Frame alignment procedure

| Stimulus                                                 | Result | Comment             |  |  |

|----------------------------------------------------------|--------|---------------------|--|--|

| FFFFFF                                                   | RDI=0  | correct FAS         |  |  |

| FFFF/F/F/F/FFF                                           | RDI=0  | 3 incorrect FAS     |  |  |

| FFFFN*(/F/F/F/FFF)                                       | RDI=1  | 4 incorrect FAS     |  |  |

| /F /F /F /F F F F                                        | RDI=0  |                     |  |  |

| /FFF/F                                                   | RDI=0  |                     |  |  |

| FFFF                                                     | RDI=0  |                     |  |  |

| 985 BIP-8 errors in 1 000 frames                         | RDI=0  |                     |  |  |

| 986 BIP-8 errors in 1 000 frames                         | RDI=1  |                     |  |  |

| FFFF                                                     | RDI=0  |                     |  |  |

| /F /F /F /F                                              | RDI=1  | New FAS should be   |  |  |

| Simulated FA1, FA2 and correct BIP-8 in                  |        | searched with 1 bit |  |  |

| the payload.                                             | RDI=0  | offset.             |  |  |

| After locking of simulated frame consecutive             |        |                     |  |  |

| F and EM, 986 incorrect BIP-8 in the                     |        |                     |  |  |

| payload                                                  | RDI=1  |                     |  |  |

| FFFF                                                     | RDI=0  |                     |  |  |

| NOTE: F = correct frame alignment signal                 |        |                     |  |  |

| /F = incorrect frame alignment signal                    |        |                     |  |  |

| N* = repeat continuously N times (where N is an integer) |        |                     |  |  |

#### Monitor: The RDI signal at the output port

Result:

The setting of the RDI shall conform to column 2 of table A.1.

## Annex B (normative): Definition of HDB3 code

## B.1 General

This annex specifies the modified Alternate Mark Inversion (AMI) code HDB3. The contents of this annex are based on annex A of ITU-T Recommendation G.703.

In this code, binary 1 bits are represented by alternate positive and negative pulses, and binary 0 bits by spaces. Exceptions are made when strings of successive 0 bits occur in the binary signal.

In the definition below, B represents an inserted pulse corresponding to the AMI rule, and V represents an AMI violation.

## B.2 Definition

Each block of 4 successive zeros is replaced by 000V or B00V. The choice of 000V or B00V is made so that the number of B pulses between consecutive V pulses is odd. In other words, successive V pulses are of alternate polarity so that no dc component is introduced.

## Annex C (normative): Definition of frame structure

## C.1 Frame structure at 34 368 kbit/s

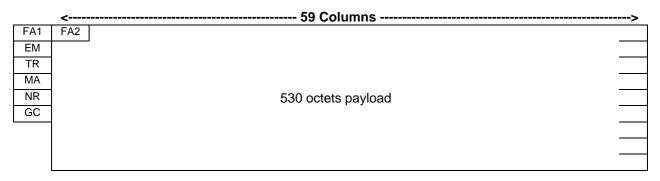

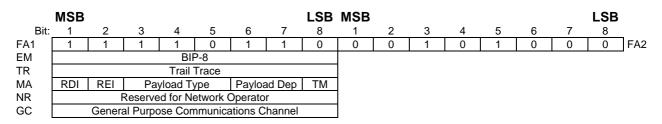

The basic frame structure at 34 368 kbit/s for the D34S leased line shall comprise 7 octets of generic path overhead and 530 octets of payload capacity; this is defined in figures C.1 and C.2. The order of transmission of information in figure C.1 is first from left to right and then top to bottom. Within each byte the most significant bit is transmitted first. The most significant bit (bit 1) is illustrated at the left of figure C.2.

#### Figure C.1: Frame structure at 34 368 kbit/s

#### Figure C.2: Path overhead at 34 368 kbit/s

- MSB Most Significant Bit.

- LSB Least Significant Bit.

- FA1 Frame Alignment byte (1).

- FA2 Frame Alignment byte (2).

- EM Error Monitoring, Bit Interleaved Parity 8 (BIP-8). One byte is allocated for path error monitoring. This function shall be a BIP-8 code using even parity. The path BIP-8 is calculated over all bits of the previous 125 μs frame. The computed BIP-8 is placed in the EM byte of the current 125 μs frame.

- TR TRail trace. This byte is used to transmit repetitively a trail access point identifier so that a trail receiving terminal can verify its continued connection to the intended transmitter. See subclause C.1.1.

- MA Maintenance and Adaptation Byte:

Bit 1 RDI Remote Defect Indication: this bit is set to "1" under the following conditions:

- a) invalid input signal or loss of signal (LOS);

- b) loss of frame alignment (LOF) see note 1; or

- c) alarm indication signal (AIS);

and is otherwise set to "0".

## Page 28 Final draft prETS 300 689: October 1996

NOTE 1: RDI may also be set in the event of a trail trace mismatch.

Bit 2 REI Remote Error Indication: this bit is set to "1" and sent back to the remote path termination if one or more errors were detected by the BIP-8, and is otherwise set to "0".

Bits 3 - 5 Payload type: these bits are set as shown in table C.1.

| Code | Signal                 |  |  |  |

|------|------------------------|--|--|--|

| 000  | Unequipped             |  |  |  |

| 001  | Equipped, non-specific |  |  |  |

| 010  | ATM                    |  |  |  |

| 011  | SDH TU-12s             |  |  |  |

#### Table C.1: Payload type

Bits 6 - 7 Payload dependent: e.g. Tributary Unit (TU) multiframe indicator.

NOTE 2: Further information on the multiplexing of SDH elements within the payload and the use of the payload dependent bits is given in ETS 300 337.

Bit 8 TM Timing Marker: this bit is set to "0" to indicate that the timing source is traceable to a primary reference clock and is otherwise set to "1".

NR Network operator byte. This byte is undefined for terminal equipments.

NOTE 3: This byte is allocated for maintenance purposes specific to individual network operators. Its transparency from NTP to NTP is not guaranteed.

- GC General purpose Communications channel (e.g. to provide data/voice channel connection for maintenance purposes). The specific use of this byte is undefined within this ETS.

- NOTE 4: This byte is allocated for the specific use of the terminal equipment user. Its transparency from NTP to NTP is guaranteed.

- NOTE 5: The specific use of this byte is under study within other ETSI Technical Committees.

#### C.1.1 Trail access point identifier format

The trail access point identifier shall use the 16-byte numbering format described below.

The first byte of the string is a frame start marker and includes the result of a Cyclic Redundancy Check (CRC-7) calculation over the previous frame. The following 15 bytes are used for the transport of 15 American Standard Code for Information Interchange (ASCII) characters supplied by the leased line provider for each leased line. This code will be different in each direction of transmission.

NOTE: The ASCII code is specified in ITU-T Recommendation T.50.

The 16-byte frame is defined in figure C.3.

| Byte 1                            | 1 | C <sub>1</sub> | $C_2$ | C <sub>3</sub> | C₄ | C <sub>5</sub> | C <sub>6</sub> | C <sub>7</sub> |

|-----------------------------------|---|----------------|-------|----------------|----|----------------|----------------|----------------|

| <b>Byte 1</b><br>Byte 2<br>Byte 3 | 0 | Х              | Х     | Х              | Х  | Х              | Х              | Х              |

| Byte 3                            | 0 | Х              | Х     | Х              | Х  | Х              | Х              | Х              |

|                                   |   |                |       |                |    |                |                |                |

| Byte 16                           | 0 | Х              | Х     | Х              | Х  | Х              | Х              | Х              |

| 0                                 |   |                |       |                |    |                |                |                |

C<sub>1</sub> --- C<sub>7</sub> 0XXXXXXX Result of the CRC-7 calculation over the previous frame ASCII Character

Frame start marker

#### Figure C.3: 16-byte frame

The description of the CRC-7 calculation is given below.

#### C.1.1.1 CRC-7 calculation - multiplication and division process

A particular CRC-7 word is the remainder after multiplication by  $x^7$  and then division (modulo 2) by the generator polynomial  $x^7 + x^3 + 1$ , of the polynomial representation of the previous Trail Trace Identifier (TTI) multiframe.

When representing the contents of the block as a polynomial, the first bit in the block (i.e. byte 1 bit 1) shall be taken as being the MSB. Similarly,  $C_1$  is defined to be the MSB of the remainder and  $C_7$  to be the LSB of the remainder.

#### C.1.1.2 CRC-7 calculation - encoding procedure

Contrary to e.g. CRC-4 procedure in a 2 048 kbit/s signal, the CRC-7 word is static because the data is static (the TTI represents the source address). This means that the CRC-7 checksum can be calculated a priori over the TTI multiframe. For consistency with existing Recommendations, the CRC-7 shall be calculated over the previous multiframe. In theory this means that the 16-byte string that is loaded in a device for repetition transmission should have the checksum as the last byte, although in practice it does not really matter, because the TTI is static.

The encoding procedure is as follows:

- a) the CRC-9 bits in the TTI are replaced by binary 0 s;

- b) the TTI is then acted upon by the multiplication/division process referred to above;

- c) the remainder resulting from the multiplication/division process is inserted into the CRC-7 location.

The CRC-9 bits generated do not affect the result of the multiplication/division process because, as indicated in a) above, the CRC-9 bit positions are initially set to 0 during the multiplication/division process.

#### C.1.1.3 CRC-7 calculation - decoding procedure

The decoding procedure is as follows:

- a) a received TTI is acted upon by the multiplication/division process referred to above after having its CRC-9 bits extracted and replaced by binary 0 s;

- b) the remainder resulting from the multiplication/division process is then compared on a bit-by-bit basis with the CRC-9 bits received;

- c) if the remainder calculated in the decoder exactly corresponds to the CRC-9 bits received, it is assumed that the checked TTI is error free.

## Annex D (normative): ETS Requirements Table (ETS-RT)

Notwithstanding the provisions of the copyright clause related to the text of this ETS, ETSI grants that users of this ETS may freely reproduce the ETS-RT proforma in this annex so that it can be used for its intended purposes and may further publish the completed ETS-RT.

## Table D.1: ETS conditions table for attachment requirements for terminal equipment to digital34 Mbit/s leased lines (D34U and D34S) as given in ETS 300 689

| Reference | Condition |                                     |          | Status    | Support (Y/N) |     |               |  |

|-----------|-----------|-------------------------------------|----------|-----------|---------------|-----|---------------|--|

| C.1       | ls †      | the                                 | terminal | equipment | intended      | for | If YES then M |  |

|           | con       | connection to the D34S leased line? |          |           |               |     | else N        |  |

## Table D.2: ETS-RT for attachment requirements for terminal equipment to digital 34 Mbit/s leased lines (D34U and D34S) as given in ETS 300 689

| ETS Reference |                                                               | ETS 300 689                                                                                                                                                                                                                                                                |                                                                |                                           |  |  |  |  |  |

|---------------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------|--|--|--|--|--|

| ltem          | Reference                                                     | Requirement                                                                                                                                                                                                                                                                | Status<br>(note 1)                                             | Support<br>(note 2)                       |  |  |  |  |  |

| 1             | 4.1.1                                                         | Sockets                                                                                                                                                                                                                                                                    | 0.1                                                            |                                           |  |  |  |  |  |

| 2             | 4.1.2                                                         | Plugs                                                                                                                                                                                                                                                                      | 0.1                                                            |                                           |  |  |  |  |  |

| 3             | 4.2.1.1                                                       | Signal coding                                                                                                                                                                                                                                                              | М                                                              |                                           |  |  |  |  |  |

| 4             | 4.2.1.2                                                       | Waveform shape                                                                                                                                                                                                                                                             | М                                                              |                                           |  |  |  |  |  |

| 5             | 4.2.1.3                                                       | Output timing                                                                                                                                                                                                                                                              | М                                                              |                                           |  |  |  |  |  |

| 6             | 4.2.1.3 (a)                                                   | - internal source of timing                                                                                                                                                                                                                                                | 0                                                              |                                           |  |  |  |  |  |

| 7             | 4.2.1.3 (b)                                                   | - external timing reference (note 3)                                                                                                                                                                                                                                       | 0                                                              |                                           |  |  |  |  |  |

| 8             | 4.2.1.3 (c)                                                   | - timing derived from input port                                                                                                                                                                                                                                           | 0                                                              |                                           |  |  |  |  |  |

| 9             | 4.2.1.4                                                       | Output return loss                                                                                                                                                                                                                                                         | М                                                              |                                           |  |  |  |  |  |

| 10            | 4.2.1.5                                                       | Output jitter                                                                                                                                                                                                                                                              | М                                                              |                                           |  |  |  |  |  |

| 11            | 4.2.1.6                                                       | Output frame structure                                                                                                                                                                                                                                                     | C.1                                                            |                                           |  |  |  |  |  |

| 12            | 4.2.2.1                                                       | Signal coding                                                                                                                                                                                                                                                              | М                                                              |                                           |  |  |  |  |  |

| 13            | 4.2.2.2                                                       | Input return loss                                                                                                                                                                                                                                                          | М                                                              |                                           |  |  |  |  |  |

| 14            | 4.2.2.3                                                       | Input loss tolerance                                                                                                                                                                                                                                                       | М                                                              |                                           |  |  |  |  |  |

| 15            | 4.2.2.4                                                       | Immunity against reflections                                                                                                                                                                                                                                               | М                                                              |                                           |  |  |  |  |  |

| 16            | 4.2.2.5                                                       | Input jitter tolerance                                                                                                                                                                                                                                                     | М                                                              |                                           |  |  |  |  |  |

| 17            | 4.2.2.6                                                       | Input clock tolerance                                                                                                                                                                                                                                                      | М                                                              |                                           |  |  |  |  |  |

| 18            | 4.2.2.7                                                       | Input frame structure                                                                                                                                                                                                                                                      | C.1                                                            |                                           |  |  |  |  |  |

| 19            | 4.2.2.8                                                       | Frame alignment procedure                                                                                                                                                                                                                                                  | C.1                                                            |                                           |  |  |  |  |  |

| 20            | 4.3                                                           | Safety                                                                                                                                                                                                                                                                     | М                                                              |                                           |  |  |  |  |  |

| 21            | 4.4                                                           | Overvoltage protection                                                                                                                                                                                                                                                     | N                                                              |                                           |  |  |  |  |  |