ETSI Standard

## Dynamic synchronous Transfer Mode (DTM); Part 6: Mapping of Synchronous Digital Hierarchy (SDH) over DTM

### Reference

#### RES/TISPAN-02017-DTM

Keywords

DTM, protocol, SDH, switching, transmission

#### **ETSI**

650 Route des Lucioles F-06921 Sophia Antipolis Cedex - FRANCE

Tel.: +33 4 92 94 42 00 Fax: +33 4 93 65 47 16

Siret N° 348 623 562 00017 - NAF 742 C Association à but non lucratif enregistrée à la Sous-Préfecture de Grasse (06) N° 7803/88

#### Important notice

Individual copies of the present document can be downloaded from: <u>http://www.etsi.org</u>

The present document may be made available in more than one electronic version or in print. In any case of existing or perceived difference in contents between such versions, the reference version is the Portable Document Format (PDF). In case of dispute, the reference shall be the printing on ETSI printers of the PDF version kept on a specific network drive within ETSI Secretariat.

Users of the present document should be aware that the document may be subject to revision or change of status.

Information on the current status of this and other ETSI documents is available at

<a href="http://portal.etsi.org/tb/status/status.asp">http://portal.etsi.org/tb/status/status.asp</a></a>

If you find errors in the present document, please send your comment to one of the following services: http://portal.etsi.org/chaircor/ETSI\_support.asp

#### **Copyright Notification**

No part may be reproduced except as authorized by written permission. The copyright and the foregoing restriction extend to reproduction in all media.

© European Telecommunications Standards Institute 2004. All rights reserved.

**DECT**<sup>TM</sup>, **PLUGTESTS**<sup>TM</sup> and **UMTS**<sup>TM</sup> are Trade Marks of ETSI registered for the benefit of its Members. **TIPHON**<sup>TM</sup> and the **TIPHON logo** are Trade Marks currently being registered by ETSI for the benefit of its Members. **3GPP**<sup>TM</sup> is a Trade Mark of ETSI registered for the benefit of its Members and of the 3GPP Organizational Partners.

# Contents

| Intell  | ectual Property Rights                                                              | 5  |

|---------|-------------------------------------------------------------------------------------|----|

| Forev   | word                                                                                | 5  |

| Introd  | luction                                                                             | 6  |

| 1       | Scope                                                                               | 7  |

| 2       | References                                                                          | 7  |

| 3       | Definitions and abbreviations                                                       | 8  |

| 3.1     | Definitions                                                                         | 8  |

| 3.2     | Abbreviations                                                                       | 9  |

| 4       | Overview                                                                            | 10 |

| 5       | DTM SDH Transport Application Layer                                                 | 12 |

| 5.1     | Access point information                                                            |    |

| 5.1.1   | Characteristic Information                                                          |    |

| 5.1.2   | Adapted Information                                                                 | 13 |

| 5.1.3   | Management Information                                                              | 13 |

| 5.1.4   | Timing Information                                                                  |    |

| 5.2     | Connection function (APO_C)                                                         | 14 |

| 5.3     | Trail Termination functions (AP0e_TT)                                               | 14 |

| 5.3.1   | Application 0 empty Trail Termination (AP0e_TT)                                     | 14 |

| 5.3.1.  | 1 Application 0 empty Termination Source function (AP0e_TT_So)                      | 14 |

| 5.3.1.2 | 2 Application 0 empty Trail Termination Sink function (AP0e_TT_Sk)                  | 15 |

| 5.4     | Adaptation functions (APO/Sn_A)                                                     |    |

| 5.4.1   | DTM Application 0/SDH Higher order path Adaptation function (AP0/S4_A)              | 16 |

| 5.4.1.  |                                                                                     | 16 |

| 5.4.1.2 | 2 Media Adaptation Sink function (AP0/S4_A_Sk)                                      | 18 |

| 5.4.2   | DTM Application 0/SDH Higher order path Adaptation function (AP0/S3_A)              |    |

| 5.4.2.  | · · · · · · · · · · · · · · · · · · ·                                               |    |

| 5.4.2.2 | 2 Media Adaptation Sink function (AP0/S3_A_Sk)                                      | 22 |

| 5.4.3   | DTM Application 0/SDH Lower order S2 path Adaptation function (AP0/S2_A)            | 24 |

| 5.4.3.  | Application 0 to SDH Lower order path S2 Adaptation Source function (AP0/S2_A_So)   | 25 |

| 5.4.3.2 |                                                                                     |    |

| 5.4.4   | DTM Application 0/SDH Lower order S12 path Adaptation function (AP0/S12_A)          | 29 |

| 5.4.4.  | Application 0 to SDH Lower order path S12 Adaptation Source function (AP0/S12_A_So) | 29 |

| 5.4.4.  | Application 0 to SDH Lower order path S12 Adaptation Sink function (AP0/S12_A_Sk)   | 31 |

| 5.4.5   | DTM Application 0/SDH Lower order S11 path Adaptation function (AP0/S11_A)          | 33 |

| 5.4.5.  |                                                                                     |    |

| 5.4.5.2 | Application 0 to SDH Lower order path S11 Adaptation Sink function (AP0/S11_A_Sk)   | 35 |

| 6       | Mapping of SDH VC-4 over DTM                                                        |    |

| 6.1     | DCAP-0 slot elements                                                                |    |

| 6.2     | Data slot mapping                                                                   |    |

| 6.2.1   | Section beginning                                                                   |    |

| 6.2.2   | Section data                                                                        |    |

| 6.3     | VC-4 mapping                                                                        |    |

| 7       | Mapping of SDH VC-3 over DTM                                                        |    |

| 7.1     | DCAP-0 slot elements                                                                |    |

| 7.2     | Data slot mapping                                                                   |    |

| 7.2.1   | Section beginning                                                                   |    |

| 7.2.2   | Section data                                                                        |    |

| 7.3     | VC-3 mapping                                                                        | 40 |

| 8       | Mapping of SDH VC-2 over DTM                                                        | 40 |

| 8.1     | DCAP-0 slot elements                                                                |    |

| 8.2     | Data slot mapping                                                                   | 40 |

## Final draft ETSI ES 201 803-6 V1.2.1 (2004-10)

| 8.2.1  | Section beginning                                            | 40 |

|--------|--------------------------------------------------------------|----|

| 8.2.2  | Section data                                                 |    |

| 8.3    | VC-2 mapping                                                 |    |

| 9      | Mapping of SDH VC-12 over DTM                                | 41 |

| 9.1    | DCAP-0 slot elements                                         |    |

| 9.2    | Data slot mapping                                            |    |

| 9.2.1  | Section beginning                                            |    |

| 9.2.2  | Section data                                                 | 42 |

| 9.3    | VC-12 mapping                                                | 42 |

| 10     | Mapping of SDH VC-11 over DTM                                | 42 |

| 10.1   | DCAP-0 slot elements                                         |    |

| 10.2   | Data slot mapping                                            |    |

| 10.2.1 |                                                              |    |

| 10.2.2 |                                                              |    |

| 10.3   | VC-11 mapping                                                |    |

| 11     | Grouped mapping of virtual containers                        | 43 |

| 11.1   | Grouped mapping                                              |    |

| 11.2   | Separate or common phase                                     |    |

| 12     | Channel creation information                                 | 45 |

| 12.1   | Historical encoding of channel characteristics               |    |

| Anne   | x A (informative): Recommendation on Mapping of PDH over DTM | 46 |

| Histor | ry                                                           | 47 |

|        | •                                                            |    |

## Intellectual Property Rights

IPRs essential or potentially essential to the present document may have been declared to ETSI. The information pertaining to these essential IPRs, if any, is publicly available for **ETSI members and non-members**, and can be found in ETSI SR 000 314: "Intellectual Property Rights (IPRs); Essential, or potentially Essential, IPRs notified to ETSI in respect of ETSI standards", which is available from the ETSI Secretariat. Latest updates are available on the ETSI Web server (http://webapp.etsi.org/IPR/home.asp).

Pursuant to the ETSI IPR Policy, no investigation, including IPR searches, has been carried out by ETSI. No guarantee can be given as to the existence of other IPRs not referenced in ETSI SR 000 314 (or the updates on the ETSI Web server) which are, or may be, or may become, essential to the present document.

### **Foreword**

This ETSI Standard (ES) has been produced by ETSI Technical Committee Telecommunications and Internet converged Services and Protocols for Advanced Networking (TISPAN), and is now submitted for the ETSI standards Membership Approval Procedure.

The present document is part 6 of a multi-part deliverable covering the Dynamic synchronous Transfer Mode (DTM), as identified below:

```

ES 201 803-1:

"System description";

ES 201 803-2:

"System characteristics";

ES 201 803-3:

"Physical protocol";

ES 201 803-4:

"Mapping of DTM frames into SDH containers";

ES 201 803-5:

"Mapping of PDH over DTM";

ES 201 803-6:

"Mapping of Synchronous Digital Hierarchy (SDH) over DTM";

ES 201 803-7:

"Ethernet over DTM Mapping";

ES 201 803-9:

"Mapping of ATM over DTM";

TR 101 803-10: "Routeing and switching of IP traffic over DTM";

ES 201 803-11: "Mapping of video streams over DTM";

ES 201 803-12: "Mapping of MPLS over DTM";

ES 201 803-13: "System description of sub-rate DTM".

```

## Introduction

Dynamic synchronous Transfer Mode (DTM) is a time division multiplex and a circuit-switched network technique that combines switching and transport.

Part 1 describes the general properties of DTM and the DTM service over a unidirectional data channel. The overall system architecture is described and fundamental functions are identified.

Part 2 includes system aspects that are mandatory or optional for nodes from different vendors to interoperate. The interworking granularity should be at node level, such that nodes from different vendors can interoperate with regard to well-defined functions.

Part 3 specifies the physical layer for physical links based on 8B10B encoding.

Part 4 describes how DTM frames are mapped onto SDH containers.

The transport of various tributary signals is specified for PDH (part 5), SDH (part 6), Ethernet (part 7), ATM (part 9), IP (part 10), video streaming (part 11) and MPLS (part 12).

Subrate DTM is described in part 13.

## 1 Scope

The present document achieves the following:

- specifies a method for mapping SDH VC-11, VC-12, VC-2, VC-3, VC-4 and VC-4-Xc containers over DTM channels;

- specifies a method for grouped mapping of SDH VC-11, VC-12, VC-2, VC-3 and VC-4 containers over DTM channels;

- specifies the characteristics of critical parameters for mapping of SDH VC-11, VC-12, VC-2, VC-3, VC-4 and VC-4-Xc containers over DTM channels;

- specifies the characteristics of critical parameters for grouped mapping of SDH VC-11, VC-12, VC-2, VC-3 and VC-4 containers over DTM channels;

- gives terms and definitions for mapping encoding.

## 2 References

[8]

[9]

The following documents contain provisions, which, through reference in this text, constitute provisions of the present document.

- References are either specific (identified by date of publication and/or edition number or version number) or non-specific.

- For a specific reference, subsequent revisions do not apply.

- For a non-specific reference, the latest version applies.

Referenced documents, which are not found to be publicly available in the expected location might be found at <a href="http://docbox.etsi.org/Reference">http://docbox.etsi.org/Reference</a>.

| ш | p.//uocoox.ets1.or | g/Keletence.                                                                                                                                                                                                                 |

|---|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | [1]                | ETSI EN 300 417-1-1: "Transmission and Multiplexing (TM); Generic requirements of transport functionality of equipment; Part 1-1: Generic processes and performance".                                                        |

|   | [2]                | ETSI EN 300 417-3-1: "Transmission and Multiplexing (TM); Generic requirements of transport functionality of equipment; Part 3-1: Synchronous Transport Module-N (STM-N) regenerator and multiplex section layer functions". |

|   | [3]                | ETSI EN 300 417-4-1: "Transmission and Multiplexing (TM); Generic requirements of transport functionality of equipment; Part 4-1: Synchronous Digital Hierarchy (SDH) path layer functions".                                 |

|   | [4]                | ETSI EN 301 164: "Transmission and Multiplexing (TM); Synchronous Digital Hierarchy (SDH); SDH leased lines; Connection characteristics".                                                                                    |

|   | [5]                | ETSI EN 301 165: "Transmission and Multiplexing (TM); Synchronous Digital Hierarchy (SDH); SDH leased lines; Network and terminal interface presentation".                                                                   |

|   | [6]                | ETSI ES 201 803-2-3: "Dynamic synchronous Transfer Mode (DTM); Part 2: System characteristics; Sub-part 3: Transport network and channel adaptation aspects".                                                                |

|   | [7]                | ITU-T Recommendation G.707: "Network node interface for the Synchronous Digital Hierarchy (SDH)".                                                                                                                            |

|   |                    |                                                                                                                                                                                                                              |

methodology and generic functionality".

ITU-T Recommendation G.805: "Generic functional architecture of transport networks".

ITU-T Recommendation G.806: "Characteristics of transport equipment - Description

## 3 Definitions and abbreviations

#### 3.1 Definitions

For the purposes of the present document, the following terms and definitions apply:

**Access Point (AP):** "reference point" that consists of the pair of co-located "unidirectional access" points, and therefore represents the binding between the trail termination and adaptation functions

NOTE: Adopted from ITU-T Recommendation G.805 [8].

Adapted Information (AI): information passing across an AP

NOTE: See also ITU-T Recommendation G.805 [8]. Adopted from ITU-T Recommendation G.806 [9].

**Alarm Indication Signal (AIS):** special marker sent in a data slot to mark the lack of transported data as a result of a defect in the transmission path

channel: set of slots allocated from one source access node to one or more destination access nodes in a network

Characteristic Information (CI): signal with a specific format, which is transferred on "network connections"

NOTE: The specific formats will be defined in the technology specific Recommendations. The information passing across a CP or TCP. (Adopted from ITU-T Recommendation G.805 [8] and ITU-T Recommendation G.806 [9]).

**Connection Point (CP):** reference point where the output of a trail termination source or a connection is bound to the input of another connection, or where the output of a connection is bound to the input of a trail termination sink or another connection

NOTE: Adopted from ITU-T Recommendation G.806 [9].

defect: density of anomalies has reached a level where the ability to perform a required function has been interrupted

NOTE: Defects are used as input for performance monitoring, the control of consequent actions, and the determination of fault cause. (Adopted from ITU-T Recommendation G.806 [9]).

**frame:** set of slots forming an entity that is transmitted on a physical medium repeatedly every 125  $\mu$ s (nominally), i.e. 8 000 frames/second

grouped mapping: the mapping of a group of some number of elements being specified in a basic mapping.

NOTE: In grouped mapping, a mapping scheme from the channel to the basic mapping needs to be defined.

idle: special marker sent in a data slot to mark the lack of transported data in the slot

Management Information (MI): signal passing across an access point

NOTE: Adopted from ITU-T Recommendation G.806 [9].

**Management Point (MP):** reference point where the output of an atomic function is bound to the input of the element management function, or where the output of the element management function is bound to the input of an atomic function

NOTE: The MP is not the TMN Q3 interface. Adopted from ITU-T Recommendation G.806 [9].

**Performance Supervision (PS):** special marker sent with the data containing per channel Performance Supervision information

physical link: unidirectional connection between the transmitter of one port and the receiver of another port

Server Signal Fail (SSF): signal fail indication output at the CP of an adaptation function

NOTE: Adopted from ITU-T Recommendation G.806 [9].

**Signal Fail (SF):** signal indicating the associated data has failed in the sense that a near-end defect condition (not being the degraded defect) is active

NOTE: Adopted from ITU-T Recommendation G.806 [9].

slot: time slot within the frame being able to transport 64 bit of data or a number of special codes

Trail Signal Fail (TSF): signal fail indication output at the AP of a termination function

NOTE: Adopted from ITU-T Recommendation G.806 [9].

### 3.2 Abbreviations

For the purposes of the present document, the following abbreviations apply:

A Adapted function

aAIS Alarm Indication Signal action

AI Adapted Information AIS Alarm Indication Signal

AP Access Point

AP0 APplication layer channel adaptation type 0

AP0e APplication layer channel adaptation type 0 with empty trail termination

aSSF Server Signal Fail action BPn ByPass layer type n

BPnp ByPass layer type n Protection

C Connection function

cAIS Alarm Indication Signal cause

CH CHannel layer

CHn CHannel layer type-n

CHP CHannel layer Protection

CI Characteristic Information

CK ClocK

cLOJ Loss Of Justification cause

CP Connection Point

D Data

dAIS Alarm Indication Signal defect

DCAP DTM Channel Adaptation Protocol

DTM Dynamic synchronous Transfer Mode

fAIS Alarm Indication Signal fault

FJ- negative Frequency Justification

FJ+ positive Frequency Justification

fLOJ Loss Of Justification fault

FS Frame Start signal

IF In Frame

II Idle Insertion

MI Management Information

Mn Media layer type-n

MP Management Point

nAIS Alarm Indication Signal anomaly

nFJ- negative Frequency Justification anomaly positive Frequency Justification anomaly

nLOJ Loss Of Justification anomaly

OOF Out Of Frame

pFJ- negative Frequency Justification performance counter pFJ+ positive Frequency Justification performance counter

POH Path OverHead

PS Performance Supervision SDH Synchronous Digital Hierarchy

sFS Frame Start signal sII Idle Insertion signal

Sk Sink

Sn SDH higher order VC-n layer (n = 11, 12, 2, 3, 4, 4-Xc)

SSF Server Signal Fail

TI Timing Information

TP Timing Point

TSF Trail Signal Fail

TT Trail Termination

VC Virtual Container

VC-n Virtual Container, level n

VC-n-Xl Virtual Container, level n, linear concatenation VC-n-Xv Virtual Container, level n, virtual concatenation

VC-11 Virtual Container, level 11

VC-12 Virtual Container, level 12

VC-2 Virtual Container, level 2

VC-3 Virtual Container, level 3

VC-4 Virtual Container, level 4

VC-4-Xc Virtual Container, level 4, contiguous concatenation

### 4 Overview

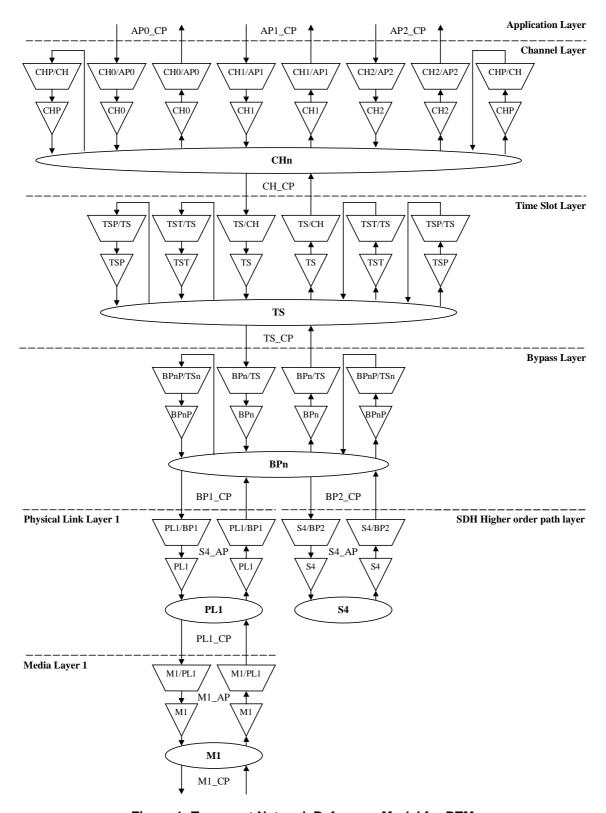

The SDH VC-11, VC-12, VC-2, VC-3, VC-4 and VC-4-Xc mapping over DTM (see figure 1) describes the mapping and framing of the virtual containers level 11 (VC-11), level 12 (VC-12), level 2 (VC-2), level 3 (VC-3) and level 4 (VC-4) into DTM channels. The functionality is part of the DTM Application layer and provides a transport service to the SDH higher and lower order path layer similar to the service provided by the SDH Multiplexing Section layer (EN 300 417-3-1 [2] and EN 300 417-4-1 [3]). The transport functionality provides a SDH VC DTM Timeslot connection over a DTM network as if this where a physical link between the SDH nodes. The service can be viewed as a leased VC-11, VC-12, VC-2, VC-3, VC-4 or VC-4-Xc over the DTM network, thus similar to EN 301 164 [4] and EN 301 165 [5].

The grouped mapping of SDH VC-11, VC-12, VC-2, VC-3 and VC-4 containers over DTM provides for an integer number of the same container to be grouped inside the same DTM channel. This allows for ease of management when multiple containers are required for the same service. Such a service includes Virtual conCATenation (VCAT) of NG-SDH.

The grouped mapping allows for separate or common phase of the grouped virtual containers. Separate phase grouping allows for separate connections or other unorganized phase aligned signals to be grouped. Common phase grouping allows for well ordered phase alignment to be maintained over the DTM network, thus reducing or eliminating the need for phase adjustment in the receiving end.

- NOTE 1: A number of ungrouped VC-n channels are thus equivalent to being grouped with separate phase, except for the separate channels with associated per channel management. Grouping can reduce the management overhead as well as providing a convenient association between the individual virtual containers.

- NOTE 2: A number of ungrouped VC-n channels are not equivalent to the grouped mapping of VC-n with common phase. This is due to the fact that even if the input signals is in phase, the frequency justification is individual and also, the lack of end-to-end association in the setup phase of channels does not guarantee the same path and delay as a single channel will provide.

The SDH Lower order Virtual Containers contain 26 (VC-11), 35 (VC-12) and 107 (VC-2) octets per row, 4 rows per 500 us super-frame. The SDH Higher order Virtual Containers contain 85 (VC-3), 261 (VC-4) and  $261 \times X$  (VC-4-Xc) octets per row, 9 rows per frame. The VC frame rate may deviate from the SDH transmission rate by up to  $\pm 4.6$  ppm (EN 300 417-3-1 [2] and EN 300 417-4-1 [3]) such that frequency justification is required. DTM idle special marker insertion or exclusion upon justification opportunity replaces the SDH frequency justification mechanism of pointer justifications.

NOTE 3: Limited support for frequency deviations up to  $\pm 20$  ppm can exist but is not guaranteed.

The SDH supervision functionality is mapped over to the DTM functionality and SDH AIS is being encoded into DTM AIS.

Figure 1: Transport Network Reference Model for DTM

# 5 DTM SDH Transport Application Layer

The SDH VC-11/VC-12/VC-2/VC-3/VC-4/VC-4-Xc over DTM transport is specified as the adaptation functions on top of the DCAP-0 (ES 201 803-2-3 [6]) trail terminator functions, providing the S11/S12/S2 Lower order trail and the S3/S4 Higher order trail over DTM.

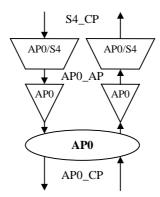

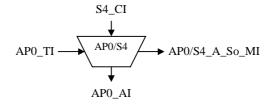

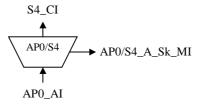

Figure 2: DTM Application layer 0 for SDH VC-4 mapping atomic functions

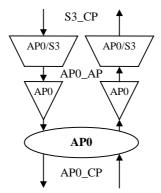

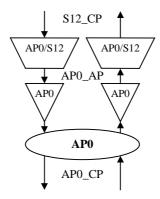

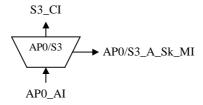

Figure 3: DTM Application layer 0 for SDH VC-3 mapping atomic functions

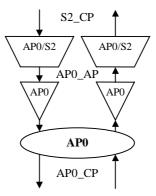

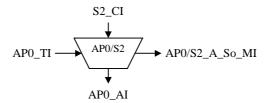

Figure 4: DTM Application layer 0 for SDH VC-2 mapping atomic functions

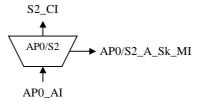

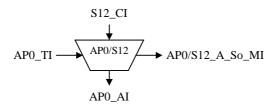

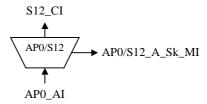

Figure 5: DTM Application layer 0 for SDH VC-12 mapping atomic functions

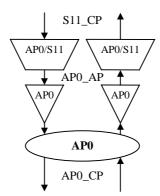

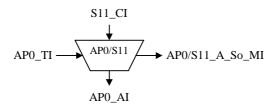

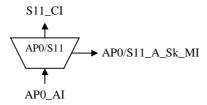

Figure 6: DTM Application layer 0 for SDH VC-11 mapping atomic functions

## 5.1 Access point information

#### 5.1.1 Characteristic Information

The Characteristic Information (CI) of the Connection Point (CP) is described in EN 300 417-4-1 [3].

## 5.1.2 Adapted Information

The Adapted Information (AI) of the Adaptation Point (AP) is described in ES 201 803-2-3 [6] as the Application 0 Characteristic Information.

## 5.1.3 Management Information

The Management Information (MI) of the Management Point (MP) is (for VC-4, VC-3, VC-2, VC-12 and VC-11 respectively):

- the 1 second timer signal AP0/S4\_A\_So\_MI\_1second, AP0/S3\_A\_So\_MI\_1second, AP0/S2\_A\_So\_MI\_1second, AP0/S12\_A\_So\_MI\_1second and AP0/S11\_A\_So\_MI\_1second;

- the positive frequency justification 1 second performance counter AP0/S4\_A\_So\_MI\_pFJ+, AP0/S3\_A\_So\_MI\_pFJ+, AP0/S2\_A\_So\_MI\_pFJ+, AP0/S12\_A\_So\_MI\_pFJ+ and AP0/S11\_A\_So\_MI\_pFJ+;

- the negative frequency justification 1 second performance counter AP0/S4\_A\_So\_MI\_pFJ-, AP0/S3\_A\_So\_MI\_pFJ-, AP0/S2\_A\_So\_MI\_pFJ-, AP0/S12\_A\_So\_MI\_pFJ- and AP0/S11\_A\_So\_MI\_pFJ-;

- the loss of justification cause signal AP0/S4\_A\_Sk\_MI\_cLOJ, AP0/S3\_A\_Sk\_MI\_cLOJ, AP0/S2\_A\_Sk\_MI\_cLOJ, AP0/S12\_A\_Sk\_MI\_cLOJ and AP0/S11\_A\_Sk\_MI\_cLOJ;

14

• and the alarm indication signal cause signal AP0/S4\_A\_Sk\_MI\_cAIS, AP0/S3\_A\_Sk\_MI\_cAIS, AP0/S2\_A\_Sk\_MI\_cAIS, AP0/S12\_A\_Sk\_MI\_cAIS and AP0/S11\_A\_Sk\_MI\_cAIS.

## 5.1.4 Timing Information

The Timing Information (TI) of the Timing Point (TP) is:

- the Application 0 data clock timing indication AP0\_TI\_CK;

- and the Application 0 frame start timing indication AP0\_TI\_FS.

## 5.2 Connection function (AP0\_C)

Not applicable. There are no connection functions defined for this layer.

## 5.3 Trail Termination functions (AP0e\_TT)

The trail termination functions are empty mappings between AI and CI.

## 5.3.1 Application 0 empty Trail Termination (AP0e\_TT)

### 5.3.1.1 Application 0 empty Termination Source function (AP0e\_TT\_So)

Symbol:

Figure 7: Application 0 empty Trail Termination Source (AP0e\_TT\_So)

#### **Interfaces:**

Table 1: AP0e\_TT\_So Input and output signals

| Input(s)   | Output(s)  |

|------------|------------|

| AP0_AI_D   | AP0_CI_D   |

| AP0_AI_CK  | AP0_CI_CK  |

| AP0_AI_II  | AP0_CI_II  |

| AP0_AI_PSI | AP0_CI_PSI |

| AP0_AI_TSF | APO CI SSF |

| Processes   | and | anomalies | • |

|-------------|-----|-----------|---|

| 1 1 0000000 | anu | anomanes  | • |

None.

**Defects:**

None.

#### **Consequent actions:**

None.

| n  | ρf | 001 | ŀ. | ഹ | rre | la   | ti | nn | •  |

|----|----|-----|----|---|-----|------|----|----|----|

| ., |    |     |    |   |     | 1121 |    | ш  | 13 |

None.

#### **Performance monitoring:**

None.

#### **Output mapping:**

$AP0\_CI\_D \leftarrow AP0\_AI\_D.$

$AP0\_CI\_CK \leftarrow AP0\_AI\_CK.$

$AP0\_CI\_II \leftarrow AP0\_AI\_II.$

$AP0\_CI\_PSI \leftarrow AP0\_AI\_PSI.$

$AP0\_CI\_SSF \leftarrow AP0\_AI\_TSF.$

#### **Fault management:**

None.

#### Long term performance monitoring:

None.

## 5.3.1.2 Application 0 empty Trail Termination Sink function (AP0e\_TT\_Sk)

#### **Symbol:**

Figure 8: Application 0 empty Trail Termination Sink (AP0e\_TT\_Sk)

#### **Interfaces:**

Table 2: AP0e\_TT\_Sk Input and output signals

| Input(s)   | Output(s)  |

|------------|------------|

| AP0_CI_D   | AP0_AI_D   |

| AP0_CI_CK  | AP0_AI_CK  |

| AP0_CI_II  | AP0_AI_II  |

| AP0_CI_PSI | AP0_AI_PSI |

| AP0_CI_SSF | AP0_AI_TSF |

#### Processes and anomalies:

None.

**Defects:**

None.

#### **Consequent actions:**

None.

**Defect correlation:**

None.

**Performance monitoring:**

None.

**Output mapping:**

$AP0\_AI\_D \leftarrow AP0\_CI\_D.$

$AP0\_AI\_CK \leftarrow AP0\_CI\_CK.$

$AP0\_AI\_II \leftarrow AP0\_CI\_II.$

$AP0\_AI\_PSI \leftarrow AP0\_CI\_PSI.$

$AP0\_AI\_TSF \leftarrow AP0\_CI\_SSF.$

**Fault management:**

None.

Long term performance monitoring:

None.

## 5.4 Adaptation functions (AP0/Sn\_A)

# 5.4.1 DTM Application 0/SDH Higher order path Adaptation function (AP0/S4\_A)

This clause describes the SDH VC-4 adaptation using DCAP-0 trail terminators.

## 5.4.1.1 Media Adaptation Source function (AP0/S4\_A\_So)

Symbol:

Figure 9: DTM Application 0/SDH Higher order path Adaptation Source (AP0/S4\_A\_So)

**Interfaces:**

Table 3: AP0/S4\_A\_So Input and output signals

| Input(s)               | Output(s)           |

|------------------------|---------------------|

| S4_CI_D                | AP0_AI_D            |

| S4_CI_CK               | AP0_AI_CK           |

| S4_CI_FS               | AP0_AI_II           |

| S4_CI_SSF              | AP0_AI_PSI          |

| AP0_TI_CK              | AP0_AI_TSF          |

| AP0_TI_FS              | AP0/S4_A_So_MI_pFJ- |

| AP0/S4 A So MI 1second | AP0/S4 A So MI pFJ+ |

#### **Processes and anomalies:**

The generation of frame alignment pattern in order to indicate the initial segment of a multi-segment VC-4 transport stream according to clause 6.2.1. See ES 201 803-2-3 [6] clause 6.1.9.4.

The division of the VC-4 octet stream into segments as specified in clause 6. See ES 201 803-2-3 [6] clause 6.1.13.5.

The multiplexing of the section alignment signal and the 5 first octets of the segment into an initial slot. See ES 201 803-2-3 [6] clause 6.1.13.6.

The multiplexing of 8 contiguous octets in the segment into a data slot. See ES 201 803-2-3 [6] clause 6.1.13.6.

The multiplexing of an initial slot and 293 contiguous data slots into a slot stream on AI\_D. See ES 201 803-2-3 [6] clause 6.1.13.6.

sII: The indirect multiplexing (performed by the TT\_So) of 0, 1 or 2 idle markers prior to the initial segment (see clause 6) by assertion of the Idle Insertion signal (sII). The number of idle markers is given by the frequency justification process, see ES 201 803-2-3 [6] clause 6.1.12.1. See ES 201 803-2-3 [6] clause 6.1.13.6.

sPSI: The Performance Supervision Insertion signal (sPSI) is asserted when the performance supervision special marker of a segment is to be transmitted according to clause 6, else it is de-asserted. See ES 201 803-2-3 [6] clause 6.1.13.6.

The continuous monitoring of the deviation in phase between the incoming signal and the transmitted signal is performed in order do perform frequency justifications. See ES 201 803-2-3 [6] clause 6.1.8.1.

The performance of positive justification when the incoming signal rate is above the nominal signal rate, by the transmission of a data in replacement of an idle-marker where positive justification is allowed. See ES 201 803-2-3 [6] clause 6.1.8.1. For justification opportunity, see clause 6.1.

The performance of negative justification when the incoming signal rate is below the nominal signal rate, by the transmission of an idle-marker in place of data where negative justification is allowed. See ES 201 803-2-3 [6] clause 6.1.8.1. For justification opportunity, see clause 6.1.

nFJ+: The positive frequency justification anomaly (nFJ+) is asserted when a positive frequency justification has occurred, else it is de-asserted. See ES 201 803-2-3 [6] clause 6.1.8.1.

nFJ-: The negative frequency justification anomaly (nFJ-) is asserted when a negative frequency justification has occurred, else it is de-asserted. See ES 201 803-2-3 [6] clause 6.1.8.1.

AIS: The Alarm Indication Signal (AIS) insertion into AI\_D instead of received signal when the CI\_SSF signal is asserted. See ES 201 803-2-3 [6] clause 6.1.5.1.

#### **Defects:**

None.

#### **Consequent actions:**

aAIS: The Alarm Indication Signal action (aAIS) is asserted when the Server Signal Fail (SSF) is asserted. See ES 201 803-2-3 [6] clause 6.3.1.1.

$aAIS \leftarrow CI SSF.$

#### **Defect correlation:**

None.

#### **Performance monitoring:**

pFJ+ (A\_So): The Positive Frequency Justification performance (pFJ+) is the number of positive frequency justifications anomalies (nFJ+) that has occurred during 1 second. See ES 201 803-2-3 [6] clause 6.5.3.1.

$pFJ+ \leftarrow \Sigma nFJ+.$

pFJ- (A\_So): The Negative Frequency Justification performance (pFJ-) is the number of negative frequency justifications anomalies (nFJ-) that has occurred during 1 second. See ES 201 803-2-3 [6] clause 6.5.3.2.

$pFJ- \ \leftarrow \ \Sigma \ nFJ-.$

#### **Output mapping:**

$AP0\_AI\_D \leftarrow AI\_D$ .

$AP0\_AI\_CK \leftarrow AP0\_TI\_CK.$

$AP0\_AI\_II \leftarrow sII.$

$AP0\_AI\_PSI \leftarrow sPSI$ .

APO AI TSF  $\leftarrow$  S4 CI SSF.

$AP0/S4\_A\_So\_MI\_pFJ+ \leftarrow pFJ+.$

$AP0/S4\_A\_So\_MI\_pFJ- \leftarrow pFJ-.$

#### Fault management:

None.

#### Long term performance monitoring:

FJ+(t-10) (A\_Sk): The delayed positive Frequency Justification performance counter (FJ+(t-10)) is the 10 second delayed value of the positive Frequency Justification performance counter (pFJ+). See ES 201 803-2-3 [6] clause 6.8.5.2.

FJ-(t-10) (A\_Sk): The delayed negative Frequency Justification performance counter (FJ-(t-10)) is the 10 second delayed value of the negative Frequency Justification performance counter (pFJ-). See ES 201 803-2-3 [6] clause 6.8.5.2.

### 5.4.1.2 Media Adaptation Sink function (AP0/S4\_A\_Sk)

#### Symbol:

Figure 10: Media Adaptation Sink (AP0/S4\_A\_Sk)

#### **Interfaces:**

Table 4: AP0/S4\_A\_Sk Input and output signals

| Input(s)   | Output(s)           |

|------------|---------------------|

| AP0_AI_D   | S4_CI_D             |

| AP0_AI_CK  | S4_CI_CK            |

| AP0_AI_II  | S4_CI_FS            |

| AP0_AI_PSI | S4_CI_SSF           |

| AP0_AI_TSF | AP0/S4_A_Sk_MI_cAIS |

|            | AP0/S4_A_Sk_MI_cLOJ |

#### **Processes and anomalies:**

The monitoring of frame alignment pattern in order to identify the initial segment of a multi-segment VC-4 transport stream according to clause 6.2.1. See ES 201 803-2-3 [6] clause 6.1.9.4.

sFS: When the initial segment is detected and the first of its data words is transmitted on CI\_D shall the Frame Start signal (sFS) be asserted, else it shall be de-asserted. See ES 201 803-2-3 [6] clause 6.1.9.4.

nLOJ: If the initial segment does not occur after the specified justification, then the Loss Of Justification anomaly (nLOJ) is asserted, else nLOJ is not asserted. See clause 6.2.1 and ES 201 803-2-3 [6] clause 6.1.9.4.

The demultiplexing of the initial slot and 293 contiguous data slots from the slot stream on AI\_D. See ES 201 803-2-3 [6] clause 6.1.13.6.

The demultiplexing of the initial slot to the section alignment signal and the 5 first octets of the segment. See ES 201 803-2-3 [6] clause 6.1.13.6.

The demultiplexing of the data slots into 8 contiguous octets in the VC-4 octet stream. See ES 201 803-2-3 [6] clause 6.1.13.6.

The reconstruction of the VC-4 octet stream from the received segments as specified in clause 6. See ES 201 803-2-3 [6] clause 6.1.13.5.

The clock smoothing process in order to reduce phase deviations on the transmitted signal. The clock smoothing must comply with the jitter and wander requirements as defined in EN 300 417-1-1 [1]. The resulting clock is delivered as CI CK. See ES 201 803-2-3 [6] clause 6.1.11.3.

The elastic buffering of the transported signal such that the buffer output is being clocked by the smoothed clock. See ES 201 803-2-3 [6] clause 6.1.11.3.

AIS (A\_Sk): The Alarm Indication Signal (AIS) insertion into CI\_D instead of received data when the Alarm Indication Signal defect (dAIS) is asserted. See ES 201 803-2-3 [6] clause 6.1.5.1.

nAIS: The Alarm Indication Signal anomaly (nAIS) is asserted when an AIS-marker is being detected in the AI\_D stream. See ES 201 803-2-3 [6] clause 6.1.5.1.

#### **Defects:**

The justification persistence state machine monitors the Loss Of Justification anomaly (nLOJ). The default state is Out Of Frame (OOF). When in the OOF state the nLOJ is not asserted on three consecutive justification opportunities, the state of the machine shall change to In Frame (IF). When in the IF state the nLOJ is asserted on five consecutive justification opportunities, the state of the machine shall change to OOF. See ES 201 803-2-3 [6] clause 6.2.4.2.

dLOJ: The Loss Of Justification defect (dLOJ) shall be asserted when the justification persistence state machine is in the OOF state. See ES 201 803-2-3 [6] clause 6.2.4.2.

dAIS (A\_Sk): The Alarm Indication Signal defect (dAIS) is asserted when the Alarm Indication Signal anomaly (nAIS) is asserted for more than three consecutive DTM frames, else it is not asserted. See ES 201 803-2-3 [6] clause 6.2.6.1.

#### **Consequent actions:**

aAIS: The Alarm Indication Signal action (aAIS) is asserted when the Loss Of Justification defect (dLOJ), the Alarm Indication Signal defect (dAIS) is asserted or the Trail Signal Fail (AI\_TSF) is. See ES 201 803-2-3 [6] clause 6.3.1.1.

$aAIS \leftarrow dLOJ \text{ or } dAIS \text{ or } AI\_TSF.$

aSSF: The Server Signal Fail action (aSSF) is asserted when the Alarm Indication Signal defect (dAIS) is asserted, the Trail Signal Fail (AI\_TSF) is asserted or the Loss Of Justification defect (dLOJ) is asserted. See ES 201 803-2-3 [6] clause 6.3.1.2.

$aSSF \leftarrow dAIS \text{ or AI TSF or dLOJ}.$

#### **Defect correlation:**

cLOJ: The Loss Of Justification cause (cLOJ) is asserted when the Loss Of Justification defect (dLOJ) is asserted, the Alarm Indication Signal defect (dAIS) not asserted and Trail Signal Fail (AI\_TSF) is not asserted. See ES 201 803-2-3 [6] clause 6.4.4.2.

cLOJ ← dLOJ and (not dAIS) and (not AI TSF)

cAIS: The Alarm Indication Signal cause (cAIS) is asserted when the Alarm Indication Signal defect (dAIS) is asserted and the Trail Signal Failure (AI\_TSF) is not asserted. See ES 201 803-2-3 [6] clause 6.4.6.1.

$cAIS \leftarrow dAIS \text{ and (not AI\_TSF)}$

#### **Performance monitoring:**

None.

#### **Output mapping:**

$S4\_CI\_D \leftarrow CI\_D.$

$S4\_CI\_CK \leftarrow CI\_CK$ .

$S4\_CI\_FS \leftarrow sFS$ .

$S4\_CI\_SSF \leftarrow aSSF.$

$AP0/S4\_A\_Sk\_MI\_cLOJ \leftarrow cLOJ$ .

$AP0/S4\_A\_Sk\_MI\_cAIS \leftarrow cAIS$ .

#### **Fault management:**

fAIS (A\_Sk): The Alarm Indication Signal fault (fAIS) is asserted when the Alarm Indication Signal cause (cAIS) is asserted consistently for  $2,5\pm0,5$  seconds and not asserted when the cAIS have been not asserted for  $10\pm0,5$  seconds. See ES 201 803-2-3 [6] clause 6.6.1.3.

fLOJ (A\_Sk): The Loss Of Justification fault (fLOF) is asserted when the Loss Of Justification cause (cLOJ) is asserted consistently for  $2.5 \pm 0.5$  seconds and not asserted when the cLOJ have been not asserted for  $10 \pm 0.5$  seconds. See ES 201 803-2-3 [6] clause 6.6.1.6.

#### Long term performance monitoring:

None.

# 5.4.2 DTM Application 0/SDH Higher order path Adaptation function (AP0/S3\_A)

This clause describes the SDH VC-3 adaptation using DCAP-0 trail terminators.

#### 5.4.2.1 Media Adaptation Source function (AP0/S3\_A\_So)

Symbol:

Figure 11: DTM Application 0/SDH Higher order path Adaptation Source (AP0/S3\_A\_So)

#### Interfaces:

Table 5: AP0/S3\_A\_So Input and output signals

| Input(s)               | Output(s)           |

|------------------------|---------------------|

| S3_CI_D                | AP0_AI_D            |

| S3_CI_CK               | AP0_AI_CK           |

| S3_CI_FS               | AP0_AI_II           |

| S3_CI_SSF              | AP0_AI_PSI          |

| AP0_TI_CK              | AP0_AI_TSF          |

| AP0_TI_FS              | AP0/S3_A_So_MI_pFJ- |

| AP0/S3_A_So_MI_1second | AP0/S3_A_So_MI_pFJ+ |

#### **Processes and anomalies:**

The generation of frame alignment pattern in order to indicate the initial segment of a multi-segment VC-3 transport stream according to clause 7.2.1. See ES 201 803-2-3 [6] clause 6.1.9.4.

The division of the VC-3 octet stream into segments as specified in clause 7. See ES 201 803-2-3 [6] clause 6.1.13.5.

The multiplexing of the section alignment signal and the 7 first octets of the segment into an initial slot. See ES 201 803-2-3 [6] clause 6.1.13.6.

The multiplexing of 8 contiguous octets in the segment into a data slot. See ES 201 803-2-3 [6] clause 6.1.13.6.

The multiplexing of an initial slot and 97 contiguous data slots into a slot stream on AI\_D. See ES 201 803-2-3 [6] clause 6.1.13.6.

sII (A\_So): The indirect multiplexing (performed by the TT\_So) of 0, 1 or 2 idle markers prior to the initial segment (see clause 6) by assertion of the Idle Insertion signal (sII). The number of idle markers is given by the frequency justification process, see ES 201 803-2-3 [6] clauses 6.1.12.1 and 6.1.13.6.

sPSI (A\_So): The Performance Supervision Insertion signal (sPSI) is asserted when the performance supervision special marker of a segment is to be transmitted according to clause 6, else it is de-asserted. See ES 201 803-2-3 [6] clause 6.1.13.6.

The continuous monitoring of the deviation in phase between the incoming signal and the transmitted signal is performed in order do perform frequency justifications. See ES 201 803-2-3 [6] clause 6.1.8.1.

The performance of positive justification when the incoming signal rate is above the nominal signal rate, by the transmission of a data in replacement of an idle-marker where positive justification is allowed. See ES 201 803-2-3 [6] clause 6.1.8.1. For justification opportunity, see clause 7.1.

The performance of negative justification when the incoming signal rate is below the nominal signal rate, by the transmission of an idle-marker in place of data where negative justification is allowed. See ES 201 803-2-3 [6] clause 6.1.8.1. For justification opportunity, see clause 7.1.

nFJ+: The positive frequency justification anomaly (nFJ+) is asserted when a positive frequency justification has occurred, else it is de-asserted. See ES 201 803-2-3 [6] clause 6.1.8.1.

nFJ-: The negative frequency justification anomaly (nFJ-) is asserted when a negative frequency justification has occurred, else it is de-asserted. See ES 201 803-2-3 [6] clause 6.1.8.1.

AIS: The Alarm Indication Signal (AIS) insertion into AI\_D instead of received signal when the CI\_SSF signal is asserted. See ES 201 803-2-3 [6] clause 6.1.5.1.

#### **Defects:**

None.

#### **Consequent actions:**

aAIS: The Alarm Indication Signal action (aAIS) is asserted when the Server Signal Fail (SSF) is asserted. See ES 201 803-2-3 [6] clause 6.3.1.1.

$aAIS \leftarrow CI\_SSF.$

#### **Defect correlation:**

None.

#### **Performance monitoring:**

pFJ+ (A\_So): The Positive Frequency Justification performance (pFJ+) is the number of positive frequency justifications anomalies (nFJ+) that has occurred during 1 second. See ES 201 803-2-3 [6] clause 6.5.3.1.

$$pFJ+ \ \leftarrow \ \Sigma \ nFJ+.$$

pFJ- (A\_So): The Negative Frequency Justification performance (pFJ-) is the number of negative frequency justifications anomalies (nFJ-) that has occurred during 1 second. See ES 201 803-2-3 [6] clause 6.5.3.2.

pFJ-  $\leftarrow \Sigma$  nFJ-.

#### **Output mapping:**

$AP0\_AI\_D \leftarrow AI\_D$ .

$AP0\_AI\_CK \leftarrow AP0\_TI\_CK$ .

$AP0\_AI\_II \leftarrow sII.$

$AP0\_AI\_PSI \leftarrow sPSI$ .

$AP0\_AI\_TSF \leftarrow AP0\_CI\_SSF$ .

$AP0/S3\_A\_So\_MI\_pFJ+ \leftarrow pFJ+$ .

$AP0/S3\_A\_So\_MI\_pFJ- \leftarrow pFJ-.$

#### Fault management:

None.

#### Long term performance monitoring:

FJ+(t-10) (A\_Sk): The delayed positive Frequency Justification performance counter (FJ+(t-10)) is the 10 second delayed value of the positive Frequency Justification performance counter (pFJ+). See ES 201 803-2-3 [6] clause 6.8.5.2.

FJ-(t-10) (A\_Sk): The delayed negative Frequency Justification performance counter (FJ-(t-10)) is the 10 second delayed value of the negative Frequency Justification performance counter (pFJ-). See ES 201 803-2-3 [6] clause 6.8.5.2.

#### 5.4.2.2 Media Adaptation Sink function (AP0/S3\_A\_Sk)

#### Symbol:

Figure 12: Media Adaptation Sink (AP0/S3\_A\_Sk)

#### Interfaces:

Table 6: AP0/S4\_A\_Sk Input and output signals

| Input(s)   | Output(s)           |

|------------|---------------------|

| AP0_AI_D   | S3_CI_D             |

| AP0_AI_CK  | S3_CI_CK            |

| AP0_AI_II  | S3_CI_FS            |

| AP0_AI_PSI | S3_CI_SSF           |

| AP0_AI_TSF | AP0/S3_A_Sk_MI_cAIS |

|            | AP0/S3_A_Sk_MI_cLOJ |

#### **Processes and anomalies:**

The monitoring of frame alignment pattern in order to identify the initial segment of a multi-segment VC-3 transport stream according to clause 7.2.1. See ES 201 803-2-3 [6] clause 6.1.9.4.

sFS: When the initial segment is detected and the first of its data words is transmitted on CI\_D shall the Frame Start signal (sFS) be asserted, else it shall be de-asserted. See ES 201 803-2-3 [6] clause 6.1.9.4.

nLOJ: If the initial segment does not occur after the specified justification, then the Loss Of Justification anomaly (nLOJ) is asserted, else nLOJ is not asserted. See clause 6.2.1 and ES 201 803-2-3 [6] clause 6.1.9.4.

The demultiplexing of the initial slot and 97 contiguous data slots from the slot stream on AI\_D. See ES 201 803-2-3 [6] clause 6.1.13.6.

The demultiplexing of the initial slot to the section alignment signal and the 7 first octets of the segment. See ES 201 803-2-3 [6] clause 6.1.13.6.

The demultiplexing of the data slots into 8 contiguous octets in the VC-3 octet stream. See ES 201 803-2-3 [6] clause 6.1.13.6.

The reconstruction of the VC3 octet stream from the received segments as specified in clause 7. See ES 201 803-2-3 [6] clause 6.1.13.5.

The clock smoothing process in order to reduce phase deviations on the transmitted signal. The clock smoothing must comply with the jitter and wander requirements as defined in EN 300 417-1-1 [1]. The resulting clock is delivered as CI\_CK. See ES 201 803-2-3 [6] clause 6.1.11.3.

The elastic buffering of the transported signal such that the buffer output is being clocked by the smoothed clock. See ES 201 803-2-3 [6] clause 6.1.11.3.

AIS (A\_Sk): The Alarm Indication Signal (AIS) insertion into CI\_D instead of received data when the Alarm Indication Signal defect (dAIS) is asserted. See ES 201 803-2-3 [6] clause 6.1.5.1.

nAIS: The Alarm Indication Signal anomaly (nAIS) is asserted when an AIS-marker is being detected in the AI\_D stream. See ES 201 803-2-3 [6] clause 6.1.5.1.

#### **Defects:**

The justification persistence state machine monitors the Loss Of Justification anomaly (nLOJ). The default state is Out Of Frame (OOF). When in the OOF state the nLOJ is not asserted on three consecutive justification opportunities, the state of the machine shall change to In Frame (IF). When in the IF state the nLOJ is asserted on five consecutive justification opportunities, the state of the machine shall change to OOF. See ES 201 803-2-3 [6] clause 6.2.4.2.

dLOJ: The Loss Of Justification defect (dLOJ) shall be asserted when the justification persistence state machine is in the OOF state. See ES 201 803-2-3 [6] clause 6.2.4.2.

dAIS (A\_Sk): The Alarm Indication Signal defect (dAIS) is asserted when the Alarm Indication Signal anomaly (nAIS) is asserted for more than three consecutive DTM frames, else it is not asserted. See ES 201 803-2-3 [6] clause 6.2.6.1.

#### **Consequent actions:**

aAIS: The Alarm Indication Signal action (aAIS) is asserted when the Loss Of Justification defect (dLOJ), the Alarm Indication Signal defect (dAIS) is asserted or the Trail Signal Fail (AI\_TSF) is. See ES 201 803-2-3 [6] clause 6.3.1.1.

$aAIS \leftarrow dLOJ \text{ or } dAIS \text{ or } AI\_TSF.$

aSSF: The Server Signal Fail action (aSSF) is asserted when the Alarm Indication Signal defect (dAIS) is asserted, the Trail Signal Fail (AI\_TSF) is asserted or the Loss Of Justification defect (dLOJ) is asserted. See ES 201 803-2-3 [6] clause 6.3.1.2.

$aSSF \leftarrow dAIS \text{ or } AI\_TSF \text{ or } dLOJ.$

#### **Defect correlation:**

cLOJ: The Loss Of Justification cause (cLOJ) is asserted when the Loss Of Justification defect (dLOJ) is asserted, the Alarm Indication Signal defect (dAIS) not asserted and Trail Signal Fail (AI\_TSF) is not asserted. See ES 201 803-2-3 [6] clause 6.4.4.2.

$cLOJ \leftarrow dLOJ$  and (not dAIS) and (not AI\_TSF).

cAIS: The Alarm Indication Signal cause (cAIS) is asserted when the Alarm Indication Signal defect (dAIS) is asserted and the Trail Signal Failure (AI\_TSF) is not asserted. See ES 201 803-2-3 [6] clause 6.4.6.1.

$cAIS \leftarrow dAIS \text{ and (not AI\_TSF)}$

#### **Performance monitoring:**

None.

#### **Output mapping:**

$S3_CI_D \leftarrow CI_D$ .

$S3_CI_CK \leftarrow CI_CK$ .

$S3\_CI\_FS \leftarrow sFS$ .

$S3\_CI\_SSF \leftarrow aSSF$ .

$AP0/S3\_A\_Sk\_MI\_cLOJ \leftarrow cLOJ$ .

$AP0/S3\_A\_Sk\_MI\_cAIS \leftarrow cAIS$ .

#### **Fault management:**

fAIS (A\_Sk): The Alarm Indication Signal fault (fAIS) is asserted when the Alarm Indication Signal cause (cAIS) is asserted consistently for  $2.5 \pm 0.5$  seconds and not asserted when the cAIS have been not asserted for  $10 \pm 0.5$  seconds. See ES 201 803-2-3 [6] clause 6.6.1.3.

fLOJ (A\_Sk): The Loss Of Justification fault (fLOF) is asserted when the Loss Of Justification cause (cLOJ) is asserted consistently for  $2,5\pm0,5$  seconds and not asserted when the cLOJ have been not asserted for  $10\pm0,5$  seconds. See ES 201 803-2-3 [6] clause 6.6.1.6.

#### Long term performance monitoring:

None.

# 5.4.3 DTM Application 0/SDH Lower order S2 path Adaptation function (AP0/S2\_A)

This clause describes the SDH VC-2 adaptation using DCAP-0 trail terminators.

# 5.4.3.1 Application 0 to SDH Lower order path S2 Adaptation Source function (AP0/S2\_A\_So)

Symbol:

25

Figure 13: DTM Application 0/SDH Lower order path S2 Adaptation Source (AP0/S2\_A\_So)

#### **Interfaces:**

Output(s) Input(s) S2\_CI\_D AP0\_AI\_D AP0\_AI\_CK S2 CI CK S2\_CI\_FS AP0\_AI\_II S2\_CI\_SSF AP0\_AI\_PSI AP0\_TI\_CK AP0\_AI\_TSF AP0/S2\_A\_So\_MI\_pFJ-AP0\_TI\_FS AP0/S2\_A\_So\_MI\_1second AP0/S2\_A\_So\_MI\_pFJ+

Table 7: AP0/S2\_A\_So Input and output signals

#### **Processes and anomalies:**

The generation of frame alignment pattern in order to indicate the initial segment of a multi-segment VC-2 transport stream according to clause 8.2.1. See ES 201 803-2-3 [6] clause 6.1.9.4.

The division of the VC-2 octet stream into segments as specified in clause 8. See ES 201 803-2-3 [6] clause 6.1.13.5.

The multiplexing of the section alignment signal into an initial slot. See ES 201 803-2-3 [6] clause 6.1.13.6.

The multiplexing of 8 contiguous octets in the segment into a data slot. See ES 201 803-2-3 [6] clause 6.1.13.6.

The multiplexing of an initial slot and 53 contiguous data slots into a slot stream on AI\_D. See ES 201 803-2-3 [6] clause 6.1.13.6.

sII (A\_So): The indirect multiplexing (performed by the TT\_So) of 0, 1 or 2 idle markers prior to the initial segment (see clause 6) by assertion of the Idle Insertion signal (sII). The number of idle markers is given by the frequency justification process, see ES 201 803-2-3 [6] clauses 6.1.12.1 and 6.1.13.6.

sPSI (A\_So): The Performance Supervision Insertion signal (sPSI) is asserted when the performance supervision special marker of a segment is to be transmitted according to clause 6, else it is de-asserted. See ES 201 803-2-3 [6] clause 6.1.13.6.

The continuous monitoring of the deviation in phase between the incoming signal and the transmitted signal is performed in order do perform frequency justifications. See ES 201 803-2-3 [6] clause 6.1.8.1.

The performance of positive justification when the incoming signal rate is above the nominal signal rate, by the transmission of a data in replacement of an idle-marker where positive justification is allowed. See ES 201 803-2-3 [6] clause 6.1.8.1. For justification opportunity, see clause 8.1.

The performance of negative justification when the incoming signal rate is below the nominal signal rate, by the transmission of an idle-marker in place of data where negative justification is allowed. See ES 201 803-2-3 [6] clause 6.1.8.1. For justification opportunity, see clause 8.1.

nFJ+: The positive frequency justification anomaly (nFJ+) is asserted when a positive frequency justification has occurred, else it is de-asserted. See ES 201 803-2-3 [6] clause 6.1.8.1.

nFJ-: The negative frequency justification anomaly (nFJ-) is asserted when a negative frequency justification has occurred, else it is de-asserted. See ES 201 803-2-3 [6] clause 6.1.8.1.

AIS: The Alarm Indication Signal (AIS) insertion into AI\_D instead of received signal when the CI\_SSF signal is asserted. See ES 201 803-2-3 [6] clause 6.1.5.1.

#### **Defects:**

None.

#### **Consequent actions:**

aAIS: The Alarm Indication Signal action (aAIS) is asserted when the Server Signal Fail (SSF) is asserted. See ES 201 803-2-3 [6] clause 6.3.1.1.

$aAIS \leftarrow CI\_SSF.$

#### **Defect correlation:**

None.

#### **Performance monitoring:**

pFJ+ (A\_So): The Positive Frequency Justification performance (pFJ+) is the number of positive frequency justifications anomalies (nFJ+) that has occurred during 1 second. See ES 201 803-2-3 [6] clause 6.5.3.1.

$$pFJ+ \ \leftarrow \ \Sigma \ nFJ+.$$

pFJ- (A\_So): The Negative Frequency Justification performance (pFJ-) is the number of negative frequency justifications anomalies (nFJ-) that has occurred during 1 second. See ES 201 803-2-3 [6] clause 6.5.3.2.

pFJ-

$$\leftarrow \Sigma$$

nFJ-.

#### **Output mapping:**

$AP0\_AI\_D \leftarrow AI\_D$ .

$AP0\_AI\_CK \leftarrow AP0\_TI\_CK.$

$AP0\_AI\_II \leftarrow sII.$

$AP0\_AI\_PSI \leftarrow sPSI$ .

$AP0\_AI\_TSF \leftarrow AP0\_CI\_SSF.$

$AP0/S2\_A\_So\_MI\_pFJ+ \leftarrow pFJ+.$

$AP0/S2\_A\_So\_MI\_pFJ- \leftarrow pFJ-.$

#### **Fault management:**

None.

#### Long term performance monitoring:

FJ+(t-10) (A\_Sk): The delayed positive Frequency Justification performance counter (FJ+(t-10)) is the 10 second delayed value of the positive Frequency Justification performance counter (pFJ+). See ES 201 803-2-3 [6] clause 6.8.5.2.

FJ-(t-10) (A\_Sk): The delayed negative Frequency Justification performance counter (FJ-(t-10)) is the 10 second delayed value of the negative Frequency Justification performance counter (pFJ-). See ES 201 803-2-3 [6] clause 6.8.5.2.

Application 0 to SDH Lower order path S2 Adaptation Sink function (AP0/S2\_A\_Sk)

27

Symbol:

5.4.3.2

Figure 14: Application 0 to SDH Lower order path Adaptation Sink (AP0/S2\_A\_Sk)

#### **Interfaces:**

Table 8: AP0/S2\_A\_Sk Input and output signals

| Input(s)   | Output(s)           |

|------------|---------------------|

| AP0_AI_D   | S2_CI_D             |

| AP0_AI_CK  | S2_CI_CK            |

| AP0_AI_II  | S2_CI_FS            |

| AP0_AI_PSI | S2_CI_SSF           |

| AP0_AI_TSF | AP0/S2_A_Sk_MI_cAIS |

|            | AP0/S2_A_Sk_MI_cLOJ |

#### **Processes and anomalies:**

The monitoring of frame alignment pattern in order to identify the initial segment of a multi-segment VC-2 transport stream according to clause 8.2.1. See ES 201 803-2-3 [6] clause 6.1.9.4.

sFS: When the initial segment is detected and the first of its data words is transmitted on CI\_D shall the Frame Start signal (sFS) be asserted, else it shall be de-asserted. See ES 201 803-2-3 [6] clause 6.1.9.4.

nLOJ: If the initial segment does not occur after the specified justification, then the Loss Of Justification anomaly (nLOJ) is asserted, else nLOJ is not asserted. See clause 8.2.1 and ES 201 803-2-3 [6] clause 6.1.9.4.

The demultiplexing of the initial slot and 53 contiguous data slots from the slot stream on AI\_D. See ES 201 803-2-3 [6] clause 6.1.13.6.

The demultiplexing of the initial slot to the section alignment signal. See ES 201 803-2-3 [6] clause 6.1.13.6.

The demultiplexing of the data slots into 8 contiguous octets in the VC-2 octet stream. See ES 201 803-2-3 [6] clause 6.1.13.6.

The reconstruction of the VC-2 octet stream from the received segments as specified in clause 8. See ES 201 803-2-3 [6] clause 6.1.13.5.

The clock smoothing process in order to reduce phase deviations on the transmitted signal. The clock smoothing must comply with the jitter and wander requirements as defined in EN 300 417-1-1 [1]. The resulting clock is delivered as CI\_CK. See ES 201 803-2-3 [6] clause 6.1.11.3.

The elastic buffering of the transported signal such that the buffer output is being clocked by the smoothed clock. See ES 201 803-2-3 [6] clause 6.1.11.3.

AIS (A\_Sk): The Alarm Indication Signal (AIS) insertion into CI\_D instead of received data when the Alarm Indication Signal defect (dAIS) is asserted. See ES 201 803-2-3 [6] clause 6.1.5.1.

nAIS: The Alarm Indication Signal anomaly (nAIS) is asserted when an AIS-marker is being detected in the AI\_D stream. See ES 201 803-2-3 [6] clause 6.1.5.1.

#### **Defects:**

The justification persistence state machine monitors the Loss Of Justification anomaly (nLOJ). The default state is Out Of Frame (OOF). When in the OOF state the nLOJ is not asserted on three consecutive justification opportunities, the state of the machine shall change to In Frame (IF). When in the IF state the nLOJ is asserted on five consecutive justification opportunities, the state of the machine shall change to OOF. See ES 201 803-2-3 [6] clause 6.2.4.2.

dLOJ: The Loss Of Justification defect (dLOJ) shall be asserted when the justification persistence state machine is in the OOF state. See ES 201 803-2-3 [6] clause 6.2.4.2.

dAIS (A\_Sk): The Alarm Indication Signal defect (dAIS) is asserted when the Alarm Indication Signal anomaly (nAIS) is asserted for more than three consecutive DTM frames, else it is not asserted. See ES 201 803-2-3 [6] clause 6.2.6.1.

#### **Consequent actions:**

aAIS: The Alarm Indication Signal action (aAIS) is asserted when the Loss Of Justification defect (dLOJ), the Alarm Indication Signal defect (dAIS) is asserted or the Trail Signal Fail (AI\_TSF) is. See ES 201 803-2-3 [6] clause 6.3.1.1.

$aAIS \leftarrow dLOJ \text{ or } dAIS \text{ or } AI\_TSF.$

aSSF: The Server Signal Fail action (aSSF) is asserted when the Alarm Indication Signal defect (dAIS) is asserted, the Trail Signal Fail (AI\_TSF) is asserted or the Loss Of Justification defect (dLOJ) is asserted. See ES 201 803-2-3 [6] clause 6.3.1.2.

$aSSF \leftarrow dAIS \text{ or AI TSF or dLOJ}.$

#### **Defect correlation:**

cLOJ: The Loss Of Justification cause (cLOJ) is asserted when the Loss Of Justification defect (dLOJ) is asserted, the Alarm Indication Signal defect (dAIS) not asserted and Trail Signal Fail (AI\_TSF) is not asserted. See ES 201 803-2-3 [6] clause 6.4.4.2.

$cLOJ \leftarrow dLOJ$  and (not dAIS) and (not AI\_TSF).

cAIS: The Alarm Indication Signal cause (cAIS) is asserted when the Alarm Indication Signal defect (dAIS) is asserted and the Trail Signal Failure (AI\_TSF) is not asserted. See ES 201 803-2-3 [6] clause 6.4.6.1.

$cAIS \leftarrow dAIS \text{ and (not AI\_TSF)}$

#### **Performance monitoring:**

None.

#### **Output mapping:**

S2 CI D  $\leftarrow$  CI D.

$S2_CI_CK \leftarrow CI_CK$ .

$S2\_CI\_FS \leftarrow sFS$ .

S2 CI SSF  $\leftarrow$  aSSF.

$AP0/S2\_A\_Sk\_MI\_cLOJ \leftarrow cLOJ$ .

$AP0/S2\_A\_Sk\_MI\_cAIS \leftarrow cAIS$ .

#### Fault management:

fAIS (A\_Sk): The Alarm Indication Signal fault (fAIS) is asserted when the Alarm Indication Signal cause (cAIS) is asserted consistently for  $2.5 \pm 0.5$  seconds and not asserted when the cAIS have been not asserted for  $10 \pm 0.5$  seconds. See ES 201 803-2-3 [6] clause 6.6.1.3.

fLOJ (A\_Sk): The Loss Of Justification fault (fLOF) is asserted when the Loss Of Justification cause (cLOJ) is asserted consistently for  $2.5 \pm 0.5$  seconds and not asserted when the cLOJ have been not asserted for  $10 \pm 0.5$  seconds. See ES 201 803-2-3 [6] clause 6.6.1.6.

#### Long term performance monitoring:

None.

# 5.4.4 DTM Application 0/SDH Lower order S12 path Adaptation function (AP0/S12\_A)

This clause describes the SDH VC-12 adaptation using DCAP-0 trail terminators.

# 5.4.4.1 Application 0 to SDH Lower order path S12 Adaptation Source function (AP0/S12\_A\_So)

Symbol:

Figure 15: DTM Application 0/SDH Lower order path S12 Adaptation Source (AP0/S12 A So)

#### **Interfaces:**

Table 9: AP0/S12\_A\_So Input and output signals

| Input(s)                | Output(s)            |

|-------------------------|----------------------|

| S12_CI_D                | AP0_AI_D             |

| S12_CI_CK               | AP0_AI_CK            |

| S12_CI_FS               | AP0_AI_II            |

| S12_CI_SSF              | AP0_AI_PSI           |

| AP0_TI_CK               | AP0_AI_TSF           |

| AP0_TI_FS               | AP0/S12_A_So_MI_pFJ- |

| AP0/S12_A_So_MI_1second | AP0/S12_A_So_MI_pFJ+ |

#### **Processes and anomalies:**

The generation of frame alignment pattern in order to indicate the initial segment of a multi-segment VC-12 transport stream according to clause 9.2.1. See ES 201 803-2-3 [6] clause 6.1.9.4.

The division of the VC-12 octet stream into segments as specified in clause 9. See ES 201 803-2-3 [6] clause 6.1.13.5.

The multiplexing of the section alignment signal and the 4 first octets of the segment into an initial slot. See ES 201 803-2-3 [6] clause 6.1.13.6.

The multiplexing of 8 contiguous octets in the segment into a data slot. See ES 201 803-2-3 [6] clause 6.1.13.6.

The multiplexing of an initial slot and 17 contiguous data slots into a slot stream on AI\_D. See ES 201 803-2-3 [6] clause 6.1.13.6.

sII (A\_So): The indirect multiplexing (performed by the TT\_So) of 0, 1 or 2 idle markers prior to the initial segment (see clause 6) by assertion of the Idle Insertion signal (sII). The number of idle markers is given by the frequency justification process, see ES 201 803-2-3 [6] clauses 6.1.12.1 and 6.1.13.6.

sPSI (A\_So): The Performance Supervision Insertion signal (sPSI) is asserted when the performance supervision special marker of a segment is to be transmitted according to clause 6, else it is de-asserted. See ES 201 803-2-3 [6] clause 6.1.13.6.

The continuous monitoring of the deviation in phase between the incoming signal and the transmitted signal is performed in order do perform frequency justifications. See ES 201 803-2-3 [6] clause 6.1.8.1.

The performance of positive justification when the incoming signal rate is above the nominal signal rate, by the transmission of a data in replacement of an idle-marker where positive justification is allowed. See ES 201 803-2-3 [6] clause 6.1.8.1. For justification opportunity, see clause 9.1.

The performance of negative justification when the incoming signal rate is below the nominal signal rate, by the transmission of an idle-marker in place of data where negative justification is allowed. See ES 201 803-2-3 [6] clause 6.1.8.1. For justification opportunity, see clause 9.1.

nFJ+: The positive frequency justification anomaly (nFJ+) is asserted when a positive frequency justification has occurred, else it is de-asserted. See ES 201 803-2-3 [6] clause 6.1.8.1.

nFJ-: The negative frequency justification anomaly (nFJ-) is asserted when a negative frequency justification has occurred, else it is de-asserted. See ES 201 803-2-3 [6] clause 6.1.8.1.

AIS: The Alarm Indication Signal (AIS) insertion into AI\_D instead of received signal when the CI\_SSF signal is asserted. See ES 201 803-2-3 [6] clause 6.1.5.1.

#### **Defects:**

None.

#### **Consequent actions:**

aAIS: The Alarm Indication Signal action (aAIS) is asserted when the Server Signal Fail (SSF) is asserted. See ES 201 803-2-3 [6] clause 6.3.1.1.

$aAIS \leftarrow CI\_SSF.$

#### **Defect correlation:**

None.

#### **Performance monitoring:**

pFJ+ (A\_So): The Positive Frequency Justification performance (pFJ+) is the number of positive frequency justifications anomalies (nFJ+) that has occurred during 1 second. See ES 201 803-2-3 [6] clause 6.5.3.1.

$$pFJ+ \leftarrow \Sigma nFJ+.$$

pFJ- (A\_So): The Negative Frequency Justification performance (pFJ-) is the number of negative frequency justifications anomalies (nFJ-) that has occurred during 1 second. See ES 201 803-2-3 [6] clause 6.5.3.2.

pFJ-  $\leftarrow \Sigma$  nFJ-.

#### **Output mapping:**

$AP0\_AI\_D \leftarrow AI\_D$ .

$AP0\_AI\_CK \leftarrow AP0\_TI\_CK$ .

$AP0\_AI\_II \leftarrow sII.$

$AP0\_AI\_PSI \leftarrow sPSI$ .

$AP0\_AI\_TSF \leftarrow AP0\_CI\_SSF.$

$AP0/S12\_A\_So\_MI\_pFJ+ \leftarrow pFJ+.$

$AP0/S12\_A\_So\_MI\_pFJ- \leftarrow pFJ-.$

#### Fault management:

None.

#### Long term performance monitoring:

FJ+(t-10) (A\_Sk): The delayed positive Frequency Justification performance counter (FJ+(t-10)) is the 10 second delayed value of the positive Frequency Justification performance counter (pFJ+). See ES 201 803-2-3 [6] clause 6.8.5.2.

FJ-(t-10) (A\_Sk): The delayed negative Frequency Justification performance counter (FJ-(t-10)) is the 10 second delayed value of the negative Frequency Justification performance counter (pFJ-). See ES 201 803-2-3 [6] clause 6.8.5.2.

# 5.4.4.2 Application 0 to SDH Lower order path S12 Adaptation Sink function (AP0/S12\_A\_Sk)

Symbol:

Figure 16: Application 0 to SDH Lower order path S12 Adaptation Sink (AP0/S12\_A\_Sk)

#### **Interfaces:**

Table 10: AP0/S12\_A\_Sk Input and output signals

| Input(s)   | Output(s)            |

|------------|----------------------|

| AP0_AI_D   | S12_CI_D             |

| AP0_AI_CK  | S12_CI_CK            |

| AP0_AI_II  | S12_CI_FS            |

| AP0_AI_PSI | S12_CI_SSF           |

| AP0_AI_TSF | AP0/S12_A_Sk_MI_cAIS |

|            | AP0/S12_A_Sk_MI_cLOJ |

#### **Processes and anomalies:**

The monitoring of frame alignment pattern in order to identify the initial segment of a multi-segment VC-12 transport stream according to clause 9.2.1. See ES 201 803-2-3 [6] clause 6.1.9.4.

sFS: When the initial segment is detected and the first of its data words is transmitted on CI\_D shall the Frame Start signal (sFS) be asserted, else it shall be de-asserted. See ES 201 803-2-3 [6] clause 6.1.9.4.

nLOJ: If the initial segment does not occur after the specified justification, then the Loss Of Justification anomaly (nLOJ) is asserted, else nLOJ is not asserted. See clause 9.2.1 and ES 201 803-2-3 [6] clause 6.1.9.4.

The demultiplexing of the initial slot and 17 contiguous data slots from the slot stream on AI\_D. See ES 201 803-2-3 [6] clause 6.1.13.6.

The demultiplexing of the initial slot to the section alignment signal and the 4 first octets of the segment. See ES 201 803-2-3 [6] clause 6.1.13.6.

The demultiplexing of the data slots into 8 contiguous octets in the VC-12 octet stream. See ES 201 803-2-3 [6] clause 6.1.13.6.

The reconstruction of the VC-12 octet stream from the received segments as specified in clause 9. See ES 201 803-2-3 [6] clause 6.1.13.5.

The clock smoothing process in order to reduce phase deviations on the transmitted signal. The clock smoothing must comply with the jitter and wander requirements as defined in EN 300 417-1-1 [1]. The resulting clock is delivered as CI CK. See ES 201 803-2-3 [6] clause 6.1.11.3.

The elastic buffering of the transported signal such that the buffer output is being clocked by the smoothed clock. See ES 201 803-2-3 [6] clause 6.1.11.3.

AIS (A\_Sk): The Alarm Indication Signal (AIS) insertion into CI\_D instead of received data when the Alarm Indication Signal defect (dAIS) is asserted. See ES 201 803-2-3 [6] clause 6.1.5.1.

nAIS: The Alarm Indication Signal anomaly (nAIS) is asserted when an AIS-marker is being detected in the AI\_D stream. See ES 201 803-2-3 [6] clause 6.1.5.1.

#### **Defects:**

The justification persistence state machine monitors the Loss Of Justification anomaly (nLOJ). The default state is Out Of Frame (OOF). When in the OOF state the nLOJ is not asserted on three consecutive justification opportunities, the state of the machine shall change to In Frame (IF). When in the IF state the nLOJ is asserted on five consecutive justification opportunities, the state of the machine shall change to OOF. See ES 201 803-2-3 [6] clause 6.2.4.2.

dLOJ: The Loss Of Justification defect (dLOJ) shall be asserted when the justification persistence state machine is in the OOF state. See ES 201 803-2-3 [6] clause 6.2.4.2.

dAIS (A\_Sk): The Alarm Indication Signal defect (dAIS) is asserted when the Alarm Indication Signal anomaly (nAIS) is asserted for more than three consecutive DTM frames, else it is not asserted. See ES 201 803-2-3 [6] clause 6.2.6.1.

#### **Consequent actions:**

aAIS: The Alarm Indication Signal action (aAIS) is asserted when the Loss Of Justification defect (dLOJ), the Alarm Indication Signal defect (dAIS) is asserted or the Trail Signal Fail (AI\_TSF) is. See ES 201 803-2-3 [6] clause 6.3.1.1.

$aAIS \leftarrow dLOJ \text{ or } dAIS \text{ or } AI\_TSF.$

aSSF: The Server Signal Fail action (aSSF) is asserted when the Alarm Indication Signal defect (dAIS) is asserted, the Trail Signal Fail (AI\_TSF) is asserted or the Loss Of Justification defect (dLOJ) is asserted. See ES 201 803-2-3 [6] clause 6.3.1.2.

$aSSF \leftarrow dAIS \text{ or } AI\_TSF \text{ or } dLOJ.$

#### **Defect correlation:**

cLOJ: The Loss Of Justification cause (cLOJ) is asserted when the Loss Of Justification defect (dLOJ) is asserted, the Alarm Indication Signal defect (dAIS) not asserted and Trail Signal Fail (AI\_TSF) is not asserted. See ES 201 803-2-3 [6] clause 6.4.4.2.

$cLOJ \leftarrow dLOJ$  and (not dAIS) and (not AI\_TSF).

cAIS: The Alarm Indication Signal cause (cAIS) is asserted when the Alarm Indication Signal defect (dAIS) is asserted and the Trail Signal Failure (AI\_TSF) is not asserted. See ES 201 803-2-3 [6] clause 6.4.6.1.

$cAIS \leftarrow dAIS \text{ and (not AI\_TSF)}$

#### **Performance monitoring:**

None.

#### **Output mapping:**

$S12_CI_D \leftarrow CI_D$ .

$S12\_CI\_CK \leftarrow CI\_CK$ .

$S12\_CI\_FS \leftarrow sFS$ .

$S12\_CI\_SSF \leftarrow aSSF$ .

$AP0/S12\_A\_Sk\_MI\_cLOJ \leftarrow cLOJ$ .

$AP0/S12\_A\_Sk\_MI\_cAIS \leftarrow cAIS.$

#### Fault management:

fAIS (A\_Sk): The Alarm Indication Signal fault (fAIS) is asserted when the Alarm Indication Signal cause (cAIS) is asserted consistently for  $2.5 \pm 0.5$  seconds and not asserted when the cAIS have been not asserted for  $10 \pm 0.5$  seconds. See ES 201 803-2-3 [6] clause 6.6.1.3.

fLOJ (A\_Sk): The Loss Of Justification fault (fLOF) is asserted when the Loss Of Justification cause (cLOJ) is asserted consistently for  $2,5\pm0,5$  seconds and not asserted when the cLOJ have been not asserted for  $10\pm0,5$  seconds. See ES 201 803-2-3 [6] clause 6.6.1.6.

#### Long term performance monitoring:

None.

# 5.4.5 DTM Application 0/SDH Lower order S11 path Adaptation function (AP0/S11\_A)

This clause describes the SDH VC-11 adaptation using DCAP-0 trail terminators.

# 5.4.5.1 Application 0 to SDH Lower order path S11 Adaptation Source function (AP0/S11\_A\_So)

Symbol:

Figure 17: DTM Application 0/SDH Lower order path S11 Adaptation Source (AP0/S11 A So)

#### Interfaces:

Table 11: AP0/S11\_A\_So Input and output signals

| Input(s)                | Output(s)            |  |  |  |

|-------------------------|----------------------|--|--|--|

| S11_CI_D                | AP0_AI_D             |  |  |  |

| S11_CI_CK               | AP0_AI_CK            |  |  |  |

| S11_CI_FS               | AP0_AI_II            |  |  |  |

| S11_CI_SSF              | AP0_AI_PSI           |  |  |  |

| AP0_TI_CK               | AP0_AI_TSF           |  |  |  |

| AP0_TI_FS               | AP0/S11_A_So_MI_pFJ- |  |  |  |

| AP0/S11_A_So_MI_1second | AP0/S11_A_So_MI_pFJ+ |  |  |  |

#### Processes and anomalies:

The generation of frame alignment pattern in order to indicate the initial segment of a multi-segment VC-11 transport stream according to clause 10.2.1. See ES 201 803-2-3 [6] clause 6.1.9.4.

The division of the VC-11 octet stream into segments as specified in clause 10. See ES 201 803-2-3 [6] clause 6.1.13.5.

The multiplexing of the section alignment signal and the 4 first octets of the segment into an initial slot. See ES 201 803-2-3 [6] clause 6.1.13.6.

The multiplexing of 8 contiguous octets in the segment into a data slot. See ES 201 803-2-3 [6] clause 6.1.13.6.

The multiplexing of an initial slot and 13 contiguous data slots into a slot stream on AI\_D. See ES 201 803-2-3 [6] clause 6.1.13.6.

34

sII (A\_So): The indirect multiplexing (performed by the TT\_So) of 0, 1 or 2 idle markers prior to the initial segment (see clause 6) by assertion of the Idle Insertion signal (sII). The number of idle markers is given by the frequency justification process, see ES 201 803-2-3 [6] clauses 6.1.12.1 and 6.1.13.6.

sPSI (A\_So): The Performance Supervision Insertion signal (sPSI) is asserted when the performance supervision special marker of a segment is to be transmitted according to clause 6, else it is de-asserted. See ES 201 803-2-3 [6] clause 6.1.13.6.

The continuous monitoring of the deviation in phase between the incoming signal and the transmitted signal is performed in order do perform frequency justifications. See ES 201 803-2-3 [6] clause 6.1.8.1.

The performance of positive justification when the incoming signal rate is above the nominal signal rate, by the transmission of a data in replacement of an idle-marker where positive justification is allowed. See ES 201 803-2-3 [6] clause 6.1.8.1. For justification opportunity, see clause 10.1.

The performance of negative justification when the incoming signal rate is below the nominal signal rate, by the transmission of an idle-marker in place of data where negative justification is allowed. See ES 201 803-2-3 [6] clause 6.1.8.1. For justification opportunity, see clause 10.1.

nFJ+: The positive frequency justification anomaly (nFJ+) is asserted when a positive frequency justification has occurred, else it is de-asserted. See ES 201 803-2-3 [6] clause 6.1.8.1.

nFJ-: The negative frequency justification anomaly (nFJ-) is asserted when a negative frequency justification has occurred, else it is de-asserted. See ES 201 803-2-3 [6] clause 6.1.8.1.

AIS: The Alarm Indication Signal (AIS) insertion into AI\_D instead of received signal when the CI\_SSF signal is asserted. See ES 201 803-2-3 [6] clause 6.1.5.1.