ETSI Standard

# Dynamic synchronous Transfer Mode (DTM); Part 4: Mapping of DTM frames into SDH containers

## Reference

DES/TM-01093

Keywords

architecture, DTM, protocol, SDH, switching, transmission

#### **ETSI**

650 Route des Lucioles F-06921 Sophia Antipolis Cedex - FRANCE

Tel.: +33 4 92 94 42 00 Fax: +33 4 93 65 47 16

Siret N° 348 623 562 00017 - NAF 742 C Association à but non lucratif enregistrée à la Sous-Préfecture de Grasse (06) N° 7803/88

#### Important notice

Individual copies of the present document can be downloaded from: <u>http://www.etsi.org</u>

The present document may be made available in more than one electronic version or in print. In any case of existing or perceived difference in contents between such versions, the reference version is the Portable Document Format (PDF). In case of dispute, the reference shall be the printing on ETSI printers of the PDF version kept on a specific network drive within ETSI Secretariat.

Users of the present document should be aware that the document may be subject to revision or change of status.

Information on the current status of this and other ETSI documents is available at

<a href="http://portal.etsi.org/tb/status/status.asp">http://portal.etsi.org/tb/status/status.asp</a></a>

If you find errors in the present document, send your comment to: <a href="mailto:editor@etsi.org">editor@etsi.org</a>

#### **Copyright Notification**

No part may be reproduced except as authorized by written permission. The copyright and the foregoing restriction extend to reproduction in all media.

© European Telecommunications Standards Institute 2002. All rights reserved.

**DECT**<sup>TM</sup>, **PLUGTESTS**<sup>TM</sup> and **UMTS**<sup>TM</sup> are Trade Marks of ETSI registered for the benefit of its Members. **TIPHON**<sup>TM</sup> and the **TIPHON logo** are Trade Marks currently being registered by ETSI for the benefit of its Members. **3GPP**<sup>TM</sup> is a Trade Mark of ETSI registered for the benefit of its Members and of the 3GPP Organizational Partners.

# Contents

| Intell | ectual Property Rights | S                                                        | 4  |

|--------|------------------------|----------------------------------------------------------|----|

| Fore   | word                   |                                                          | 4  |

| Intro  | duction                |                                                          | 4  |

| 1      | Scope                  |                                                          | 6  |

| 2      | References             |                                                          | 6  |

| 3      | Definitions and abbro  | eviations                                                | 7  |

| 3.1    |                        |                                                          |    |

| 3.2    | Abbreviations          |                                                          | 8  |

| 4      | Overview               |                                                          | 8  |

| 5      | SDH Higher order pa    | ath/DTM Physical Link layer                              | 10 |

| 5.1    |                        | n                                                        |    |

| 5.2    |                        | ons                                                      |    |

| 5.3    | Adaptation function    | 18                                                       | 11 |

| 5.3.1  | SDH VC-n to D          | TM Bypass layer type 2 Adaptation S4/BP2_A               | 11 |

| 5.3.1. |                        | to DTM Bypass layer type 2 Adaptation source S4/BP2_A_So |    |

| 5.3.1. | 2 SDH VC-n t           | o DTM Bypass layer type 2 Adaptation sink S4/BP2_A_Sk    | 12 |

| 6      | Mapping of DTM fra     | ames into VC-4                                           | 13 |

| 6.1    | VC-4 structure         |                                                          | 14 |

| 6.2    | DTM Slot mapping       |                                                          | 14 |

| 6.3    | Slot format            |                                                          | 16 |

| Anno   | ex A (informative):    | STM-n Synchronization                                    | 17 |

| Anno   | ex B (informative):    | Bibliography                                             | 18 |

| Histo  | rv                     |                                                          | 19 |

## Intellectual Property Rights

IPRs essential or potentially essential to the present document may have been declared to ETSI. The information pertaining to these essential IPRs, if any, is publicly available for **ETSI members and non-members**, and can be found in ETSI SR 000 314: "Intellectual Property Rights (IPRs); Essential, or potentially Essential, IPRs notified to ETSI in respect of ETSI standards", which is available from the ETSI Secretariat. Latest updates are available on the ETSI Web server (<a href="http://webapp.etsi.org/IPR/home.asp">http://webapp.etsi.org/IPR/home.asp</a>).

Pursuant to the ETSI IPR Policy, no investigation, including IPR searches, has been carried out by ETSI. No guarantee can be given as to the existence of other IPRs not referenced in ETSI SR 000 314 (or the updates on the ETSI Web server) which are, or may be, or may become, essential to the present document.

## **Foreword**

This ETSI Standard (ES) has been produced by ETSI Technical Committee Transmission and Multiplexing (TM), and is now submitted for the ETSI standards Membership Approval Procedure.

The present document is part 4 of a multi-part deliverable covering Dynamic synchronous Transfer Mode (DTM), as identified below:

```

Part 1:

"System description";

Part 2:

"System characteristics";

Part 3:

"Physical protocol";

Part 4:

"Mapping of DTM frames into SDH containers";

Part 5:

"Mapping of PDH over DTM";

Part 6:

"Mapping of SDH over DTM";

Part 7:

"Ethernet over DTM Mapping";

Part 8:

"Mapping of Frame relay over DTM";

Part 9:

"Mapping of ATM over DTM";

Part 10:

"Routeing and switching of IP flows over DTM";

"Mapping of video streams over DTM";

Part 11:

Part 12:

"Mapping of MPLS over DTM";

Part 13:

"System description of sub-rate DTM";

Part 14:

"Network management".

```

## Introduction

Dynamic synchronous Transfer Mode (DTM) is a time division multiplex and a circuit-switched network technique that combines switching and transport.

Part 1 describes the general properties of DTM and the DTM service over a unidirectional data channel. The overall system architecture is described and fundamental functions are identified.

Part 2 includes system aspects that are mandatory or optional for nodes from different vendors to interoperate. The interworking granularity should be at node level, such that nodes from different vendors can interoperate with regard to well-defined functions.

5

Part 3 specifies the physical layer for physical links based on 8B10B encoding.

The present document (Part 4) describes how DTM frames are mapped onto SDH containers.

The transport of various tributary signals is specified for PDH (Part 5), SDH (Part 6), Ethernet (Part 7), Frame Relay (Part 8), ATM (Part 9), IP (Part 10), MPLS (Part 11), video streaming (Part 12).

Finally, management aspects are standardized in Part 13.

## 1 Scope

The present document:

- establishes a synchronous mapping of DTM frames into SDH VC-4 containers;

- specifies the characteristics of critical parameters for an SDH VC-4 based physical interface;

- gives terms and definitions for message encoding;

- gives terms and definitions for the frame format;

- gives terms and definitions for the sync transport;

- gives terms and definitions for the sync and physical link status.

## 2 References

The following documents contain provisions which, through reference in this text, constitute provisions of the present document.

- References are either specific (identified by date of publication and/or edition number or version number) or non-specific.

- For a specific reference, subsequent revisions do not apply.

- For a non-specific reference, the latest version applies.

- [1] ETSI ES 201 803-2-1: " Dynamic synchronous Transfer Mode (DTM); Part 2: System characteristics; Sub-part 1: Data link aspects".

- [2] ETSI EN 300 417-4-1: "Transmission and Multiplexing (TM); Generic requirements of transport functionality of equipment; Part 4-1: Synchronous Digital Hierarchy (SDH) path layer functions".

- [3] ETSI EN 300 417-6-1: "Transmission and Multiplexing (TM); Generic requirements of transport functionality of equipment; Part 6-1: Synchronization layer functions".

- [4] ETSI EN 300 462-6-1: "Transmission and Multiplexing (TM); Generic requirements for synchronization networks; Part 6-1: Timing characteristics of primary reference clocks".

- [5] ITU-T Recommendation G.707: "Network node interface for the synchronous digital hierarchy (SDH)".

- [6] ITU-T Recommendation G.781: "Synchronization layer functions".

- [7] ITU-T Recommendation G.783: "Characteristics of synchronous digital hierarchy (SDH) equipment functional blocks".

- [8] ITU-T Recommendation G.805: "Generic functional architecture of transport networks".

- [9] ITU-T Recommendation G.806: "Characteristics of Transport Equipment Description Methodology and Generic Functionality".

- [10] ITU-T Recommendation G.811: "Timing characteristics of primary reference clocks".

## 3 Definitions and abbreviations

#### 3.1 Definitions

For the purposes of the present document, the following terms and definitions apply:

**Access Point (AP):** "reference point" that consists of the pair of co-located "unidirectional access" points, and therefore represents the binding between the trail termination and adaptation functions (adopted from ITU-T Recommendation G.805)

**Adapted Information (AI):** information passing across an AP (see also ITU-T Recommendation G.805), (adopted from ITU-T Recommendation G.806)

**Alarm Indication Signal (AIS):** special marker sent in a data slot to mark the lack of transported data as a result of a defect in the transmission path

channel: set of slots allocated from one source access node to one or more destination access nodes in a network

**Characteristic Information (CI):** Signal with a specific format, which is transferred on "network connections". The specific formats will be defined in the technology specific Recommendations. The information passing across a CP or TCP. (Adopted from ITU-T Recommendations G.805 and G.806)

**Connection Point (CP):** reference point where the output of a trail termination source or a connection is bound to the input of another connection, or where the output of a connection is bound to the input of a trail termination sink or another connection (adopted from ITU-T Recommendation G.806)

**defect:** The density of anomalies has reached a level where the ability to perform a required function has been interrupted. Defects are used as input for performance monitoring, the control of consequent actions, and the determination of fault cause. (Adopted from ITU-T Recommendation G.806).

**frame:** set of slots forming an entity that is transmitted on a physical medium repeatedly every 125  $\mu s$  (nominally), i.e. 8 000 frames/second

idle: special marker sent in a data slot to mark the lack of transported data in the slot

Management Information (MI): signal passing across an access point (adopted from ITU-T Recommendation G.806)

**Management Point (MP):** A reference point where the output of an atomic function is bound to the input of the element management function, or where the output of the element management function is bound to the input of an atomic function. The MP is not the TMN Q3 interface. (Adopted from ITU-T Recommendation G.806).

**Performance Supervision (PS):** special marker sent with the data containing per channel Performance Supervision information

physical link: unidirectional connection between the transmitter of one port and the receiver of another port

**Server Signal Fail (SSF):** signal fail indication output at the CP of an adaptation function (adopted from ITU-T Recommendation G.806)

**Signal Fail (SF):** signal indicating the associated data has failed in the sense that a near-end defect condition (not being the degraded defect) is active (adopted from ITU-T Recommendation G.806)

**slot:** time slot within the frame being able to transport 64 bit of data or a number of special codes

**Trail Signal Fail (TSF):** signal fail indication output at the AP of a termination function (adopted from ITU-T Recommendation G.806)

## 3.2 Abbreviations

For the purposes of the present document, the following abbreviations apply:

A Adapted function

ACT Active

AI Adapted Information

AIS Alarm Indication Signal

AM Administrative Mode

AP Access Point

aSSF Server Signal Fail action

aTSF Trail Signal Fail action

AU-4 Administrative Unit, level 4

BPn ByPass layer type n

BPnP ByPass layer type n Protection CI Characteristic Information

CK ClocK

cTSF Trail Signal Fail cause

D Data

FS Frame Start signal MP Management Point PM Port Mode

POH Path OverHead

PS Performance Supervision SDH Synchronous Digital Hierarchy

Sk Sink

Sn SDH higher order VC-n layer (n=3,4,4-Xc)

So Source

SSF Server Signal Fail

SSM Synchronization Status Message STM Synchronous Transport Module

TS Time Slot layer TSF Trail Signal Fail

TSP Time Slot layer Protection

TST Time Slot layer Tunnel

TTI Trail Trace Identifier

VC Virtual Container

VC-4 Virtual Container, level 4

## 4 Overview

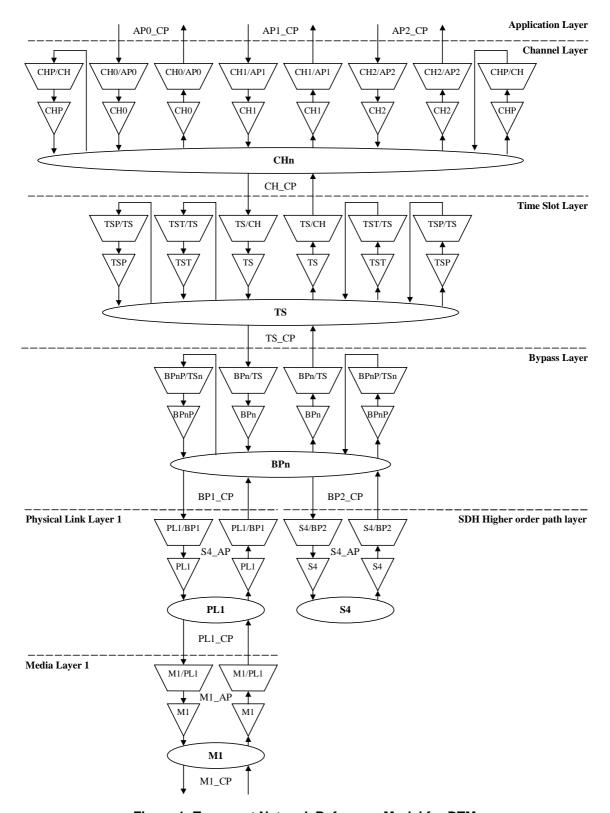

The Physical Layer Adaptation (see figure 1) describes the mapping and framing of the slots in the DTM frame synchronously into the SDH VC-4-Xc payload. The functionality is part of the SDH higher order path layer and additional adaptation functions and their inner workings are specified. The transport functionality provides a DTM Timeslot connection over an SDH network as if this where a physical link between the DTM nodes.

DTM slots, which may carry Data, Idle-marker, PS-marker or AIS-marker, is being encoded into a 65 bit format. The 65 bit slot representation is synchronously mapped onto the octet payload of an VC-4-Xc. The VC-4-Xc payload is also scrambled through a self-synchronous scrambler in order to ensure integrity. In the receiver end the reverse process is performed.

The DTM frame synchronization signal is being transferred over the AU-4 pointer adjustment mechanism.

The SDH supervision functionality is mapped over to the DTM functionality and SDH AIS is being encoded into DTM AIS. The DTM supervision includes port available supervision, which is being generated out of the SDH supervision signals.

Figure 1: Transport Network Reference Model for DTM

# 5 SDH Higher order path/DTM Physical Link layer

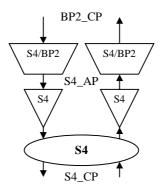

The SDH Higher order path section (see figure 2) provides adaptation for higher speeds PDH, ATM, HDLC, FDDI and DTM signals and multiplexing adaptation for SDH lower order part section. Only the DTM signal will be detailed in this clause.

Figure 2: SDH Higher order path section atomic functions (relating to DTM mapping)

The Characteristic Information and Adapted Information is defined in [7], clause 12.

Modelling is according to ITU-T Recommendation G.806 [9] with the exception of DTM specific modifications. These modifications is relating to:

- DTM layer labelling (BP2 for the DTM Bypass layer, type 2).

- Administrative Mode.

- Use of a signal (aTSF Trail Server Fail action) to the dynamic management protocols of DTM.

The Administrative Mode (AM) signal is sent to a port in order to control the administrative status as being enabled or disabled (or optionally auto). This signal control the administrative state machine having the states Active (ACT), Not Active (NACT) or optionally Automatic Active (AACT). The state machine is equivalent to that of the port mode as defined in ITU-T Recommendation G.806 [9].

## 5.1 Connection function

The SDH VC-n (n=4, 4-Xc) interconnection between input and output VC-n ports. See Sn connection function in [7], clause 12.1 and [2], clause 4.1.

#### 5.2 Termination functions

The SDH VC-n (n=4, 4-Xc) trail termination functions. See Sn trail termination function in [7], clause 12.2 and [2], clause 4.2.

## 5.3 Adaptation functions

## 5.3.1 SDH VC-n to DTM Bypass layer type 2 Adaptation S4/BP2\_A

### 5.3.1.1 SDH VC-n to DTM Bypass layer type 2 Adaptation source S4/BP2\_A\_So

#### **Symbols**

Figure 3: DTM Bypass layer type 2 to SDH Higher order path layer Adaptation function Source

#### **Interfaces**

Table 1: S4/BP2\_A\_So Input and output signals

| Input(s)  | Output(s) |

|-----------|-----------|

| BP2_CI_D  | S4_AI_D   |

| BP2_CI_CK | S4_AI_CK  |

| BP2_CI_FS | S4_AI_FS  |

#### **Processes**

The DTM frame synchronization transmission is achieved by letting the DTM BP2\_CI\_FS signal trigger the S4\_AI\_FS, i.e. by generating the POH header J1 octet whenever the BP2\_CI\_FS goes active.

The encoding of slots (from BP2\_CI\_D) into the 65 bit format is performed according to clause 6.3.

The format adaptation of 65 bit encoded slot words into the octet stream of 9 rows of 260 x n octets according to clause 6.2.

The scrambling of the octet stream is performed using a self-synchronous scrambler with the polynomial  $X^{43} + 1$  according to clause 6.1.

C2: The signal label shall be inserted according to clause 6.1.

F2, F3, H4 and K3: These unused octets shall be inserted according to clause 6.1.

#### **Defects**

None

#### **Consequent actions**

None

#### **Defect correlation**

None

#### **Performance monitoring**

None

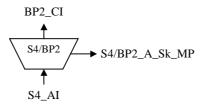

## 5.3.1.2 SDH VC-n to DTM Bypass layer type 2 Adaptation sink S4/BP2\_A\_Sk

12

#### **Symbols**

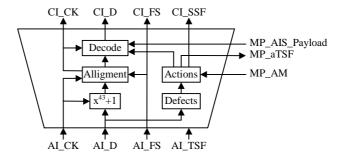

Figure 4: DTM Bypass layer type 2 from SDH Higher order path layer Adaptation function Sink

#### Interfaces

Input(s)

Output(s)

S4\_AI\_D

BP2\_CI\_D

S4\_AI\_CK

BP2\_CI\_CK

S4\_AI\_FS

BP2\_CI\_SSF

S4\_AI\_TSF

BP2\_CI\_FS

S4/BP2\_A\_Sk\_MP\_PM

S4/BP2\_A\_Sk\_MP\_aTSF

S4/BP2\_A\_Sk\_MP\_AM

S4/BP2\_A\_Sk\_MP\_cTSF

S4/BP2\_A\_Sk\_MP\_cPLM

S4/BP2\_A\_Sk\_MP\_nPUA

Table 2: S4/BP2\_A\_Sk Input and output signals

#### **Processes**

Figure 5: Partial view of Adaptation function sink

**C2:** The signal label, octet C2 is recovered and monitored. The PayLoad Mismatch defect (dPLM) is detected upon incorrect value of the C2 octet. For further description of signal label processing see [9], clause 6.2.4.2.

The de-scrambling of the octet stream by the use of a self synchronous scrambler with the polynomial  $X^{43} + 1$  according to clause 6.1.

The format adaptation of 65 bit encoded slot words from the octet stream of 9 rows of 260 x n octets according to clause 6.2.

The decoding of slots from the 65 bit format into BP2\_CI\_D slots according to clause 6.3.

S4/BP2\_A\_Sk\_MP\_TSF\_Reported

S4/BP2\_A\_Sk\_MP\_AIS\_Payload

S4/BP2\_A\_Sk\_MP\_1second

The AIS insertion into BP2\_CI\_D instead of received slots upon AIS defect (see [9], clause 6.3). The inserted AIS payload shall be according to ES 201 803-2-1 [1].

The DTM synchronization transmission is achieved by the processing of the received S4\_AI\_FS and issuing of an active DTM BP2\_CI\_FS.

#### **Defects**

dPLM: Defect detected due to incorrect signal label (C2), according to ITU-T Recommendation G.806 [9], clauses 6.2.4.2 and 6.1.

#### Consequent actions

The Server Signal Fail action (aSSF) may be the result of underlying failure (AI\_TSF) or the PayLoad Missmatch defect (dPLM).

$aSSF \leftarrow AI\_TSF \text{ or } dPLM$

The Trail Signal Fail action (aTSF), the port availability, may be the result of underlying failure (AI\_TSF), the payload mismatch (dPLM) or inactive port (NACT).

$aTSF \leftarrow AI\_TSF$  or dPLM or NACT

The Alarm Indication Signal action (aAIS) is activated of either the underlying failure (AI\_TSF), the payload mismatch (dPLM) or inactive port (NACT).

aAIS ← AI TSF or dPLM or NACT

#### **Defect correlation**

The PayLoad Mismatch cause (cPLM) is activated when the PayLoad Mismatch defect (dPLM) is active, but only if there is no underlying failure (AI\_TSF).

$cPLM \leftarrow dPLM \text{ and (not AI\_TSF)}$

The Trail Signal Fail cause (cTSF) is activated when the Trail Signal Fail signal (AI\_TSF) is active, and the TSF is to be reported (TSF\_Reported) and port mode is in state monitoring (MON), see ITU-T Recommendation G.806 [9], clause 6.4.

cTSF ← AI\_TSF and TSF\_Reported and MON

#### **Performance monitoring**

The Port UnAvailable performance (pPUA) is set active if the Trail Signal Fail action was active under the last second. A timing signal (MP\_1second) is given for timing reference.

pPUA← aTSF

## 6 Mapping of DTM frames into VC-4

DTM has nominally the same frame rate as SDH but is not synchronous to SDH. This means that the DTM frame can not be locked to a certain position in the VC-4 ITU-T Recommendation G.707 [5]. Two possibilities exist:

- Synchronous mapping into the VC-4: the DTM frame is locked to the VC-4.

- Asynchronous mapping into the VC-4: the DTM frame floats inside the VC-4.

The synchronous mapping is being specified in the present document. Asynchronous mapping is for further study.

## 6.1 VC-4 structure

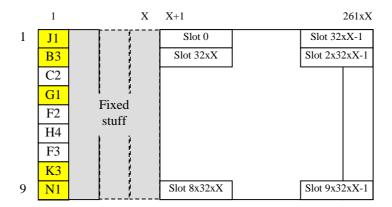

The VC-4/VC-4-Xc structure is found in figure 6. The shaded fields is unavailable in the S4\_AI\_D [2].

Figure 6: Structure of S4\_AI\_D with mapped DTM slots

The Path Overhead [5] octets J1, B3, G1, K3 and N1 are not available in the S4\_AP and is assumed to be handled according to [5]. The J1 octet is used for Trail Termination Identifier (TTI). The B3 octet is used for standard performance supervision. The G1, K3 and N1 used according to SDH specifications. As for the free portion of the K3, it is not used and is set to 000000000.

The Path Overhead octets C2, F2, F3 and H4 are available for a mapping usage. C2 shall be assigned the value of 00000101 for experimental encoding until a proper value has been assigned. The F2, F3 and H4 octets are currently not in use and should be set to the value of 00000000.

The entire VC-4-Xc payload containing the DTM frame is scrambled using the self-synchronous scrambler polynomial:

$$X^{43} + 1$$

## 6.2 DTM Slot mapping

Each slot takes up 65 bits, 1 special marker bit and 64 bits of data. Each slot is mapped into the octet stream giving the special marker bit first, and then the data bit 63 to 0.

|     |   |    |    | Oct | et e | ;  |    |    |    |    | C  | cte | t e+ | 1  |    |    |    | Octet e+2 e+6 |    | Τ   |    |    | C  | )cte | t e+ | 7  |   |   |   |   | C | )cte | t e+ | -8 |   |   |

|-----|---|----|----|-----|------|----|----|----|----|----|----|-----|------|----|----|----|----|---------------|----|-----|----|----|----|------|------|----|---|---|---|---|---|------|------|----|---|---|

| Bit | 1 | 2  | 3  | 4   | 5    | 6  | 7  | 8  | 1  | 2  | 3  | 4   | 5    | 6  | 7  | 8  | 1  |               | 8  | T   | 1  | 2  | 3  | 4    | 5    | 6  | 7 | 8 | 1 | 2 | 3 | 4    | 5    | 6  | 7 | 8 |

| f=0 | s | 63 | 62 | 61  | 60   | 59 | 58 | 57 | 56 | 55 | 54 | 53  | 52   | 51 | 50 | 49 | 48 |               | 9  | 1   | 8  | 7  | 6  | 5    | 4    | 3  | 2 | 1 | 0 |   |   |      |      |    |   |   |

| f=1 |   | s  | 63 | 62  | 61   | 60 | 59 | 58 | 57 | 56 | 55 | 54  | 53   | 52 | 51 | 50 | 49 |               | 10 | ) [ | 9  | 8  | 7  | 6    | 5    | 4  | 3 | 2 | 1 | 0 |   |      |      |    |   |   |

| f=2 |   |    | s  | 63  | 62   | 61 | 60 | 59 | 58 | 57 | 56 | 55  | 54   | 53 | 52 | 51 | 50 |               | 1  | 1 1 | 0  | 9  | 8  | 7    | 6    | 5  | 4 | 3 | 2 | 1 | 0 |      |      |    |   |   |

| f=3 |   |    |    | s   | 63   | 62 | 61 | 60 | 59 | 58 | 57 | 56  | 55   | 54 | 53 | 52 | 51 |               | 1: | 2 1 | 1  | 10 | 9  | 8    | 7    | 6  | 5 | 4 | 3 | 2 | 1 | 0    |      |    |   |   |

| f=4 |   |    |    |     | s    | 63 | 62 | 61 | 60 | 59 | 58 | 57  | 56   | 55 | 54 | 53 | 52 |               | 1: | 3 1 | 2  | 11 | 10 | 9    | 8    | 7  | 6 | 5 | 4 | 3 | 2 | 1    | 0    |    |   |   |

| f=5 |   |    |    |     |      | s  | 63 | 62 | 61 | 60 | 59 | 58  | 57   | 56 | 55 | 54 | 53 |               | 14 | 1 1 | 13 | 12 | 11 | 10   | 9    | 8  | 7 | 6 | 5 | 4 | 3 | 2    | 1    | 0  |   |   |

| f=6 |   |    |    |     |      |    | s  | 63 | 62 | 61 | 60 | 59  | 58   | 57 | 56 | 55 | 54 |               | 1: | 5 1 | 4  | 13 | 12 | 11   | 10   | 9  | 8 | 7 | 6 | 5 | 4 | 3    | 2    | 1  | 0 |   |

| f=7 |   |    |    |     |      |    |    | s  | 63 | 62 | 61 | 60  | 59   | 58 | 57 | 56 | 55 |               | 1  | 5 1 | 5  | 14 | 13 | 12   | 11   | 10 | 9 | 8 | 7 | 6 | 5 | 4    | 3    | 2  | 1 | 0 |

Figure 7: DTM slot to SDH octet alignment variants

Note that SDH bit order goes from 1 to 8 where 1 is the left most bit of the octet and is transmitted first. For the first octet of a row, bit 1 will be the special marker, bit 2 will be data bit 63, bit 3 will be data bit 62 etc.

The 65 bit format causes misalignment between the octet boundaries and slot boundaries (see figure 7) with a cycle of 65 octets (i.e. 8 slots). The boundaries are synchronized on the first data octet on each row. This mapping will produce exactly 32xX slots per row, giving 288xX slots per frame. In table 3 is the performance of an STM-N using a VC-4-Xc when X=N detailed.

Table 3: Performance table of DTM over VC-4 mapping

| Description            | Symbol             | STM-1   | STM-4   | STM-16    | STM-64    | STM-256    | Unit   |

|------------------------|--------------------|---------|---------|-----------|-----------|------------|--------|

| Signal speed           | f <sub>sig</sub>   | 155,52  | 622,08  | 2 488,32  | 9 953,28  | 39 813,12  | Mbps   |

| Payload size           | PS                 | 2 340   | 9 360   | 37 440    | 149 760   | 599 040    | octets |

| Bit rate               | BR                 | 149,76  | 599,04  | 2 396,16  | 9 584,64  | 38 338,56  | Mbps   |

| Slot count             | n <sub>data</sub>  | 288     | 1 152   | 4 608     | 18 432    | 73 728     | slots  |

| Physical Link bit rate | BR <sub>data</sub> | 147,456 | 589,824 | 2 359,296 | 9 437,184 | 37 748,736 | Mbps   |

The payload size (PS) is the size of the VC-4 payload.

$$PS = 260 \times 9 \times X$$

The bit rate (BR) is the bit rate of the VC-4 payload.

$$BR = PS \times 8 \times 8k = X \times 260 \times 9 \times 8 \times 8k = X \times 149760k$$

The nominal slot count (n<sub>slot</sub>) is a strict function of the payload size:

$$n_{slot} = PS \times \frac{8}{65} = X \times 260 \times 9 \times \frac{8}{65} = X \times 4 \times 9 \times 8 = X \times 288$$

The maximum bit rate available for channel traffic (including signalling) is strictly related to the number of data slots  $(n_{data})$  and thus the available physical link data bit rate  $(BR_{data})$  becomes:

$$BR_{data} = n_{data} \times 64 \times 8k = n_{data} \times 512k$$

The position (a,b,c) of a slot s in the VC-4-Xc data payload area is given from the equations:

$$a = \left\lfloor \frac{s}{32 \times X} \right\rfloor$$

$$b = \left\lfloor \frac{\left(s - a \times 32 \times X\right) \times 65}{8 \times X} \right\rfloor$$

$$c = \left\lfloor \frac{\left(s - a \times 32 \times X\right) \times 65 - b \times 8 \times X}{8} \right\rfloor$$

The initial octet e for a slot s is given by:

$$e = b \times X + c$$

The bit alignment variant f in the octet e is given by:

$$f = s \mod 8$$

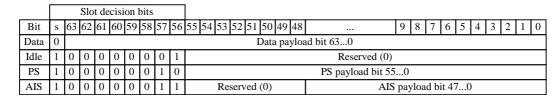

## 6.3 Slot format

Each slot is encoded with a special marker bit S and 64 bit of data bits. A slot may contain either 64-bit data, Idle-marker, PS-marker or AIS-marker (see figure 8). The PS-marker and AIS markers can hold up to 56 bits and 48 bits of non-user data respectively.

Figure 8: DTM Slot format and encoding

The special marker bit S marks data with the value of 0 and Idle, PS and AIS markers with the value of 1. For the case where the S bit is 1, only 3 patterns in the data bits of 63 to 56 implies special markers of Idle, PS and AIS, the other patterns are treated as if the special marker bit was faulty (i.e. of value 0) and thus the slot contains a 64-bit data word.

For a 64-bit data word, the S bit shall be 0 and the data bits 63 down to 0 will hold the data payload.

For the Idle-marker, the S bit shall be 1 and the data bits 63 down to 56 shall be 00000001. The data bit 55 down to 0 is reserved for future use and should be set to 0.

For the PS-marker, the S bit shall be 1 and the data bits 63 down to 56 shall be 00000010. The data bit 55 down to 0 is the PS-payload.

For the AIS-marker, the S bit shall be 1 and the data bits 63 down to 56 shall be 00000011. The data bit 55 down to 48 is reserved for future use and should be set to 0. The data bit 47 down to 0 is the AIS-payload.

# Annex A (informative): STM-n Synchronization

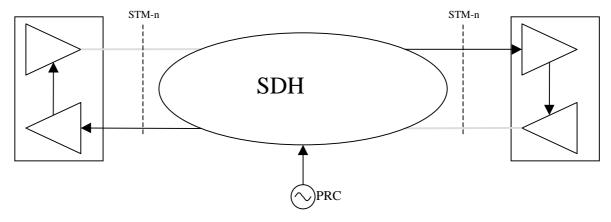

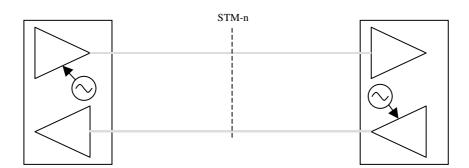

The DTM frame synchronization is not synchronous to the SDH frame. This implies that different physical links do not have to be synchronized to each other.

When used in an SDH network, the SDH synchronization is traceable to a PRC ITU-T Recommendation G.811 [10] and EN 300 462-6-1 [4]. Thus it is natural to slave the STM-n interface to the SDH network (see figure A.1).

Figure A.1: Connected to an SDH network

If the STM-n interfaces do not interface an SDH network, the simplest way is to synchronize the interface to the DTM node sync (see figure A.2).

Figure A.2: DPP-VC-4 without SDH network

In this case, the timing does not have to meet the SDH requirements.

Consequently, the STM-n interface has to support two and only two different timing modes:

- Loop timing.

- DTM Equipment Clock.

The choice of mode should be configured automatically by the synchronization status message *SSM* ITU-T Recommendation G.781 [6] and EN 300 417-6-1 [3] in the received S1 octet.

The transmitted S1 shall be set to 1111, not to be used for synchronization.

If the received SSM is 1111, then the DTM Equipment Clock be used as timing reference for the SDH transmit interface.

If the received SSM is better than 1111, then shall the receiver be used as timing reference for the SDH transmit interface, i.e. loop timing.

# Annex B (informative): Bibliography

ETSI ES 201 803-2-3: "Dynamic synchronous Transfer Mode (DTM); Part 2: System characteristics; Sub-part 3: Transport network and channel adaption aspects".

# History

|        | Document history |                               |                                       |  |  |  |  |  |  |  |  |

|--------|------------------|-------------------------------|---------------------------------------|--|--|--|--|--|--|--|--|

| V1.1.1 | October 2002     | Membership Approval Procedure | MV 20021220: 2002-10-22 to 2002-12-20 |  |  |  |  |  |  |  |  |

|        |                  |                               |                                       |  |  |  |  |  |  |  |  |

|        |                  |                               |                                       |  |  |  |  |  |  |  |  |

|        |                  |                               |                                       |  |  |  |  |  |  |  |  |

|        |                  |                               |                                       |  |  |  |  |  |  |  |  |