# EN 300 417-3-1 V1.1.3 (1999-05)

European Standard (Telecommunications series)

Transmission and Multiplexing (TM);

Generic requirements of transport functionality of equipment;

Part 3-1: Synchronous Transport Module-N (STM-N)

regenerator and multiplex section layer functions

#### Reference

REN/TM-01015-3-1a (3v0r9ie0.PDF)

#### Keywords

transmission, SDH, interface

#### **ETSI**

#### Postal address

F-06921 Sophia Antipolis Cedex - FRANCE

#### Office address

650 Route des Lucioles - Sophia Antipolis Valbonne - FRANCE Tel.: +33 4 92 94 42 00 Fax: +33 4 93 65 47 16 Siret N° 348 623 562 00017 - NAF 742 C Association à but non lucratif enregistrée à la Sous-Préfecture de Grasse (06) N° 7803/88

#### Internet

secretariat@etsi.fr http://www.etsi.org

#### **Copyright Notification**

No part may be reproduced except as authorized by written permission. The copyright and the foregoing restriction extend to reproduction in all media.

© European Telecommunications Standards Institute 1998. All rights reserved.

## Contents

| Intell         | ectual Property Rights                                                                                                                                                     | 7  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Forev          | word                                                                                                                                                                       | 7  |

| 1              | Scope                                                                                                                                                                      | 9  |

| 2              | References                                                                                                                                                                 | 9  |

| 3              | Definitions, abbreviations and symbols                                                                                                                                     | 10 |

| 3.1            | Definitions                                                                                                                                                                |    |

| 3.2            | Abbreviations                                                                                                                                                              |    |

| 3.3            | Symbols and Diagrammatic Conventions                                                                                                                                       |    |

| 3.4            | Introduction                                                                                                                                                               |    |

| 4              | STM-1 Regenerator Section Layer Functions                                                                                                                                  | 13 |

| 4.1            | STM-1 Regenerator Section Connection functions                                                                                                                             |    |

| 4.2            | STM-1 Regenerator Section Trail Termination functions                                                                                                                      | 14 |

| 4.2.1          | STM-1 Regenerator Section Trail Termination Source RS1_TT_So                                                                                                               | 14 |

| 4.2.2          | STM-1 Regenerator Section Trail Termination Sink RS1_TT_Sk                                                                                                                 | 16 |

| 4.3            | STM-1 Regenerator Section Adaptation functions                                                                                                                             |    |

| 4.3.1          | STM-1 Regenerator Section to Multiplex Section Adaptation Source RS1/MS1_A_So                                                                                              |    |

| 4.3.2          | STM-1 Regenerator Section to Multiplex Section Adaptation Sink RS1/MS1_A_Sk                                                                                                |    |

| 4.3.3          | STM-1 Regenerator Section to DCC Adaptation Source RS1/DCC_A_So                                                                                                            |    |

| 4.3.4          | STM-1 Regenerator Section to DCC Adaptation Sink RS1/DCC_A_Sk                                                                                                              |    |

| 4.3.5          | STM-1 Regenerator Section to P0s Adaptation Source RS1/P0s_A_So/N                                                                                                          |    |

| 4.3.6          | STM-1 Regenerator Section to P0s Adaptation Sink RS1/P0s_A_Sk/N                                                                                                            |    |

| 4.3.7          | STM-1 Regenerator Section toV0x Adaptation Source RS1/V0x_A_So                                                                                                             |    |

| 4.3.8          | STM-1 Regenerator Section to V0x Adaptation Sink RS1/V0x_A_Sk                                                                                                              |    |

| 5              | STM-1 Multiplex Section Layer Functions                                                                                                                                    |    |

| 5.1            | STM-1 Multiplex Section Connection functions                                                                                                                               |    |

| 5.2            | STM-1 Multiplex Section Trail Termination functions                                                                                                                        |    |

| 5.2.1          | STM-1 Multiplex Section Trail Termination Source MS1_TT_So                                                                                                                 |    |

| 5.2.2          | STM-1 Multiplex Section Trail Termination Sink MS1_TT_Sk                                                                                                                   |    |

| 5.3            | STM-1 Multiplex Section Adaptation functions                                                                                                                               |    |

| 5.3.1          | STM-1 Multiplex Section to S4 Layer Adaptation Source MS1/S4_A_So                                                                                                          |    |

| 5.3.2          | STM-1 Multiplex Section to S4 Layer Adaptation Sink MS1/S4_A_Sk                                                                                                            |    |

| 5.3.3          | STM-1 Multiplex Section to DCC Adaptation Source MS1/DCC_A_So                                                                                                              |    |

| 5.3.4<br>5.3.5 | STM-1 Multiplex Section to DCC Adaptation Sink MS1/DCC_A_Sk                                                                                                                |    |

|                | STM-1 Multiplex Section to P0s Adaptation Source MS1/P0s_A_So                                                                                                              |    |

| 5.3.6<br>5.3.7 | STM-1 Multiplex Section to Pos Adaptation Sink MS1/Pos_A_sk                                                                                                                |    |

| 5.3.8          | STM-1 Multiplex Section to Synchronization Distribution Adaptation Source MS1/SD_A_So  STM-1 Multiplex Section to Synchronization Distribution Adaptation Sink MS1/SD_A_Sk |    |

| 5.3.9          | STM-1 Multiplex Section to Synchronization Distribution Adaptation Sink WiS1/3D_A_Sk                                                                                       |    |

| 5.4            | STM-1 Multiplex Section Layer Monitoring Functions                                                                                                                         |    |

| 5.5            | STM-1 Multiplex Section Linear Trail Protection Functions                                                                                                                  |    |

| 5.5.1          | STM-1 Multiplex Section Linear Trail Protection Connection Functions                                                                                                       |    |

| 5.5.1.         | •                                                                                                                                                                          |    |

| 5.5.1.         |                                                                                                                                                                            |    |

| 5.5.2          | STM-1 Multiplex Section Linear Trail Protection Trail Termination Functions                                                                                                |    |

| 5.5.2.         |                                                                                                                                                                            |    |

| 5.5.2.         |                                                                                                                                                                            |    |

| 5.5.3          | STM-1 Multiplex Section Linear Trail Protection Adaptation Functions                                                                                                       |    |

| 5.5.3.         |                                                                                                                                                                            |    |

|                | MS1/MS1P_A_So                                                                                                                                                              | 48 |

| 5.5.3.         | 2 STM-1 Multiplex Section to STM-1 Multiplex Section Protection Layer Adaptation Sink                                                                                      |    |

|                | MS1/MS1P A Sk                                                                                                                                                              | 49 |

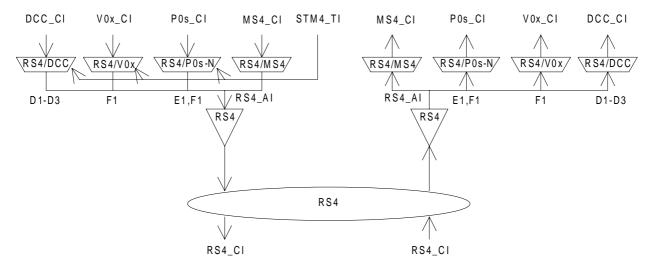

| 6       | STM-4 Regenerator Section Layer Functions                                             |            |  |

|---------|---------------------------------------------------------------------------------------|------------|--|

| 6.1     | STM-4 Regenerator Section Connection functions                                        |            |  |

| 6.2     | STM-4 Regenerator Section Trail Termination functions                                 |            |  |

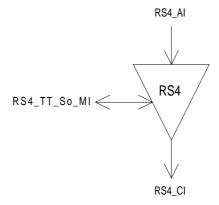

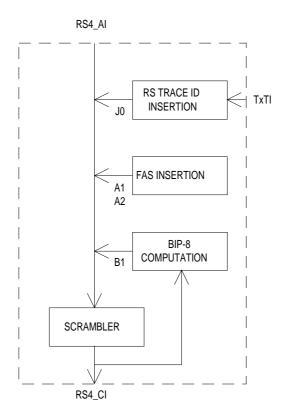

| 6.2.1   | STM-4 Regenerator Section Trail Termination Source RS4_TT_So                          | 51         |  |

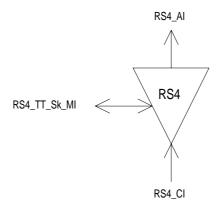

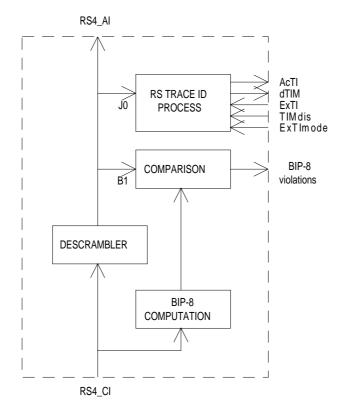

| 6.2.2   | STM-4 Regenerator Section Trail Termination Sink RS4_TT_Sk                            | 54         |  |

| 6.3     | STM-4 Regenerator Section Adaptation functions                                        |            |  |

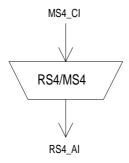

| 6.3.1   | STM-4 Regenerator Section to Multiplex Section Adaptation Source RS4/MS4_A_So         | 56         |  |

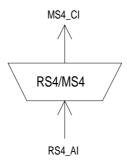

| 6.3.2   | STM-4 Regenerator Section to Multiplex Section Adaptation Sink RS4/MS4_A_Sk           | 57         |  |

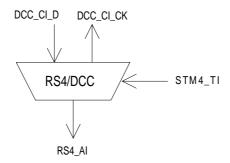

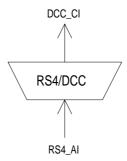

| 6.3.3   | STM-4 Regenerator Section to DCC Adaptation Source RS4/DCC_A_So                       | 58         |  |

| 6.3.4   | STM-4 Regenerator Section to DCC Adaptation Sink RS4/DCC_A_Sk                         | 59         |  |

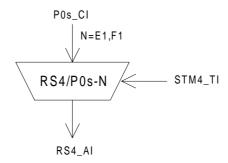

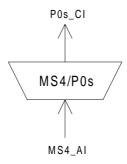

| 6.3.5   | STM-4 Regenerator Section to P0s Adaptation Source RS4/P0s_A_So/N                     | 60         |  |

| 6.3.6   | STM-4 Regenerator Section to P0s Adaptation Sink RS4/P0s_A_Sk/N                       | 61         |  |

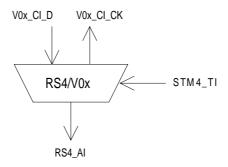

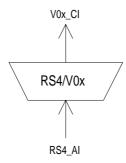

| 6.3.7   | STM-4 Regenerator Section to V0x Adaptation Source RS4/V0x_A_So                       | 62         |  |

| 6.3.8   | STM-4 Regenerator Section to V0x Adaptation Sink RS4/V0x_A_Sk                         | 63         |  |

| 7       | CTM 4 Marking Continue Language                                                       | <i>C</i> 1 |  |

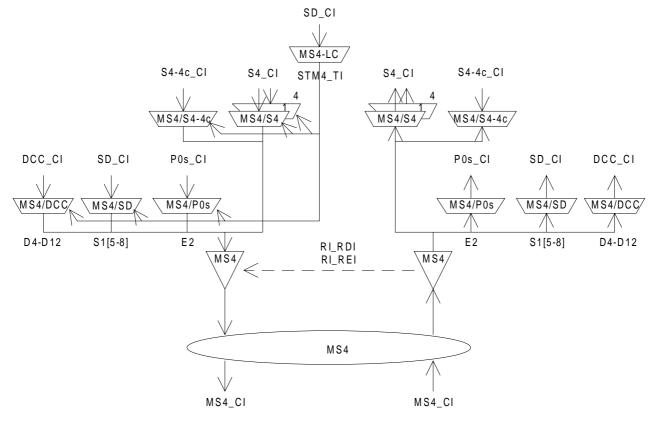

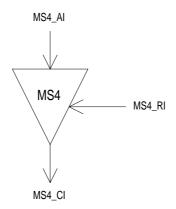

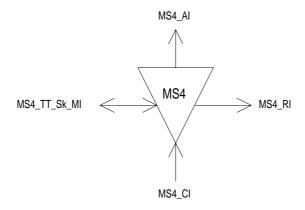

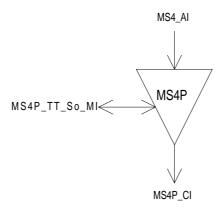

| 7       | STM-4 Multiplex Section Layer Functions                                               |            |  |

| 7.1     | STM-4 Multiplex Section Connection functions                                          |            |  |

| 7.2     | STM-4 Multiplex Section Trail Termination functions                                   |            |  |

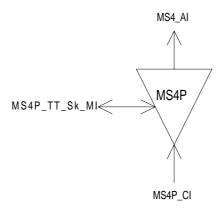

| 7.2.1   | STM-4 Multiplex Section Trail Termination Source MS4_TT_So                            |            |  |

| 7.2.2   | STM-4 Multiplex Section Trail Termination Sink MS4_TT_Sk                              |            |  |

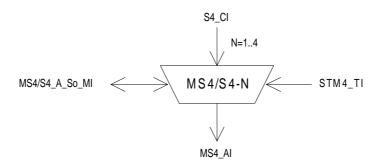

| 7.3     | STM-4 Multiplex Section Adaptation functions                                          |            |  |

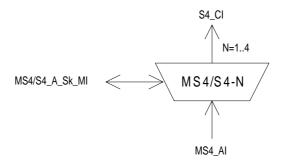

| 7.3.1   | STM-4 Multiplex Section to S4 Layer Adaptation Source MS4/S4_A_So/N                   |            |  |

| 7.3.2   | STM-4 Multiplex Section to S4 Layer Adaptation Sink MS4/S4_A_Sk/N                     |            |  |

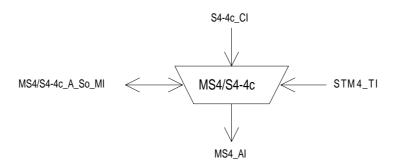

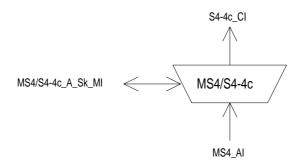

| 7.3.3   | STM-4 Multiplex Section to S4-4c Layer Adaptation Source MS4/S4-4c_A_So               |            |  |

| 7.3.4   | STM-4 Multiplex Section to S4-4c Layer Adaptation Sink MS4/S4-4c_A_Sk                 |            |  |

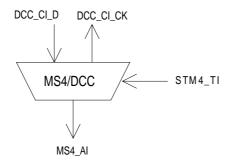

| 7.3.5   | STM-4 Multiplex Section to DCC Adaptation Source MS4/DCC_A_So                         |            |  |

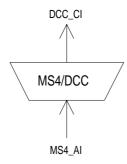

| 7.3.6   | STM-4 Multiplex Section to DCC Adaptation Sink MS4/DCC_A_Sk                           |            |  |

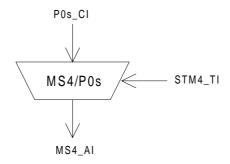

| 7.3.7   | STM-4 Multiplex Section to P0s Adaptation Source MS4/P0s_A_So                         |            |  |

| 7.3.8   | STM-4 Multiplex Section to P0s Adaptation Sink MS4/P0s_A_Sk                           |            |  |

| 7.3.9   | STM-4 Multiplex Section to Synchronization Distribution Adaptation Source MS4/SD_A_So |            |  |

| 7.3.10  | 1 – –                                                                                 |            |  |

| 7.3.11  | 1 - 1                                                                                 |            |  |

| 7.4     | STM-4 Multiplex Section Layer Monitoring Functions                                    |            |  |

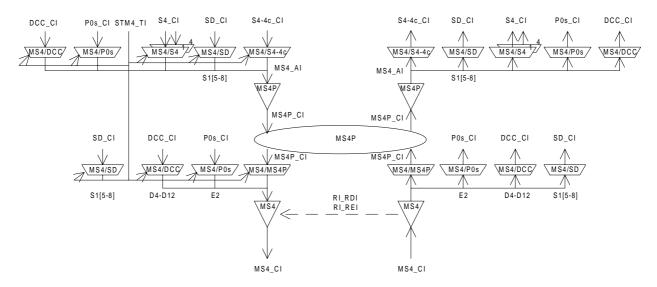

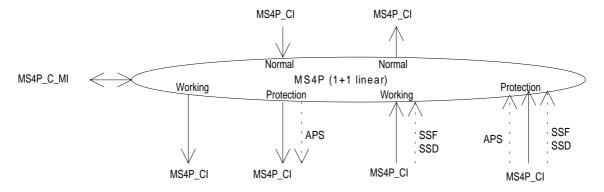

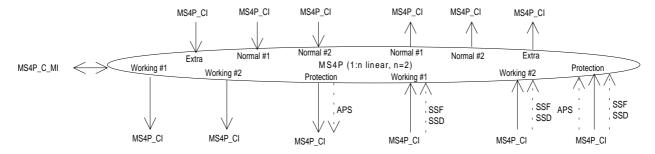

| 7.5     | STM-4 Multiplex Section Linear Trail Protection Functions                             |            |  |

| 7.5.1   | STM-4 Multiplex Section Linear Trail Protection Connection Functions                  |            |  |

| 7.5.1.1 |                                                                                       |            |  |

| 7.5.1.2 | <u> </u>                                                                              |            |  |

| 7.5.2   | STM-4 Multiplex Section Linear Trail Protection Trail Termination Functions           | 91         |  |

| 7.5.2.1 | 1 – –                                                                                 |            |  |

| 7.5.2.2 |                                                                                       |            |  |

| 7.5.3   | STM-4 Multiplex Section Linear Trail Protection Adaptation Functions                  | 93         |  |

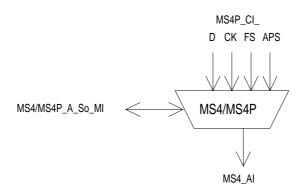

| 7.5.3.1 | STM-4 Multiplex Section to STM-4 Multiplex Section Protection Layer Adaptation Source |            |  |

|         | MS4/MS4P_A_So                                                                         | 93         |  |

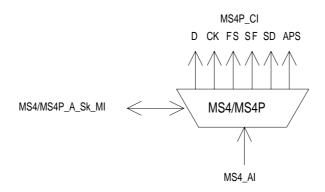

| 7.5.3.2 | STM-4 Multiplex Section to STM-4 Multiplex Section Protection Layer Adaptation Sink   |            |  |

|         | MS4/MS4P_A_Sk                                                                         | 94         |  |

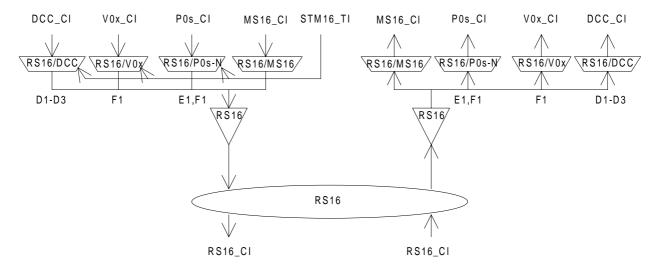

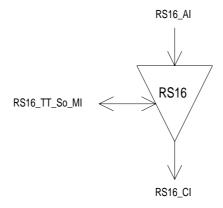

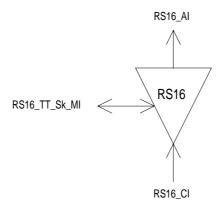

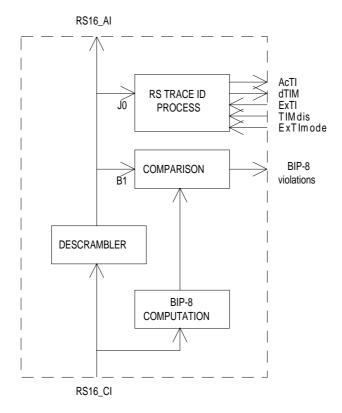

| 8       | STM-16 Regenerator Section Layer Functions                                            | 05         |  |

|         | •                                                                                     |            |  |

| 8.1     | STM-16 Regenerator Section Connection functions.                                      |            |  |

| 8.2     | STM-16 Regenerator Section Trail Termination functions                                | 96         |  |

| 8.2.1   | STM-16 Regenerator Section Trail Termination Source RS16_TT_So                        | 96         |  |

| 8.2.2   | STM-16 Regenerator Section Trail Termination Sink RS16_TT_Sk                          |            |  |

| 8.3     | STM-16 Regenerator Section Adaptation functions                                       |            |  |

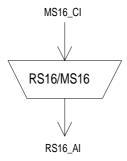

| 8.3.1   | STM-16 Regenerator Section to Multiplex Section Adaptation Source RS16/MS16_A_So      |            |  |

| 8.3.2   | STM-16 Regenerator Section to Multiplex Section Adaptation Sink RS16/MS16_A_Sk        |            |  |

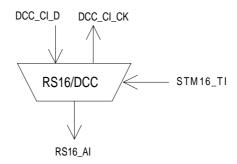

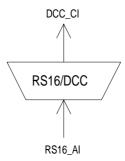

| 8.3.3   | STM-16 Regenerator Section to DCC Adaptation Source RS16/DCC_A_So                     |            |  |

| 8.3.4   | STM-16 Regenerator Section to DCC Adaptation Sink RS16/DCC_A_Sk                       |            |  |

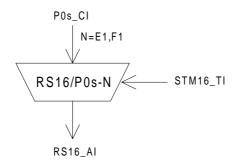

| 8.3.5   |                                                                                       |            |  |

| 8.3.6   |                                                                                       |            |  |

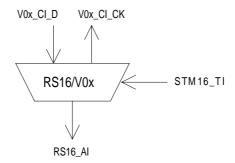

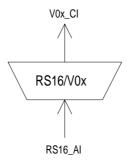

| 8.3.7   | STM-16 Regenerator Section to V0x Adaptation Source RS16/V0x_A_So                     |            |  |

| 8.3.8   | STM-16 Regenerator Section to V0x Adaptation Sink RS16/V0x_A_Sk                       | 108        |  |

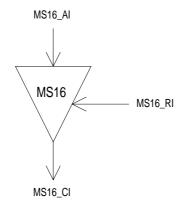

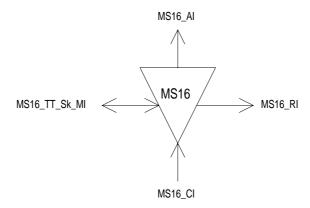

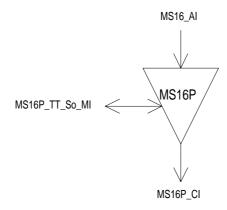

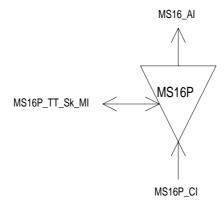

| 9                | STM-16 Multiplex Section Layer Functions                                                    | 109              |

|------------------|---------------------------------------------------------------------------------------------|------------------|

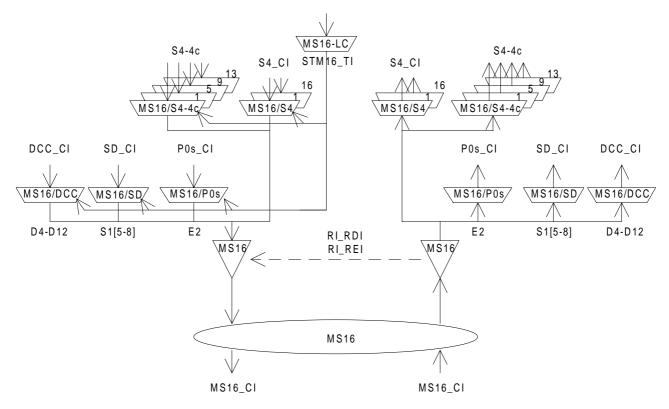

| 9.1              | STM-16 Multiplex Section Connection functions                                               | 114              |

| 9.2              | STM-16 Multiplex Section Trail Termination functions                                        | 114              |

| 9.2.1            | STM-16 Multiplex Section Trail Termination Source MS16_TT_So                                | 114              |

| 9.2.2            | STM-16 Multiplex Section Trail Termination Sink MS16_TT_Sk                                  | 116              |

| 9.3              | STM-16 Multiplex Section Adaptation functions                                               |                  |

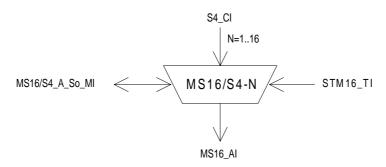

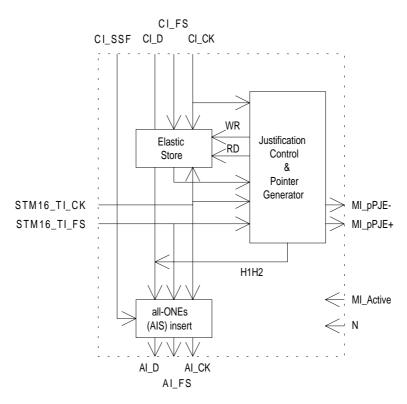

| 9.3.1            | STM-16 Multiplex Section to S4 Layer Adaptation Source MS16/S4_A_So/N                       | 118              |

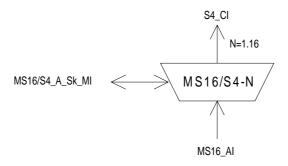

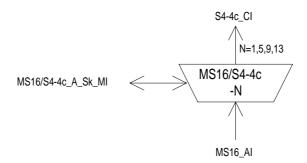

| 9.3.2            | STM-16 Multiplex Section to S4 Layer Adaptation Sink MS16/S4_A_Sk/N                         | 121              |

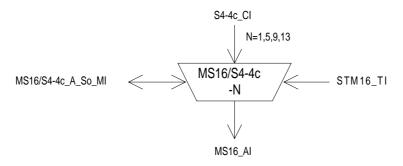

| 9.3.3            | STM-16 Multiplex Section to S4-4c Layer Adaptation Source MS16/S4-4c_A_So/N                 | 123              |

| 9.3.4            | STM-16 Multiplex Section to S4-4c Layer Adaptation Sink MS16/S4-4c_A_Sk/N                   | 126              |

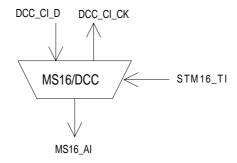

| 9.3.5            | STM-16 Multiplex Section to DCC Adaptation Source MS16/DCC_A_So                             | 128              |

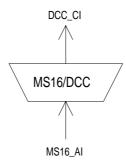

| 9.3.6            | STM-16 Multiplex Section to DCC Adaptation Sink MS16/DCC_A_Sk                               |                  |

| 9.3.7            | STM-16 Multiplex Section to P0s Adaptation Source MS16/P0s_A_So                             |                  |

| 9.3.8            | STM-16 Multiplex Section to P0s Adaptation Sink MS16/P0s_A_Sk                               |                  |

| 9.3.9            | STM-16 Multiplex Section to Synchronization Distribution Adaptation Source MS16/SD_A_So     |                  |

| 9.3.10           | 1                                                                                           |                  |

| 9.3.11           | STM-16 Multiplex Section Layer Clock Adaptation Source MS16-LC_A_So                         |                  |

| 9.4              | STM-16 Multiplex Section Layer Monitoring Functions                                         |                  |

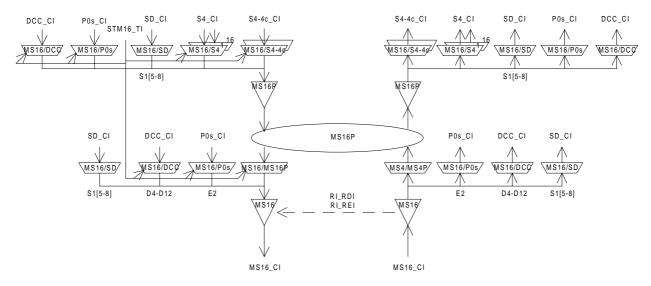

| 9.5              | STM-16 Multiplex Section Linear Trail Protection Functions                                  |                  |

| 9.5.1            | STM-16 Multiplex Section Linear Trail Protection Connection Functions                       |                  |

| 9.5.1.1          | <u> </u>                                                                                    |                  |

| 9.5.1.2          | <u> </u>                                                                                    |                  |

| 9.5.2            | STM-16 Multiplex Section Linear Trail Protection Trail Termination Functions                |                  |

| 9.5.2.1          |                                                                                             |                  |

| 9.5.2.2          |                                                                                             |                  |

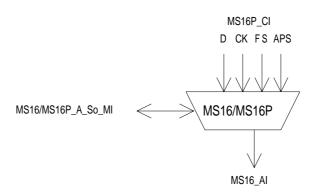

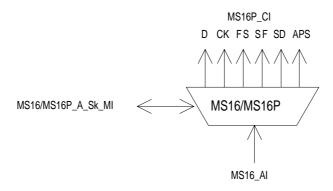

| 9.5.3            | STM-16 Multiplex Section Linear Trail Protection Adaptation Functions                       | 139              |

| 9.5.3.1          |                                                                                             |                  |

|                  | MS16/MS16P_A_So                                                                             | 139              |

| 9.5.3.2          |                                                                                             |                  |

|                  | MS16/MS16P_A_Sk                                                                             |                  |

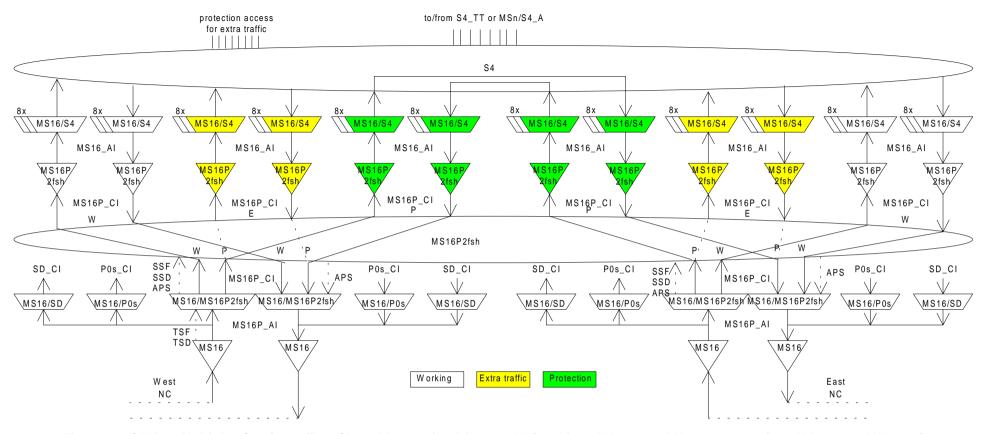

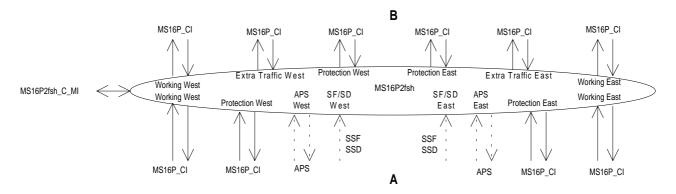

| 9.6              | STM-16 Multiplex Section 2 Fibre Shared Protection Ring Functions                           |                  |

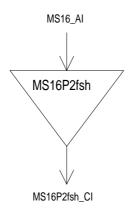

| 9.6.1            | STM-16 Multiplex Section 2 Fibre Shared Protection Ring Connection MS16P2fsh_C              |                  |

| 9.6.2            | STM-16 Multiplex Section 2 Fibre Shared Protection Ring Trail Termination Functions         | 145              |

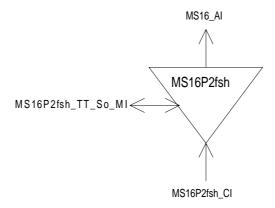

| 9.6.2.1          |                                                                                             |                  |

| 0 < 0 0          | MS16P2fsh_TT_So                                                                             | 145              |

| 9.6.2.2          |                                                                                             | 1.1.             |

| 0.60             | MS16P2fsh_TT_Sk                                                                             |                  |

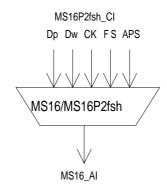

| 9.6.3            | STM-16 Multiplex Section 2 Fibre Shared Protection Ring Adaptation Functions                | 14/              |

| 9.6.3.1          |                                                                                             | 1.47             |

| 0 6 2 2          | Adaptation Source MS16/MS16P2fsh_A_So                                                       | 14/              |

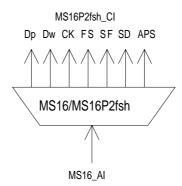

| 9.6.3.2          |                                                                                             | 1.40             |

| 0.7              | Adaptation Sink MS16/MS16P2fsh_A_Sk                                                         |                  |

| 9.7              | STM-16 Multiplex Section 4 Fibre Shared Protection Ring Functions                           | 149              |

| 9.7.1            | STM-16 Multiplex Section 4 Fibre Shared Protection Ring Connection MS16P4fsh_C              |                  |

| 9.7.2            | STM-16 Multiplex Section 4 Fibre Shared Protection Ring Trail Termination Functions         | 149              |

| 9.7.2.1          | MS16P4fsh_TT_So                                                                             | 140              |

| 0722             |                                                                                             | 149              |

| 9.7.2.2          |                                                                                             | 140              |

| 9.7.3            | MS16P4fsh_TT_SkSTM-16 Multiplex Section 4 Fibre Shared Protection Ring Adaptation Functions |                  |

| 9.7.3<br>9.7.3.1 |                                                                                             | 149              |

| 1.1.3.1          | Adaptation Source MS16/MS16P4fsh_A_So                                                       | 1/10             |

| 9.7.3.2          | <u>*</u>                                                                                    | 1 <del>4</del> 7 |

| 1.1.3.2          | Adaptation Sink MS16/MS16P4fsh A Sk                                                         | 149              |

|                  |                                                                                             |                  |

| 10                             | STM-64 Regenerator                | Section layer functions                                        | 149         |

|--------------------------------|-----------------------------------|----------------------------------------------------------------|-------------|

| 11                             | STM-64 Multiplex S                | ection layer functions                                         | 149         |

| Anne                           | ex A (normative):                 | Generic specification of linear protection switching operation | 150         |

| A.1                            | Protection process ov             | verview                                                        | 151         |

| A.2                            | External switch com               | nands definition                                               | 152         |

| A.3                            | Conditions of working             | g and protection trail / connections                           | 153         |

| A.4                            | States within protecti            | on process                                                     | 153         |

| A.5                            | Numbering of working              | ng, protection, normal, extra traffic, null signals            | 154         |

| A.6                            | Priority of request ty            | pes (conditions, external commands, states)                    | 155         |

| A.7<br>A.7.1<br>A.7.2<br>A.7.3 | APS signal fields<br>STM-N MS-APS | 1                                                              | 156         |

| A.8                            | Switch performance:               | switching and holdoff times                                    | 158         |

| A.9                            | Subprocesses                      |                                                                | 158         |

| Anne                           | ex B (informative):               | STM-16 regenerator functional model (example)                  | 166         |

| Anne                           | ex C (informative):               | AU-4-Xc numbering scheme & pointer allocation                  | 167         |

| Anne                           | ex D (informative):               | MS protection examples                                         | <b>17</b> 3 |

| Biblio                         | ography                           |                                                                | 173         |

| Histo                          | <b>r</b> v                        |                                                                | 174         |

## Intellectual Property Rights

IPRs essential or potentially essential to the present document may have been declared to ETSI. The information pertaining to these essential IPRs, if any, is publicly available for **ETSI members and non-members**, and can be found in SR 000 314: "Intellectual Property Rights (IPRs); Essential, or potentially Essential, IPRs notified to ETSI in respect of ETSI standards", which is available **free of charge** from the ETSI Secretariat. Latest updates are available on the ETSI Web server (http://www.etsi.org/ipr).

Pursuant to the ETSI IPR Policy, no investigation, including IPR searches, has been carried out by ETSI. No guarantee can be given as to the existence of other IPRs not referenced in SR 000 314 (or the updates on the ETSI Web server) which are, or may be, or may become, essential to the present document.

#### **Foreword**

This European Standard (Telecommunications series) has been produced by ETSI Technical Committee Transmission and Multiplexing (TM).

The present document is one of a family of documents that has been produced in order to provide inter-vendor and inter-operator compatibility of Synchronous Digital Hierarchy (SDH) equipment.

The present document is part 3-1 of a multi-part EN covering the generic requirements of transport functionality of equipment, as identified below:

- Part 1-1: "Generic processes and performance".

- Part 1-2: "General information about Implementation Conformance Statement (ICS) proforma".

- Part 2-1: "Synchronous Digital Hierarchy (SDH) and Plesiochronous Digital Hierarchy (PDH) physical section layer functions".

- Part 2-2: "Synchronous Digital Hierarchy (SDH) and Plesiochronous Digital Hierarchy (PDH) physical section layer functions; Implementation Conformance Statement (ICS) proforma specification".

- Part 3-1: "Synchronous Transport Module-N (STM-N) regenerator and multiplex section layer functions".

- Part 3-2: "Synchronous Transport Module-N (STM-N) regenerator and multiplex section layer functions; Implementaion Conformance Statement (ICS) proforma specification".

- Part 4-1: "Synchronous Digital Hierarchy (SDH) path layer functions".

- Part 4-2: "Synchronous Digital Hierarchy (SDH) path layer functions; Implementation Conformance Statement (ICS) proforma specification".

- Part 5-1: "Plesiochronous Digital Hierarchy (PDH) path layer functions".

- Part 5-2: "Plesiochronous Digital Hierarchy (PDH) path layer functions; Implementation Conformance Statement (ICS) proforma specification".

- Part 6-1: "Synchronization layer functions".

- Part 6-2: "Synchronization layer functions; Implementation Conformance Statement (ICS) proforma specification".

- Part 7-1: "Auxiliary layer functions".

- Part 7-2: "Auxiliary layer functions; Implementation Conformance Statement (ICS) proforma specification".

- Parts 2 to 7 specify the layers and their atomic functions.

- NOTE 1: The present document does not currently address configuration management.

- NOTE 2: The SDH radio equipment functional blocks are addressed by ETSI WG TM4.

Various of the above parts have previously been published as parts of ETS 300 417.

They have been converted into parts of EN 300 417 without technical changes, but some editorial changes have been necessary (e.g. references). In particular:

- Parts 2-1, 2-2 and 3-2 have been modified to take account of editorial errors present in edition 1.

- Part 1-1 has had its title change of to align with other parts published at a later date.

Also note that in the meantime parts 8-1 and 8-2 together will all parts x-3 (Abstract Test Suites) have been stopped.

This version of the present document has been published because the previous version had incorrect dates in the transposition table.

| National transposition dates                                                           |                  |  |

|----------------------------------------------------------------------------------------|------------------|--|

| Date of latest announcement of this EN (doa):                                          | 31 August 1999   |  |

| Date of latest publication of new National Standard or endorsement of this EN (dop/e): | 29 February 2000 |  |

| Date of withdrawal of any conflicting National Standard (dow):                         | 29 February 2000 |  |

## 1 Scope

The present document specifies a library of basic building blocks and a set of rules by which they are combined in order to describe transport functionality of equipment. The library comprises the functional building blocks needed to completely specify the generic functional structure of the European Transmission Hierarchies. Equipment which is compliant with the present document needs to be describable as an interconnection of a subset of these functional blocks contained within the present document. The interconnections of these blocks need to obey the combination rules given. The generic functionality is described in EN 300 417-1-1 [3].

### 2 References

The following documents contain provisions which, through reference in this text, constitute provisions of the present document.

- References are either specific (identified by date of publication, edition number, version number, etc.) or non-specific.

- For a specific reference, subsequent revisions do not apply.

- For a non-specific reference, the latest version applies.

- A non-specific reference to an ETS shall also be taken to refer to later versions published as an EN with the same number.

- [1] ETS 300 147: "Transmission and Multiplexing (TM); Synchronous Digital Hierarchy (SDH); Multiplexing structure".

- [2] ETS 300 166 (1993): "Transmission and Multiplexing (TM); Physical and electrical characteristics of hierarchical digital interfaces for equipment using the 2 048 kbit/s based plesiochronous or synchronous digital hierarchies".

- [3] EN 300 417-1-1: "Transmission and Multiplexing (TM); Generic requirements of transport functionality of equipment; Part 1-1: Generic processes and performance".

- [4] EN 300 417-4-1: "Transmission and Multiplexing (TM); Generic requirements of transport functionality of equipment; Part 4-1: Synchronous Digital Hierarchy (SDH) path layer functions".

- [5] EN 300 417–6–1: "Transmission and Multiplexing (TM); Generic requirements of transport functionality of equipment; Part 6-1: Synchronization distribution layer functions".

- [6] ETS 300 746: "Transmission and Multiplexing (TM); Synchronous Digital Hierarchy (SDH); Network protection schemes; Automatic Protection Switch (APS) protocols and operation".

- [7] ITU-T Recommendation G.783: "Characteristics of synchronous digital hierarchy (SDH) equipment functional blocks".

## 3 Definitions, abbreviations and symbols

#### 3.1 Definitions

The functional definitions are described in EN 300 417-1-1 [3].

#### 3.2 Abbreviations

For the purposes of the present document, the following abbreviations apply:

A Adaptation function

AcTI Accepted Trace Identifier

ADM Add-Drop Multiplexer

AI Adapted Information

AIS Alarm Indication Signal

AP Access Point

APId Access Point Identifier

APS Automatic Protection Switch

AU Administrative Unit

AUG Administrative Unit Group

AU-n Administrative Unit, level n

BER Bit Error Ratio

BIP Bit Interleaved Parity

BIP-N Bit Interleaved Parity, width N

C Connection function

CI Characteristic Information

CK ClocK

CM Connection Matrix

CP Connection Point

CS Clock Source

D Data

DCC Data Communications Channel

DEC DECrement

DEG DEGraded

DEGTHR DEGraded THReshold EBC Errored Block Count

ECC Embedded Communications Channel ECC(x) Embedded Communications Channel, layer x

EDC Error Detection Code

EDCV Error Detection Code Violation EMF Equipment Management Function

EQ EQuipment

ES Electrical Section

ES Errored Second

ExTI Expected Trace Identifier

F\_B Far-end Block

FAS Frame Alignment Signal FOP Failure Of Protocol FS Frame Start signal HO Higher Order

HOVC Higher Order Virtual Container

HP Higher order Path

ID IDentifier

IF In Frame state

IF In Frame state

INC INCrement

INV INValid

LC Link Connection

LO Lower Order

LOA Loss Of Alignment; generic for LOF, LOM, LOP

LOFLoss Of FrameLOPLoss Of PointerLOSLoss Of Signal

LOVC Lower Order Virtual Container

MC Matrix Connection

MCF Message Communications Function

MDT Mean Down Time

mei maintenance event information MI Management Information

MO Managed Object

MON MONitored

MP Management Point

MS Multiplex Section

MS1 STM-1 Multiplex Se

MS1 STM-1 Multiplex Section

MS16 STM-16 Multiplex Section

MS4 STM-4 Multiplex Section

MSB Most Significant Bit

MSOH Multiplex Section OverHead

MSP Multiplex Section Protection

MSPG Multiplex Section Protection Group

Not Connected NC N B Near-end Block NC **Network Connection NDF** New Data Flag NE Network Element **NMON** Not MONitored NNI Network Node Interface NU National Use (bits, bytes) NUx National Use, bit rate order x

OAM Operation, Administration and Maintenance

OFS Out of Frame Second

OOF Out Of Frame state

OS Optical Section

OSI(x) Open Systems Interconnection, layer x

OW Order Wire Protection

P\_A Protection Adaptation

P\_C Protection Connection

P\_TT Protection Trail Termination

PDH Plesiochronous Digital Hierarchy

PJE Pointer Justification Event

PM Performance Monitoring

Pn Plesiochronous signal, level n

POH Path OverHead

PRC Primary Reference Clock

PS Protection Switching

PSC Protection Switch Count

PTR PoinTeR

QOS Quality Of Service

RDI Remote Defect Indication

REI Remote Error Indication

RI Remote Information

RP Remote Point

RS Regenerator Section

RS1 STM-1 Regenerator Section

RS1 STM-1 Regenerator Section

RS16 STM-16 Regenerator Section

RS4 STM-4 Regenerator Section

RSOH Regenerator Section OverHead

RxTI Received Trace Identifier

S4 VC-4 path layer

SASE Stand-Alone Synchronization Equipment

SD Synchronization Distribution layer, Signal Degrade

SDH Synchronous Digital Hierarchy

SEC SDH Equipment Clock

SF Signal Fail Sk Sink

SNC Sub-Network Connection

SNC/I Inherently monitored Sub-Network Connection protection

SNC/N Non-intrusively monitored Sub-Network Connection protection

SNC/S Sublayer monitored Sub-Network Connection protection

So Source

SOH Section OverHead

SPRING Shared Protection RING

SR Selected Reference

SSD Server Signal Degrade

SSF Server Signal Fail

SSM Synchronization Status Message

SSU Synchronization Supply Unit

STM Synchronous Transport Module

STM-N Synchronous Transport Module, level N

TCP Termination Connection Point

TI Timing Information

TIM Trace Identifier Mismatch

TM Transmission Medium

TMN Telecommunications Management Network

TP Timing Point

TPmode Termination Point mode

TS Time Slot

TSD Trail Signal Degrade TSF Trail Signal Fail

TT Trail Termination function

TTI Trail Trace Identifier

TTs Trail Termination supervisory function

TxTI Transmitted Trace Identifier

UNEQ UNEQuipped

UNI User Network Interface

USR USeR channels

V0 64 kbit/s contradirectional data layer

VC Virtual Container

VC-n Virtual Container, level-n

W Working

## 3.3 Symbols and Diagrammatic Conventions

The symbols and diagrammatic conventions are described in EN 300 417-1-1 [3].

#### 3.4 Introduction

The atomic functions defining the regenerator and multiplex section layers are described below (clause 4 onwards).

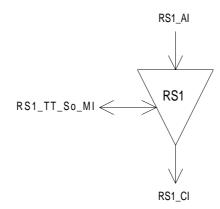

## 4 STM-1 Regenerator Section Layer Functions

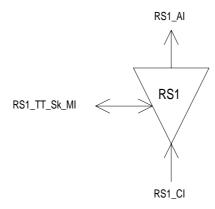

Figure 1: STM-1 Regenerator Section atomic functions

#### **RS1 Layer CP**

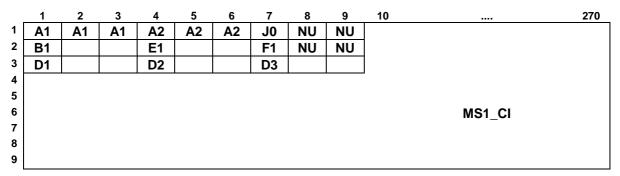

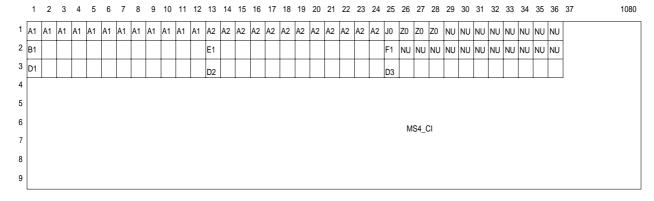

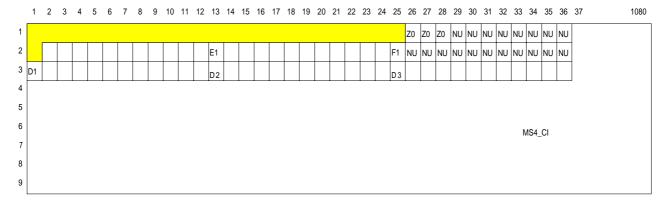

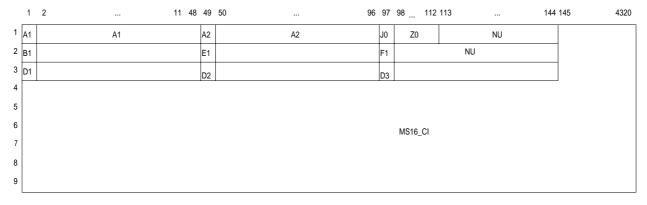

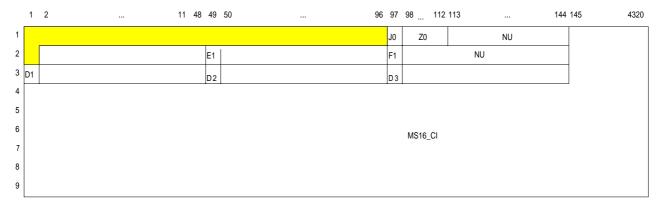

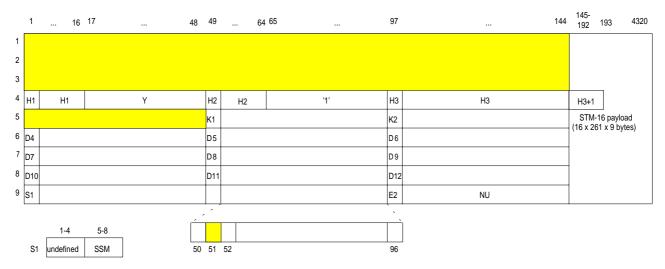

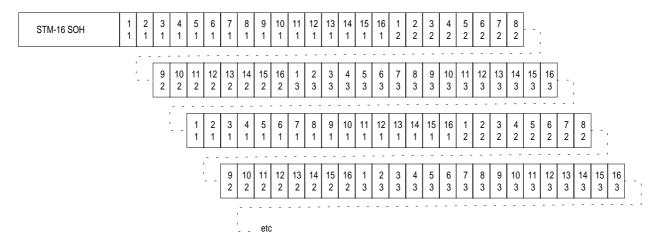

The CI at this point is an octet structured, 125 µs framed data stream with co-directional timing. It is the entire STM-1 signal as defined in ETS 300 147 [1]. Figure 2 depicts only bytes handled in the RS1 layer.

- NOTE 1: The unmarked bytes [2, 6], [3, 6], [3, 8], [3, 9] in rows 2,3 (figure 2) are reserved for future international standardization. Currently, they are undefined.

- NOTE 2: The unmarked bytes [2, 2], [2, 3], [2, 5], [3, 2], [3, 3], [3, 5] in rows 2,3 (figure 2) are reserved for media specific usage (e.g. radio sections). In optical and electrical section applications they are undefined.

- NOTE 3: The bytes for National Use (NU) in rows 1,2 (figure 2) are reserved for operator specific usage. Their processing is not within the province of the present document. If NU bytes [1, 8] and [1, 9] are unused, care should be taken in selecting the binary content of the bytes which are excluded from the scrambling process of the STM-N signal to ensure that long sequences of "1"s or "0"s do not occur.

Figure 2: RS1\_CI\_D signal

#### **RS1 Layer AP**

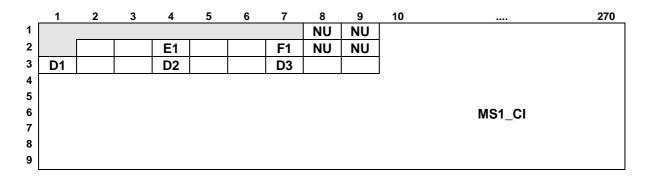

The AI at this point is octet structured and  $125 \,\mu s$  framed with co-directional timing and represents the combination of adapted information from the MS1 layer (2 403 bytes per frame), the management communication DCC layer (3 bytes per frame if supported), the OW layer (1 byte per frame if supported) and the user channel F1 (1 byte per frame if supported). The location of these four components in the frame is defined in ETS 300 147 [1] and depicted in figure 3.

NOTE 4: Bytes E1, F1 and D1-D3 will be undefined when the adaptation functions sourcing these bytes are not present in the network element.

Figure 3: RS1\_AI\_D signal

## 4.1 STM-1 Regenerator Section Connection functions

For further study.

Symbol:

### 4.2 STM-1 Regenerator Section Trail Termination functions

## 4.2.1 STM-1 Regenerator Section Trail Termination Source RS1\_TT\_So

Figure 4: RS1\_TT\_So symbol

#### **Interfaces:**

Table 1: RS1\_TT\_So input and output signals

| Input(s)          | Output(s) |

|-------------------|-----------|

| RS1_AI_D          | RS1_CI_D  |

| RS1_AI_CK         | RS1_CI_CK |

| RS1_AI_FS         |           |

| RS1_TT_So_MI_TxTI |           |

#### **Processes:**

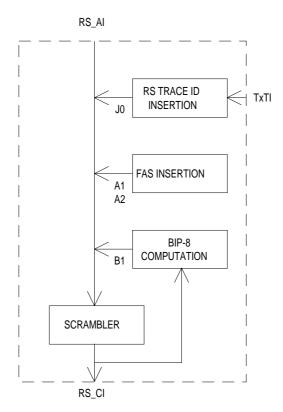

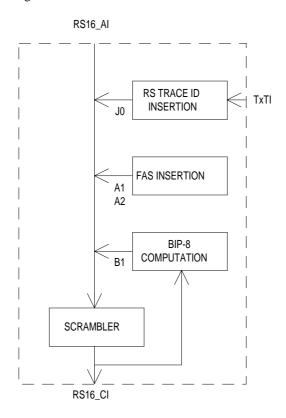

The function builds the STM-1 signal by adding the frame alignment information, bytes A1A2, the STM Section Trace Identifier (STI) byte J0, computing the parity and inserting the B1 byte.

**J0:** In this byte the function shall insert the Transmitted Trail Trace Identifier TxTI. Its format is described in EN 300 417-1-1 [3], subclause 7.1.

**B1:** The function shall calculate a Bit Interleaved Parity 8 (BIP-8) code using even parity. The BIP-8 shall be calculated over all bits of the previous STM-1 frame after scrambling and is placed in byte position B1 of the current STM-1 frame before scrambling (figure 5).

**A1A2:** The function shall insert the STM-1 frame alignment signal A1A1A1A2A2A2 into the regenerator section overhead as defined in ETS 300 147 [1].

Scrambler: This function provides scrambling of the RS1\_CI. The operation of the scrambler shall be functionally identical to that of a frame synchronous scrambler of sequence length 127 operating at the line rate. The generating polynomial shall be  $1 + X^6 + X^7$ . The scrambler shall be reset to "1111 1111" on the most significant bit (MSB) of the byte [1, 10] following the last byte of the STM-1 SOH in the first row. This bit and all subsequent bits to be scrambled shall be modulo 2 added to the output of the  $X^7$  position of the scrambler. The scrambler shall run continuously throughout the remaining STM-1 frame.

Figure 5: Some processes within RS1\_TT\_So

Defects:None.Consequent Actions:None.Defect Correlations:None.Performance Monitoring:None.

### 4.2.2 STM-1 Regenerator Section Trail Termination Sink RS1\_TT\_Sk

#### **Symbol:**

Figure 6: RS1\_TT\_Sk symbol

#### **Interfaces:**

Table 2: RS1\_TT\_Sk input and output signals

| Input(s)              | Output(s)           |

|-----------------------|---------------------|

| RS1_CI_D              | RS1_AI_D            |

| RS1_CI_CK             | RS1_AI_CK           |

| RS1_CI_FS             | RS1_AI_FS           |

| RS1_CI_SSF            | RS1_AI_TSF          |

| RS1_TT_Sk_MI_ExTI     | RS1_TT_Sk_MI_AcTI   |

| RS1_TT_Sk_MI_TPmode   | RS1_TT_Sk_MI_cTIM   |

| RS1_TT_Sk_MI_TIMdis   | RS1_TT_Sk_MI_pN_EBC |

| RS1_TT_Sk_MI_ExTImode | RS1_TT_Sk_MI_pN_DS  |

| RS1_TT_Sk_MI_1second  |                     |

#### **Processes:**

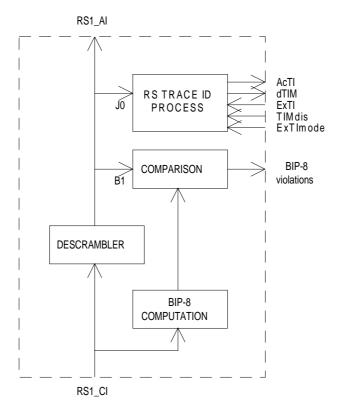

This function monitors the STM-1 signal for RS errors, and recovers the RS trail termination status. It extracts the payload independent overhead bytes (J0, B1) from the RS1 layer Characteristic Information:

*Descrambling:* The function shall descramble the incoming STM-1 signal. The operation of the descrambler shall be functionally identical to that of a scrambler in OS1/RS1\_A\_So.

**B1:** Even bit parity is computed for each bit n of every byte of the preceding scrambled STM-1 frame and compared with bit n of B1 recovered from the current frame (n = 1 to 8 inclusive) (figure 7). A difference between the computed and recovered B1 values is taken as evidence of one or more errors ( $nN_B$ ) in the computation block.

**J0**: The Received Trail Trace Identifier RxTI shall be recovered from the J0 byte and shall be made available as AcTI for network management purposes. The application and acceptance and mismatch detection process shall be performed as specified in EN 300 417-1-1 [3], subclauses 7.1 and 8.2.1.3.

Figure 7: Some processes within RS1\_TT\_Sk

#### **Defects:**

The function shall detect for dTIM defect according the specification in EN 300 417-1-1 [3], subclause 8.2.1.

#### **Consequent Actions:**

aAIS  $\leftarrow$  CI\_SSF or dTIM.

aTSF  $\leftarrow$  CI\_SSF or dTIM.

On declaration of aAIS the function shall output an all-ONEs (AIS) signal within 250  $\mu$ s; on clearing of aAIS the function shall output normal data within 250  $\mu$ s.

NOTE 1: The term "CI\_SSF" has been added to the conditions for aAIS while the descrambler function has been moved from the e.g. OS1/RS1\_A\_Sk to this function. Consequently, an all-ONEs (AIS) pattern inserted in the mentioned adaptation function would be descrambled in this function. A "refreshment" of all-ONEs is required.

NOTE 2: The insertion of AIS - especially due to detection of dTIM - will cause the RS-DCC channel to be "squelched" too, so that control of the NE via this channel is lost. If control is via this channel only, there is a risk of a dead-lock situation if dTIM is caused by a misprovisioning of ExTI.

#### **Defect Correlations:**

cTIM  $\leftarrow$  MON and dTIM.

#### **Performance Monitoring:**

For further study.

## 4.3 STM-1 Regenerator Section Adaptation functions

# 4.3.1 STM-1 Regenerator Section to Multiplex Section Adaptation Source RS1/MS1\_A\_So

**Symbol:**

Figure 8: RS1/MS1\_A\_So symbol

#### **Interfaces:**

Table 3: RS1/MS1\_A\_So input and output signals

| Input(s)   | Output(s) |

|------------|-----------|

| MS1_CI_D   | RS1_AI_D  |

| MS1_CI_CK  | RS1_AI_CK |

| MS1_CI_FS  | RS1_AI_FS |

| MS1_CI_SSF |           |

#### **Processes:**

The function multiplexes the MS1\_CI data (2 403 bytes / frame) into the STM-1 byte locations defined in ETS 300 147 [1] and depicted in figure 2.

NOTE 1: There might be cases in which the network element knows that the timing reference for a particular STM-1 interface can not be maintained within  $\pm 4,6$  ppm. For such cases MS-AIS can be generated. This is network element specific and outside the scope of the present document.

**Defects:** None.

#### **Consequent Actions:**

aAIS  $\leftarrow$  CI\_SSF.

On declaration of aAIS the function shall output all ONEs signal within 250  $\mu$ s; on clearing of aAIS the function shall output normal data within 250  $\mu$ s. The frequency of the all ONEs signal shall be within 155 520 kHz  $\pm$  20 ppm.

NOTE 2: If CI\_SSF is not connected (when RS1/MS1\_A\_So is connected to a MS1\_TT\_So), SSF is assumed to be false.

**Defect Correlations:** None.

# 4.3.2 STM-1 Regenerator Section to Multiplex Section Adaptation Sink RS1/MS1\_A\_Sk

Symbol:

Figure 9: RS1/MS1\_A\_Sk symbol

**Interfaces:**

Table 4: RS1/MS1\_A\_Sk input and output signals

| Input(s)   | Output(s)  |

|------------|------------|

| RS1_AI_D   | MS1_CI_D   |

| RS1_AI_CK  | MS1_CI_CK  |

| RS1_AI_FS  | MS1_CI_FS  |

| RS1_AI_TSF | MS1_CI_SSF |

**Processes:**

The function separates MS1\_CI data from RS1\_AI as depicted in figure 2.

None.

**Defects:** None.

**Consequent Actions:**

aSSF  $\leftarrow$  AI\_TSF.

**Performance Monitoring:**

**Defect Correlations:** None.

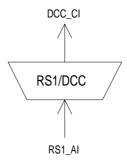

# 4.3.3 STM-1 Regenerator Section to DCC Adaptation Source RS1/DCC\_A\_So

#### Symbol:

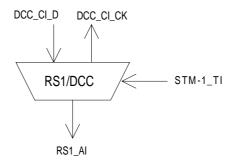

Figure 10: RS1/DCC\_A\_So symbol

#### **Interfaces:**

Table 5: RS1/DCC\_A\_So input and output signals

| Input(s) Output(s) | Input(s)                 |

|--------------------|--------------------------|

|                    | DCC_CI_D<br>STM1_TI_CK   |

|                    | STM1_TI_CK<br>STM1_TI_FS |

#### **Processes:**

The function multiplexes the DCC CI data (192 kbit/s) into the byte locations D1, D2 and D3 as defined in ETS 300 147 [1] and depicted in figure 3.

NOTE: DCC transmission can be "disabled" when the matrix connection in the connected DCC\_C function is removed.

Defects:None.Consequent Actions:None.Defect Correlations:None.

# 4.3.4 STM-1 Regenerator Section to DCC Adaptation Sink RS1/DCC\_A\_Sk

#### Symbol:

Figure 11: RS1/DCC\_A\_Sk symbol

#### **Interfaces:**

Table 6: RS1/DCC\_A\_Sk input and output signals

| Input(s)   | Output(s)  |

|------------|------------|

| RS1_AI_D   | DCC_CI_D   |

| RS1_AI_CK  | DCC_CI_CK  |

| RS1_AI_FS  | DCC_CI_SSF |

| RS1_AI_TSF |            |

#### **Processes:**

The function separates DCC data from RS Overhead as defined in ETS 300 147 [1] and depicted in figure 3.

NOTE: DCC processing can be "disabled" when the matrix connection in the connected DCC\_C function is

removed.

**Defects:** None.

**Consequent Actions:**

aSSF  $\leftarrow$  AI\_TSF.

**Defect Correlations:** None.

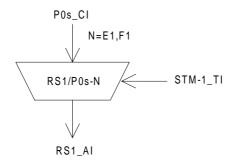

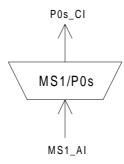

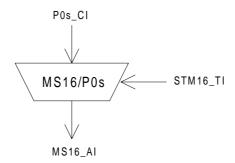

## 4.3.5 STM-1 Regenerator Section to P0s Adaptation Source RS1/P0s A So/N

#### Symbol:

Figure 12: RS1/P0s\_A\_So symbol

#### **Interfaces:**

Table 7: RS1/P0s\_A\_So input and output signals

| Input(s)   | Output(s) |

|------------|-----------|

| P0s_CI_D   | RS1_AI_D  |

| P0s_CI_CK  |           |

| P0s_CI_FS  |           |

| STM1_TI_CK |           |

| STM1_TI_FS |           |

#### **Processes:**

This function provides the multiplexing of a 64 kbit/s orderwire or user channel information stream into the RS1\_AI using slip buffering. It takes P0s\_CI, a 64 kbit/s signal as defined in ETS 300 166 [2], as an octet structured bit-stream with a synchronous bit rate of 64 kbit/s, present at its input and inserts it into the RSOH byte E1 or F1 as defined in ETS 300 147 [1] and depicted in figure 3.

NOTE: Any frequency deviation between the 64 kbit/s signal and the associated STM-1 signal leads to octet slips.

Frequency justification and bitrate adaptation: The function shall provide an elastic store (slip buffer) process. The data signal shall be written into the store under control of the associated input clock. The data shall be read out of the store under control of the STM-1 clock, frame position (STM1\_TI), and justification decisions.

Each justification decision results in a corresponding negative / positive justification action. Upon a positive justification (slip) action, the reading of one 64 kbit/s octet (8 bits) shall be cancelled once. Upon a negative justification (slip) action, the same 64 kbit/s octet (8 bits) shall be read out a second time.

The elastic store (slip buffer) shall accommodate at least 18 µs of wander without introducing errors.

64 kbit/s timeslot: The adaptation source function has access to a specific 64 kbit/s channel of the RS access point. The specific 64 kbit/s channel is defined by the parameter N (N = E1, F1).

Defects: None.

Consequent Actions: None.

Defect Correlations: None.

Performance Monitoring: None.

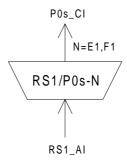

## 4.3.6 STM-1 Regenerator Section to P0s Adaptation Sink RS1/P0s\_A\_Sk/N

#### Symbol:

Figure 13: RS1/P0s\_A\_Sk symbol

#### **Interfaces:**

Table 8: RS1/P0s\_A\_Sk input and output signals

| Input(s)   | Output(s)  |

|------------|------------|

| RS1_AI_D   | P0s_CI_D   |

| RS1_AI_CK  | P0s_CI_CK  |

| RS1_AI_FS  | P0s_CI_FS  |

| RS1_AI_TSF | P0s_CI_SSF |

#### **Processes:**

The function separates P0s data from RS Overhead byte E1 or F1 as defined in ETS 300 147 [1] and depicted in figure 3.

Data latching and smoothing process: The function shall provide a data latching and smoothing function. Each 8-bit octet received shall be written and latched into a data store under the control of the STM-1 signal clock. The eight data bits shall then be read out of the store using a nominal 64 kHz clock which may be derived directly from the incoming STM-1 signal clock (e.g. 155 520 kHz divided by a factor of 2 430).

64 kbit/s timeslot: The adaptation sink function has access to a specific 64 kbit/s of the RS access point. The specific 64 kbit/s is defined by the parameter N (N = E1, F1).

**Defects:** None.

#### **Consequent Actions:**

aSSF  $\leftarrow$  AI\_TSF.

aAIS  $\leftarrow$  AI\_TSF.

On declaration of aAIS the function shall output an all-ONEs (AIS) signal - complying to the frequency limits for this signal (a bit rate in range 64 kbit/s  $\pm$  100 ppm) - within 1 ms; on clearing of aAIS the function shall output normal data within 1 ms.

**Defect Correlations:** None.

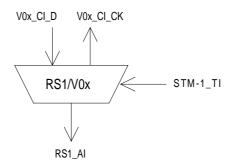

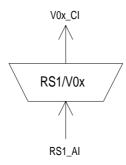

# 4.3.7 STM-1 Regenerator Section toV0x Adaptation Source RS1/V0x\_A\_So

Symbol:

Figure 14: RS1/V0x\_A\_So symbol

**Interfaces:**

Table 9: RS1/V0x\_A\_So input and output signals

| Input(s)   | Output(s) |

|------------|-----------|

| V0x_CI_D   | RS1_AI_D  |

| STM1_TI_CK | V0x_CI_CK |

| STM1_TI_FS |           |

**Processes:** None.

This function shall multiplex the  $V0x_CI$  data (64 kbit/s) into the byte location F1 as defined in ETS 300 147 [1] and depicted in figure 3.

**Defects:** None.

**Consequent Actions:** None.

**Defect Correlations:** None.

## 4.3.8 STM-1 Regenerator Section to V0x Adaptation Sink RS1/V0x\_A\_Sk

#### Symbol:

Figure 15: RS1/V0x\_A\_Sk symbol

#### **Interfaces:**

Table 10: RS1/V0x\_A\_Sk input and output signals

| Input(s)   | Output(s)  |

|------------|------------|

| RS1_AI_D   | V0x_CI_D   |

| RS1_AI_CK  | V0x_CI_CK  |

| RS1_AI_FS  | V0x_CI_SSF |

| RS1_AI_TSF |            |

#### **Processes:**

This function separates user channel data from RS Overhead (byte F1) as defined in ETS 300 147 [1] and depicted in figure 3.

**Defects:** None.

**Consequent Actions:**

aSSF  $\leftarrow$  AI\_TSF.

aAIS  $\leftarrow$  AI\_TSF.

On declaration of aAIS the function shall output an all-ONEs (AIS) signal within 1 ms; on clearing of aAIS the function shall output normal data within 1 ms.

**Defect Correlations:** None.

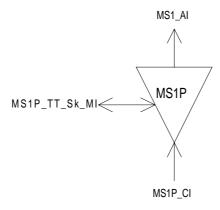

## 5 STM-1 Multiplex Section Layer Functions

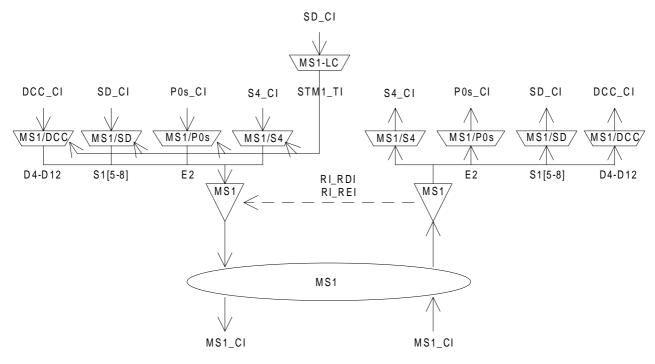

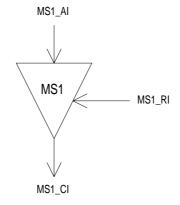

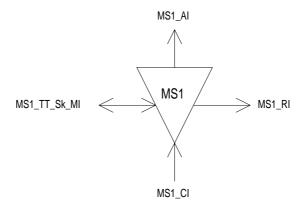

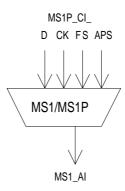

Figure 16: STM-1 Multiplex Section atomic functions

#### **MS1 Layer CP**

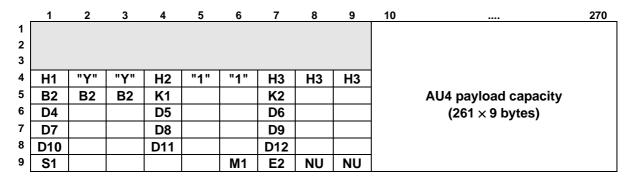

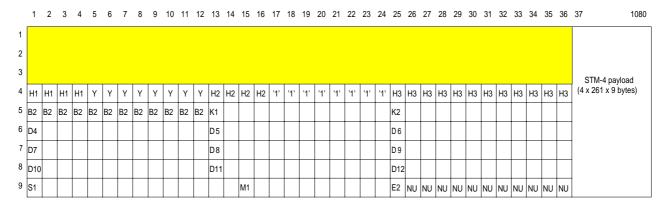

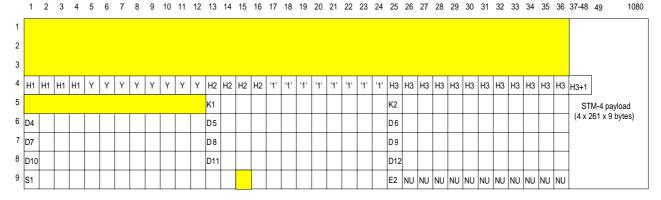

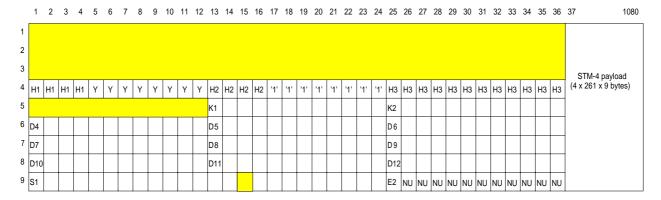

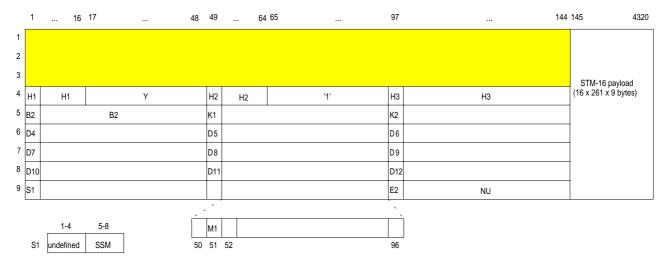

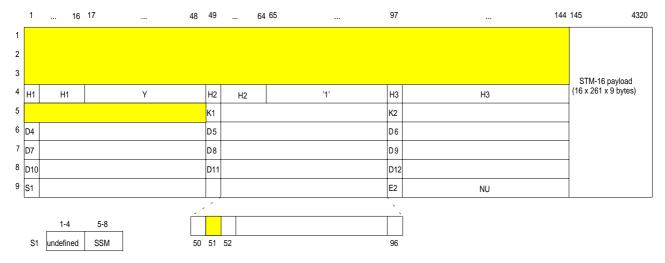

The CI at this point is octet structured and  $125 \,\mu s$  framed with co-directional timing. Its format is characterized as the MS1\_AI with an additional MS Trail Termination overhead in the three B2 bytes, byte M1, and bits 6-8 of the K2 byte in the frame locations defined in ETS 300 147 [1] and depicted in figure 17.

- NOTE 1: The unmarked bytes in rows 5, 6, 7, 8 and 9 (see figure 17) are reserved for future international standardization. Currently, they are undefined.

- NOTE 2: The bytes for National Use (NU) in row 9 (see figure 17) are reserved for operator specific usage. Their processing is not within the province of the present document.

Figure 17: MS1\_CI\_D

#### **MS1 Layer AP**

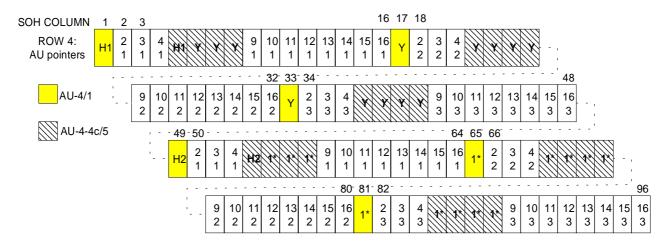

The AI at this point is octet structured and  $125~\mu s$  framed with co-directional timing. It represents the combination of information adapted from the VC-4 layer (150 336 kbit/s), the management communications DCC layer (576 kbit/s), the OW layer (64 kbit/s if supported), the AU-4 pointer (3 bytes per frame), the APS signalling channel (13 or 16 bits per frame if supported, see note 3), and the Synchronization Status Message (SSM) channel (4 bits per frame if supported). The location of these five components in the frame is defined in ETS 300 147 [1] and depicted in figure 18.

NOTE 3: 13 bits APS channel for the case of linear MS protection. 16 bits APS channel for the case of MS SPRING protection

NOTE 4: Bytes E2 and D4-D12 will be undefined when the adaptation functions sourcing these bytes are not present in the network element.

|   | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8  | 9  | 10   | <b></b>              | 270 |

|---|-----|-----|-----|-----|-----|-----|-----|----|----|------|----------------------|-----|

| 1 |     |     |     |     |     |     |     |    |    |      |                      |     |

| 2 |     |     |     |     |     |     |     |    |    |      |                      |     |

| 3 |     |     |     |     |     |     |     |    |    |      |                      |     |

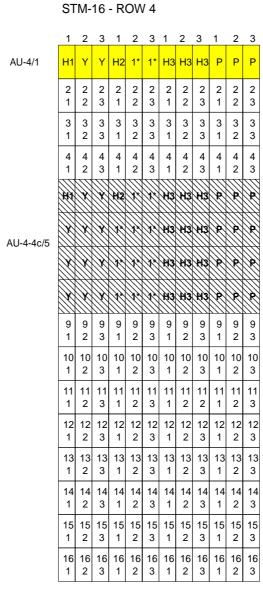

| 4 | H1  | "Y" | "Y" | H2  | "1" | "1" | Н3  | Н3 | Н3 | H3+1 | H3+1 H3+1            |     |

| 5 |     |     |     | K1  |     |     | K2  |    |    |      | AU4 payload capacity |     |

| 6 | D4  |     |     | D5  |     |     | D6  |    |    |      | (261 × 9 bytes)      |     |

| 7 | D7  |     |     | D8  |     |     | D9  |    |    |      |                      |     |

| 8 | D10 |     |     | D11 |     |     | D12 |    |    |      |                      |     |

| 9 | S1  |     |     |     |     |     | E2  | NU | NU |      |                      |     |

Figure 18: MS1\_AI\_D

NOTE 5: The allocation of definitions and associated processing of unused MS OH bytes might change due to their future application.

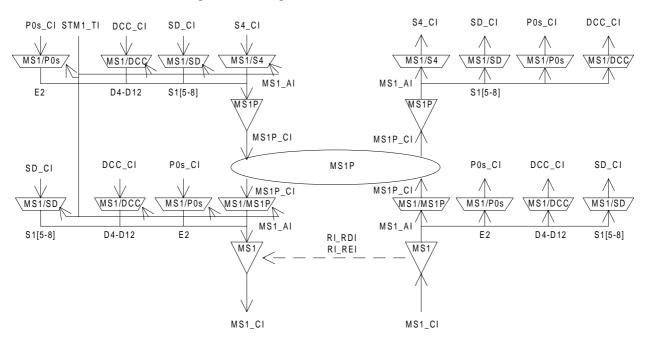

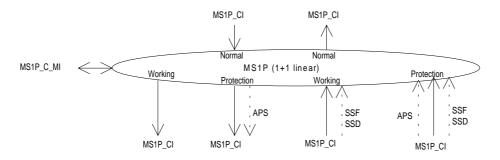

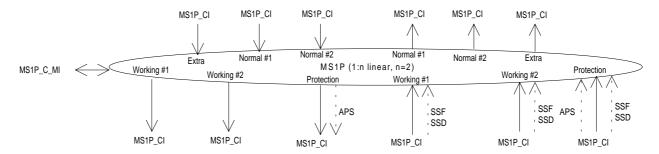

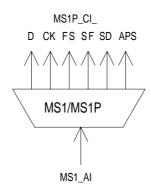

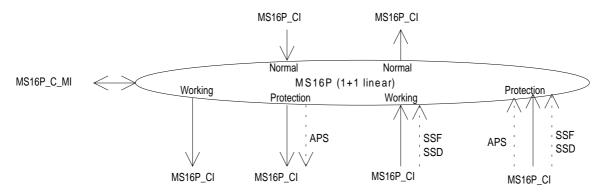

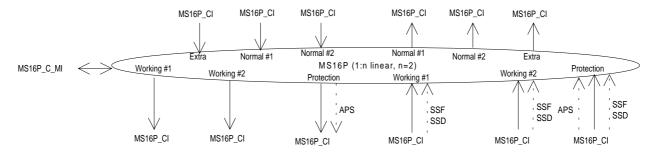

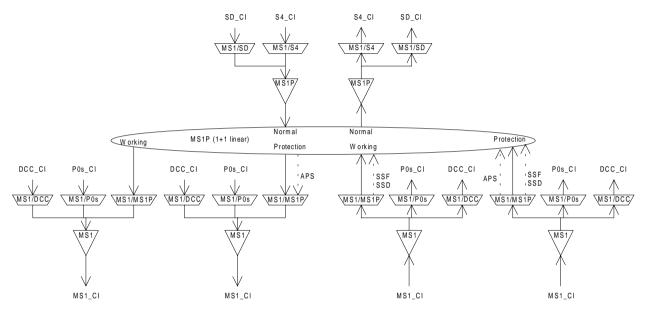

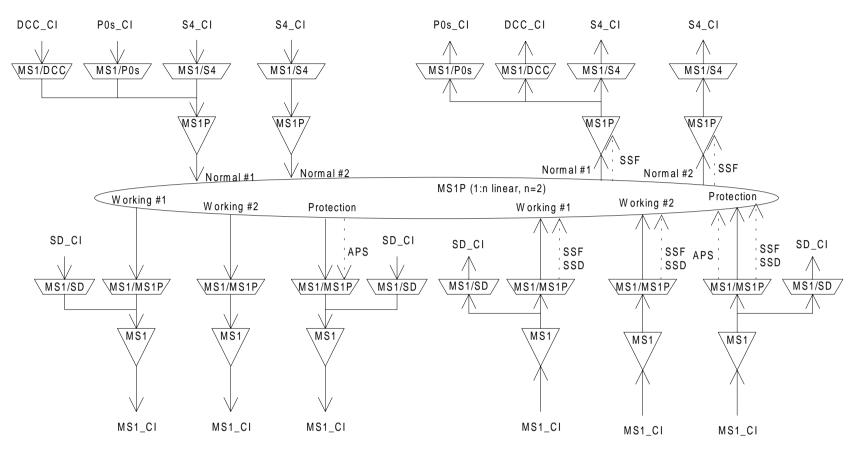

Figure 19 shows the MS trail protection specific sublayer atomic functions (MS1/MS1P\_A, MS1P\_C, MS1P\_TT) within the MS1 layer. Note that the DCC (D4-D12), OW (E2), and SSM (S1[5-8]) signals can be accessible before (unprotected) and after (protected) the MS1P\_C function. The choice is outside the scope of the present document.

NOTE 6: Equipment may provide MS protection and bi-directional services such as DCC and OW in the MS layer. Where a link uses this provision both ends of the link shall be configured to operate these services in the same mode (i.e. either protected or unprotected).

Figure 19: STM-1 Multiplex Section Linear Trail Protection Functions

#### **MS1P Sublayer CP**

The CI at this point is octet structured and 125  $\mu$ s framed with co-directional timing. Its format is equivalent to the MS1\_AI and depicted in figure 20.

NOTE 7: Bytes S1, E2 and D4-D12 will be undefined when the adaptation functions sourcing these bytes are not present in the network element or are unprotected (see above).

|   | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8  | 9  | 10 |                      | 270 |

|---|-----|-----|-----|-----|-----|-----|-----|----|----|----|----------------------|-----|

| 1 |     |     |     |     |     |     |     |    |    |    |                      |     |

| 2 |     |     |     |     |     |     |     |    |    |    |                      |     |

| 3 |     |     |     |     |     |     |     |    |    |    |                      |     |

| 4 | H1  | "Y" | "Y" | H2  | "1" | "1" | Н3  | Н3 | Н3 |    |                      |     |

| 5 |     |     |     | K1  |     |     | K2* |    |    |    | AU4 payload capacity |     |

| 6 | D4  |     |     | D5  |     |     | D6  |    |    |    | (261 × 9 bytes)      |     |

| 7 | D7  |     |     | D8  |     |     | D9  |    |    |    |                      |     |

| 8 | D10 |     |     | D11 |     |     | D12 |    |    |    |                      |     |

| 9 | S1  |     |     |     |     |     | E2  | NU | NU |    |                      |     |

NOTE 8: K2\* represents bits 1 to 5 of K2.

Figure 20: MS1P\_CI\_D

## 5.1 STM-1 Multiplex Section Connection functions

For further study.

## 5.2 STM-1 Multiplex Section Trail Termination functions

# 5.2.1 STM-1 Multiplex Section Trail Termination Source MS1\_TT\_So Symbol:

Figure 21: MS1\_TT\_So symbol

#### **Interfaces:**

Table 11: MS1\_TT\_So input and output signals

| Input(s)   | Output(s) |

|------------|-----------|

| MS1_AI_D   | MS1_CI_D  |

| MS1_AI_CK  | MS1_CI_CK |

| MS1_AI_FS  | MS1_CI_FS |

| MS1_RI_REI |           |

| MS1_RI_RDI |           |

#### Processes:

This function adds error monitoring capabilities and remote maintenance information signals to the MS1\_AI.

**M1:** The function shall insert the value of MS1\_RI\_REI into the REI (Remote Error Indication) - to convey the count of interleaved bit blocks that have been detected in error by the BIP-24 process in the companion MS1\_TT\_Sk - in the range of "0000 0000" (0) to "0001 1000" (24).

**K2[6-8]:** These bits represents the defect status of the associated MS1\_TT\_Sk. The RDI indication shall be set to "110" on activation of MS1\_RI\_RDI within 250 μs, determined by the associated MS1\_TT\_Sk function, and set to "000" within 250 μs on the clearing of MS1\_RI\_RDI.

**B2:** The function shall calculate a Bit Interleaved Parity 24 (BIP-24) code using even parity. The BIP-24 shall be calculated over all bits, except those in the RSOH bytes, of the previous STM-1 frame and placed in three B2 bytes of the current STM-1 frame.

NOTE: The BIP-24 procedure is described in ETS 300 147 [1].

**Defects:** None.

**Consequent Actions:** None.

**Defect Correlations:** None.

**Performance Monitoring:** None.

## 5.2.2 STM-1 Multiplex Section Trail Termination Sink MS1\_TT\_Sk

#### **Symbol:**

Figure 22: MS1\_TT\_Sk symbol

#### **Interfaces:**

Table 12: MS1\_TT\_Sk input and output signals

| Input(s)                  | Output(s)           |

|---------------------------|---------------------|

| MS1_CI_D                  | MS1_AI_D            |

| MS1_CI_CK                 | MS1_AI_CK           |

| MS1_CI_FS                 | MS1_AI_FS           |

| MS1_CI_SSF                | MS1_AI_TSF          |

| MS1_TT_Sk_MI_DEGTHR       | MS1_AI_TSD          |

| MS1_TT_Sk_MI_DEGM         | MS1_TT_Sk_MI_cAIS   |

| MS1_TT_Sk_MI_1second      | MS1_TT_Sk_MI_cDEG   |

| MS1_TT_Sk_MI_TPmode       | MS1_TT_Sk_MI_cRDI   |

| MS1_TT_Sk_MI_SSF_Reported | MS1_TT_Sk_MI_cSSF   |

| MS1_TT_Sk_MI_AIS_Reported | MS1_TT_Sk_MI_pN_EBC |

| MS1_TT_Sk_MI_RDI_Reported | MS1_TT_Sk_MI_pF_EBC |

| ·                         | MS1_TT_Sk_MI_pN_DS  |

|                           | MS1_TT_Sk_MI_pF_DS  |

|                           | MS1_RI_REI          |

|                           | MS1_RI_RDI          |

#### **Processes:**

This function monitors error performance of associated MS1 including the far end receiver.

**B2:** The BIP-24 shall be calculated over all bits, except of those in the RSOH bytes, of the previous STM-1 frame and compared with the three error monitoring bytes B2 recovered from the MSOH of the current STM-1 frame. A difference between the computed and recovered B2 values is taken as evidence of one or more errors (nN\_B) in the computation block.

M1: The REI information carried in these bits shall be extracted to enable single ended maintenance of a bi-directional trail (section). The REI (nF\_B) is used to monitor the error performance of the other direction of transmission. The application process is described in EN 300 417-1-1 [3], subclause 7.4.2 (REI).

The function shall interpret the value of the byte (for interworking with old equipment generating a 7 bit code) as shown in table 13.

Table 13: STM-1 M1 interpretation

| M1[2-8] code, bits<br>234 5678 | code interpretation [#BIP violations], (nF_B) |

|--------------------------------|-----------------------------------------------|

| 000 0000                       | 0                                             |

| 000 0001                       | 1                                             |

| 000 0010                       | 2                                             |

| 000 0011                       | 3                                             |

| :                              | :                                             |

| 001 1000                       | 24                                            |

| 001 1001                       | 0                                             |

| 001 1010                       | 0                                             |

| :                              | i i                                           |

| 111 1111                       | 0                                             |

| NOTE: Bit 1 of byte M          | 1 is ignored.                                 |

NOTE: In case of interworking with old equipment not supporting MS-REI, the information extracted from M1 is not relevant.

**K2**[6-8] - **RDI:** The RDI information carried in these bits shall be extracted to enable single ended maintenance of a bi-directional trail (section). The RDI provides information as to the status of the remote receiver. A "110" indicates a Remote Defect Indication state, while other patterns indicate the normal state. The application process is described in EN 300 417-1-1 [3], subclauses 7.4.11 and 8.2.

**K2[6-8] - AIS:** The MS-AIS information carried in these bits shall be extracted.

#### **Defects:**

The function shall detect for dDEG and dRDI defects according the specification in EN 300 417-1-1 [3], subclause 8.2.1.

dAIS: If at least x consecutive frames contain the "111" pattern in bits 6, 7 and 8 of the K2 byte a dAIS defect shall be detected. dAIS shall be cleared if in at least x consecutive frames any pattern other then the "111" is detected in bits 6, 7 and 8 of byte K2. The x is in range 3 to 5.

#### **Consequent Actions:**

On declaration of aAIS the function shall output an all-ONEs signal within 250  $\mu s;$  on clearing of aAIS the function shall output normal data within 250  $\mu s.$

#### **Defect Correlations:**

```

cAIS ← MON and dAIS and (not CI_SSF) and AIS_Reported.

cDEG ← MON and dDEG.

cRDI ← MON and dRDI and RDI_Reported.

cSSF ← MON and dAIS and SSF_Reported.

```

#### **Performance monitoring:**

The performance monitoring process shall be performed as specified in EN 300 417-1-1 [3], subclause 8.2.4 through 8.2.7.

```

\begin{array}{lll} pN\_DS & \leftarrow & aTSF \ or \ dEQ. \\ \\ pF\_DS & \leftarrow & dRDI. \\ \\ pN\_EBC & \leftarrow & \Sigma \ nN\_B. \\ \\ pF\_EBC & \leftarrow & \Sigma \ nF\_B. \end{array}

```

## 5.3 STM-1 Multiplex Section Adaptation functions

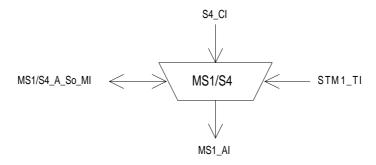

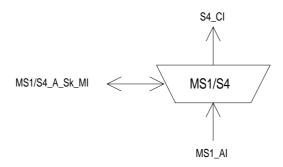

## 5.3.1 STM-1 Multiplex Section to S4 Layer Adaptation Source MS1/S4\_A\_So

Symbol:

Figure 23: MS1/S4\_A\_So symbol

#### **Interfaces:**

Table 14: MS1/S4\_A\_So input and output signals

| Input(s)   | Output(s)            |

|------------|----------------------|

| S4_CI_D    | MS1_AI_D             |

| S4_CI_CK   | MS1_AI_CK            |

| S4_CI_FS   | MS1_AI_FS            |

| S4_CI_SSF  |                      |

| STM1_TI_CK | MS1/S4_A_So_MI_pPJE+ |

| STM1_TI_FS | MS1/S4_A_So_MI_pPJE- |

#### **Processes:**

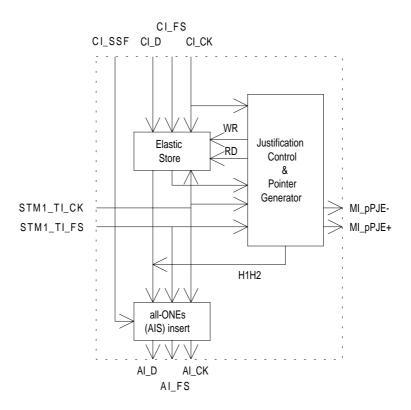

This function provides frequency justification and bitrate adaptation for a VC-4 signal, represented by a nominally  $(261 \times 9 \times 64) = 150 \times 336 \text{ kbit/s}$  information stream and the related frame phase with a frequency accuracy within  $\pm 4,6$  ppm, to be multiplexed into a STM-1 signal.

NOTE 1: Degraded performance may be observed when interworking with SONET equipment having a ± 20 ppm network element clock source.

The frame phase of the VC-4 is coded in the related AU-4 pointer. Frequency justification, if required, is performed by pointer adjustments. The accuracy of this coding process is specified below. See EN 300 417-4-1 [4], annex A.

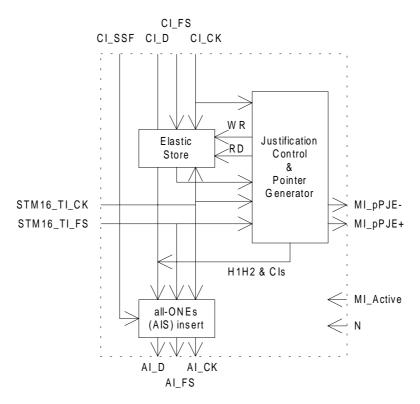

Frequency justification and bitrate adaptation: The function shall provide for an elastic store (buffer) process. The data and frame start signals shall be written into the buffer under control of the associated input clock. The data and frame start signals shall be read out of the buffer under control of the STM-1 clock, frame position, and justification decision.

The justification decisions determine the phase error introduced by the MS1/S4\_A\_So function. The amount of this phase error can be measured at the physical interfaces by monitoring the AU-4 pointer actions. An example is given in EN 300 417-4-1 [4], clause A.2.

Each justification decision results in a corresponding negative / positive justification action. Upon a positive justification action, the reading of 24 data bits shall be cancelled once and no data written at the three positions H3+1. Upon a negative justification action, an extra 24 data bits shall be read out once into the three positions H3.

NOTE 2: A requirement for maximum introduced phase error cannot be defined until a reference path is defined from which the requirements for network elements can be deduced. Such a requirement would also limit excessive phase error caused by pointer processors under fixed frequency offset conditions.

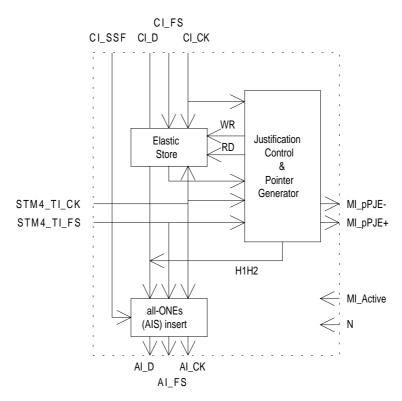

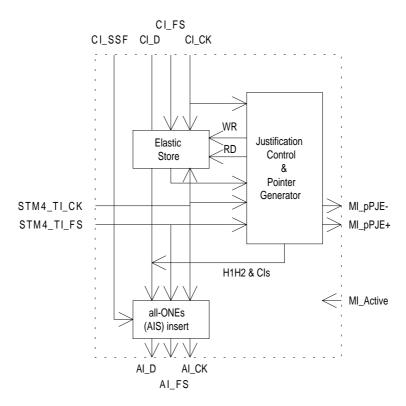

Figure 24: Main processes within MS1/S4\_A\_So

Buffer size: For further study.

Behaviour at recovery from defect condition: The incoming frequency (S4\_CI\_CK) of a passing through VC-4 may exceed its limits during a STM1dLOS condition. As a consequence, the buffer (elastic store) fill is not reliable any more. Due to all-ONEs (AIS) insertion after the pointer generator this reliability is not important for the operation of the network element. However, it shall be prevented to generate excessive pointer adjustments when recovering from the defect condition.

NOTE 3: The definition of excessive pointer adjustments is for further study.

The AU-4 pointer is carried in 2 bytes of payload specific OH (H1, H2) in each STM-1 frame. The AU-4 pointer is aligned in the STM-1 payload in fixed position relative to the STM-1 frame. The AU-4 pointer points to the begin of the VC-4 frame within the STM-1. The format of the AU-4 pointer and its location in the frame are defined in ETS 300 147 [1].

**H1H2 -** *Pointer generation:* The function shall generate the AU-4 pointer as is described in EN 300 417-1-1 [3], annex A: Pointer Generation. It shall insert the pointer in the appropriate H1, H2 positions with the SS field set to 10 to indicate AU-4.

YY1\*1\* - Fixed stuff insertion: The function shall insert fixed stuff codes Y = 1001ss11 in bytes [4, 2], [4, 3] and code "1" = 111111111 in bytes [4, 5], [4, 6]. Bits ss are undefined.

Defects: None.

#### **Consequent Actions:**

aAIS

$$\leftarrow$$

CI\_SSF.

On declaration of aAIS the function shall output an all-ONEs signal within 250  $\mu$ s; on clearing of aAIS the function shall output normal data within 250  $\mu$ s.

NOTE 4: If CI\_SSF is not connected (when MS1/S4\_A\_So is connected to a S4\_TT\_So), CI\_SSF is assumed to be false.

**Defect Correlations:**

None.

#### **Performance Monitoring:**

Every second the number of generated pointer increments within that second shall be counted as the pPJE+. Every second the number of generated pointer decrements within that second shall be counted as the pPJE-.

NOTE 5: This is applicable for a passing through VC-4 only. A locally generated VC-4 may have a fixed frame phase; pointer justifications will not occur.

# 5.3.2 STM-1 Multiplex Section to S4 Layer Adaptation Sink MS1/S4\_A\_Sk

#### Symbol:

Figure 25: MS1/S4\_A\_Sk symbol

#### **Interfaces:**

Table 15: MS1/S4\_A\_Sk input and output signals

| Input(s)                    | Output(s)           |

|-----------------------------|---------------------|

| MS1_AI_D                    | S4_CI_D             |

| MS1_AI_CK                   | S4_CI_CK            |

| MS1_AI_FS                   | S4_CI_FS            |

| MS1_AI_TSF                  | S4_CI_SSF           |

| MS1/S4_A_Sk_MI_AIS_Reported | MS1/S4_A_Sk_MI_cAIS |

| ·                           | MS1/S4_A_Sk_MI_cLOP |

#### **Processes:**

This function recovers the VC-4 data with frame phase information from the STM-1 as defined in ETS 300 147 [1].

**H1H2** - *AU-4* pointer interpretation: An AU-4 pointer consists of 2 bytes, [4, 1] and [4, 4]. The function shall perform AU-4 pointer interpretation according to annex B of EN 300 417-1-1 [3] to recover the VC-4 frame phase within the STM-1. The process shall maintain its current phase on detection of an invalid pointer and searches in parallel for a new phase.

**YY1\*1\*:** The bytes [4, 2], [4, 3], [4, 5], [4, 6] contain fixed stuff, of a specified value, ignored by the AU-4 pointer interpreter.

#### **Defects:**

*dAIS*: The dAIS defect shall be detected if the pointer interpreter is in the AIS\_state (see EN 300 417-1-1 [3], annex B). The dAIS defect shall be cleared if the pointer interpreter is not in the AIS\_state.

*dLOP*: The dLOP defect shall be detected if the pointer interpreter is in the LOP\_state (see EN 300 417-1-1 [3], annex B). The dLOP defect shall be cleared if the pointer interpreter is not in the LOP\_state.

#### **Consequent Actions:**

aAIS  $\leftarrow$  dAIS or dLOP.

aSSF  $\leftarrow$  dAIS or dLOP.

On declaration of aAIS the function shall output an all-ONEs (AIS) signal within 250  $\mu s;$  on clearing of aAIS the function shall output the recovered data within 250  $\mu s.$

#### **Defect Correlations:**

cAIS  $\leftarrow$  dAIS and (not AI\_TSF) and AIS\_Reported.

None.

$cLOP \leftarrow dLOP.$

**Performance Monitors:**

## 5.3.3 STM-1 Multiplex Section to DCC Adaptation Source MS1/DCC A So

Symbol:

Figure 26: MS1/DCC\_A\_So symbol

**Interfaces:**

Table 16: MS1/DCC\_A\_So input and output signals

| Input(s)   | Output(s)             |

|------------|-----------------------|

|            | MS1_AI_D<br>DCC_CI_CK |

| STM1_TI_FS |                       |

#### **Processes:**

The function multiplexes the DCC CI data (576 kbit/s) into the byte locations D4 to D12 as defined in ETS 300 147 [1] and depicted in figure 18.

NOTE: DCC transmission can be "disabled" when the matrix connection in the connected DCC\_C function is removed.

Defects: None.

Consequent Actions: None.

Defect Correlations: None.

Performance Monitoring: None.

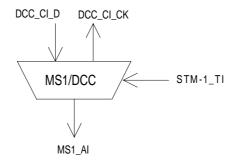

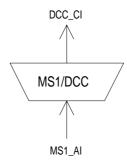

## 5.3.4 STM-1 Multiplex Section to DCC Adaptation Sink MS1/DCC\_A\_Sk

#### Symbol:

Figure 27: MS1/DCC\_A\_Sk symbol

**Interfaces:**

Table 17: MS1/DCC\_A\_Sk input and output signals

| Input(s)   | Output(s)  |

|------------|------------|

| MS1_AI_D   | DCC_CI_D   |

| MS1_AI_CK  | DCC_CI_CK  |

| MS1_AI_FS  | DCC_CI_SSF |

| MS1_AI_TSF |            |

#### **Processes:**

The function separates DCC data from MS Overhead as defined in ETS 300 147 [1] and depicted in figure 18.

NOTE: DCC processing can be "disabled" when the matrix connection in the connected DCC\_C function is

removed.

**Defects:** None.

**Consequent Actions:**

aSSF  $\leftarrow$  AI\_TSF.

**Defect Correlations:** None. **Performance Monitoring:** None.

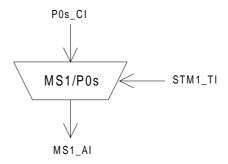

### 5.3.5 STM-1 Multiplex Section to P0s Adaptation Source MS1/P0s\_A\_So

#### Symbol:

Figure 28: MS1/P0s\_A\_So symbol

#### **Interfaces:**

Table 18: MS1/P0s\_A\_So input and output signals

| Input(s)   | Output(s) |

|------------|-----------|

| P0s_CI_D   | MS1_AI_D  |

| P0s_CI_CK  |           |

| P0s_CI_FS  |           |

| STM1_TI_CK |           |

| STM1_TI_FS |           |

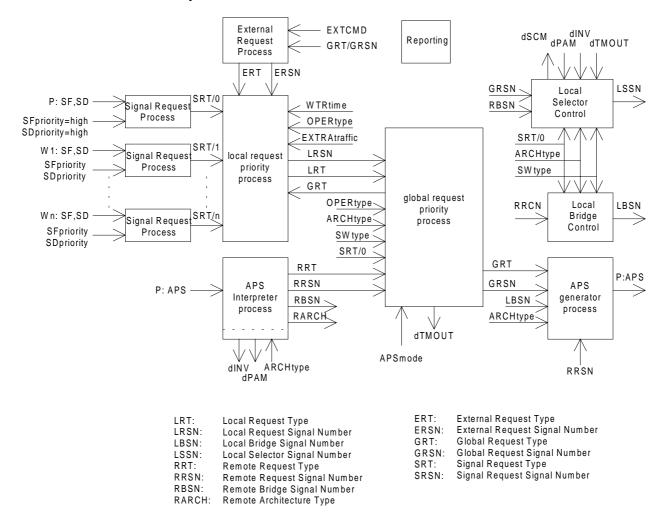

#### **Processes:**