# ETSI TS 102 080 V1.3.2 (2000-05)

Technical Specification

Transmission and Multiplexing (TM); Integrated Services Digital Network (ISDN) basic rate access; Digital transmission system on metallic local lines

Reference RTS/TM-06017-1

Keywords

ISDN, transmission, basic, rate, access, local loop, coding

#### ETSI

#### 650 Route des Lucioles F-06921 Sophia Antipolis Cedex - FRANCE

Tel.: +33 4 92 94 42 00 Fax: +33 4 93 65 47 16

Siret N° 348 623 562 00017 - NAF 742 C Association à but non lucratif enregistrée à la Sous-Préfecture de Grasse (06) N° 7803/88

Important notice

Individual copies of the present document can be downloaded from: http://www.etsi.org

The present document may be made available in more than one electronic version or in print. In any case of existing or perceived difference in contents between such versions, the reference version is the Portable Document Format (PDF). In case of dispute, the reference shall be the printing on ETSI printers of the PDF version kept on a specific network drive within ETSI Secretariat.

Users of the present document should be aware that the document may be subject to revision or change of status. Information on the current status of this and other ETSI documents is available at <a href="http://www.etsi.org/tb/status/">http://www.etsi.org/tb/status/</a>

> If you find errors in the present document, send your comment to: editor@etsi.fr

#### **Copyright Notification**

No part may be reproduced except as authorized by written permission. The copyright and the foregoing restriction extend to reproduction in all media.

> © European Telecommunications Standards Institute 2000. All rights reserved.

# Contents

| Intell     | lectual Property Rights                     | 8  |

|------------|---------------------------------------------|----|

| Forev      | word                                        | 8  |

| 1          | Scope                                       | 9  |

| 1.1        | Ôbjectives                                  | 9  |

| 2          | References                                  |    |

| 3          | Abbreviations                               |    |

|            |                                             |    |

| 4          | Functions                                   |    |

| 4.1        | B-channel                                   |    |

| 4.2        | D-channel                                   |    |

| 4.3        | Bit timing                                  |    |

| 4.4<br>4.5 | Octet timing<br>Frame alignment             |    |

| 4.5        | Activation from LT or NT1                   |    |

| 4.0        | Deactivation                                |    |

| 4.8        | Power feeding                               |    |

| 4.9        | Operations and maintenance                  |    |

| 4.9        |                                             |    |

| 5          | Transmission medium                         |    |

| 5.1        | Description                                 |    |

| 5.2        | Minimum ISDN requirements                   |    |

| 5.3        | DLL physical characteristics                |    |

| 5.4        | DLL characteristics                         |    |

| 5.4.1      | Principal characteristics                   |    |

| 5.4.2      |                                             |    |

| 5.4.3      |                                             |    |

| 5.4.4      |                                             |    |

| 5.4.5      | Micro interruptions                         |    |

| 6          | System performance                          |    |

| 6.1        | Performance requirements                    |    |

| 6.1.1      | System performance with Regenerators (REGs) |    |

| 6.2        | Performance measurements                    |    |

| 6.2.1      | DLL physical models                         |    |

| 6.2.2      | j                                           |    |

| 6.2.3      | 1 0                                         |    |

| 6.2.3.     |                                             |    |

| 6.2.3.     | 6                                           |    |

| 6.2.4      |                                             |    |

| 6.2.4.     |                                             |    |

| 6.2.4.     |                                             |    |

| 6.2.4.     |                                             |    |

| 6.2.5      | 1                                           |    |

| 6.3        | Unbalance about earth                       |    |

| 6.3.1      | Longitudinal conversion loss                |    |

| 6.3.2      |                                             |    |

| 7          | Transmission method                         | 25 |

| 8          | Activation/deactivation                     |    |

| 8.1        | General                                     |    |

| 8.2        | Physical representation of signals          |    |

| 9          | Operation and maintenance                   |    |

| 9.1        | Operation and maintenance functions         |    |

|            | -                                           |    |

| 9.2            | C <sub>L</sub> channel                                     |    |

|----------------|------------------------------------------------------------|----|

| 9.2.1          | C <sub>L</sub> channel definition                          |    |

| 9.2.2          | C <sub>L</sub> channel requirements                        |    |

| 9.3            | Metallic loop testing                                      |    |

| 10 1           |                                                            |    |

|                | Power feeding                                              |    |

| 10.1<br>10.2   | General                                                    |    |

| 10.2           | Power feeding functions                                    |    |

| 10.2.1         | Power feeding of the REG<br>Power feeding of the NT1       |    |

| 10.2.2         | Power feeding of the user network interface                |    |

| 10.2.3         | DLL resistance                                             |    |

| 10.3           | Wetting current                                            |    |

| 10.4           | LT aspects                                                 |    |

| 10.5.1         | Feeding voltage from the LT                                |    |

| 10.5.2         | Dynamic power feeding requirements                         |    |

| 10.5.3         | LT requirements for the reset of NT1 and REG               |    |

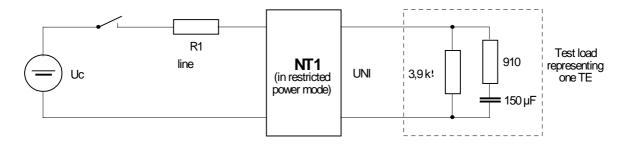

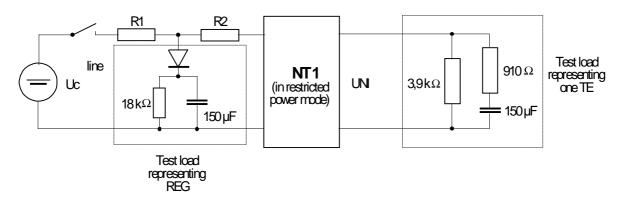

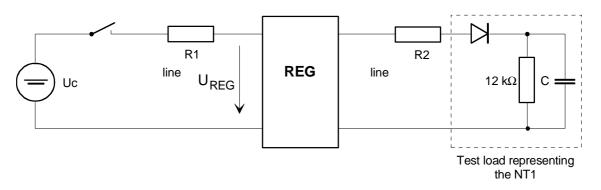

| 10.6           | Power requirements of NT1 and regenerator                  |    |

| 10.6.1         | Power requirements of NT1                                  |    |

| 10.6.1.1       |                                                            |    |

| 10.6.1.2       | -                                                          |    |

| 10.6.2         | Power requirement of regenerator                           |    |

| 10.6.2.1       |                                                            |    |

| 10.6.2.2       |                                                            |    |

| 10.6.3         | Feeding voltage to the NT1                                 |    |

| 10.6.4         | Voltage drop across the REG                                |    |

| 10.6.5         | Reset of NT1 and REG                                       |    |

| 10.7           | Current transient limitation                               |    |

| 10.8           | DC and low frequency AC termination of NT1 and REG         |    |

| 11 H           | Environmental conditions                                   | 32 |

| 11.1           | Climatic conditions                                        |    |

| 11.2           | Safety                                                     |    |

| 11.3           | Overvoltage protection                                     |    |

| 11.4           | EMC                                                        |    |

|                |                                                            |    |

| Annex          | A (normative): Definition of a system using 2B1Q line code | 34 |

| A.1 I          | Line code                                                  |    |

|                | Line baud rate                                             | 24 |

| A.2 I<br>A.2.1 | NT1 clock tolerance                                        |    |

| A.2.1<br>A.2.2 | LT clock tolerance                                         |    |

| A.2.2<br>A.2.3 | REG clock tolerance                                        |    |

|                |                                                            |    |

| A.3 I          | Frame structure                                            |    |

| A.3.1          | Frame length                                               |    |

| A.3.2          | Bit allocation in direction LT to NT1                      |    |

| A.3.3          | Bit allocation in direction NT1 to LT                      |    |

| A.4 I          | Frame word                                                 |    |

| A.4.1          | Frame word in direction LT to NT1                          |    |

| A.4.2          | Frame word in direction NT1 to LT.                         |    |

|                |                                                            |    |

| A.5 I          | Frame alignment procedure                                  |    |

| A.6 M          | Multiframe                                                 |    |

| A.6.1          | Multiframe word in direction NT1 to LT                     |    |

| A.6.2          | Multiframe word in direction LT to NT1                     |    |

|                |                                                            |    |

|     | 5                                                |    |

|-----|--------------------------------------------------|----|

| Fra | me offset between LT to NT1 and NT1 to LT frames |    |

| CL  | channel                                          |    |

| 2   | Bit rate                                         |    |

|     | Structure                                        |    |

|     | Protocol and procedures                          |    |

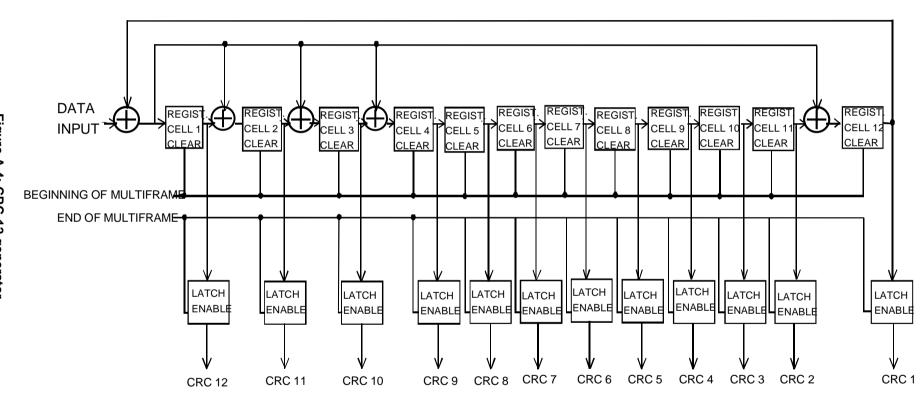

| 1   | Error monitoring function                        |    |

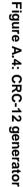

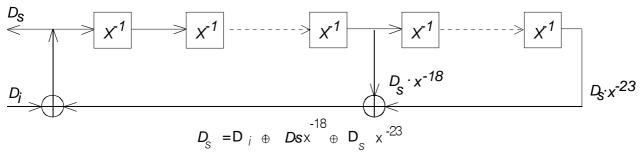

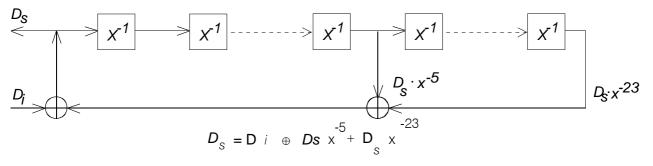

| 1.1 | Cyclic redundancy check                          |    |

| 1.2 | CRC algorithms                                   |    |

| 1.3 | Bits covered by the CRC                          |    |

| 2   | Other C <sub>L</sub> channel functions           |    |

| 2.1 | Far end block error bit, mandatory               |    |

| 2.2 | The ACT bit, mandatory                           |    |

| 2.3 | The DEA bit, mandatory                           |    |

| 2.4 | NT1 power status bits                            |    |

| 2.5 | NT1 Test Mode (NTM) indicator bit                |    |

| 2.6 | Cold-Start-Only (CSO) bit                        |    |

| 2.7 | DLL-Only-Activation (UOA) bit                    |    |

| 20  | S/T Interface Activity Indicator (SAI) bit       | 41 |

| A.8.3.1.3 Bits covered by the CRC                          | 41 |

|------------------------------------------------------------|----|

| A.8.3.2 Other C <sub>L</sub> channel functions             | 41 |

| A.8.3.2.1 Far end block error bit, mandatory               | 41 |

| A.8.3.2.2 The ACT bit, mandatory                           | 41 |

| A.8.3.2.3 The DEA bit, mandatory                           |    |

| A.8.3.2.4 NT1 power status bits                            |    |

| A.8.3.2.5 NT1 Test Mode (NTM) indicator bit                |    |

| A.8.3.2.6 Cold-Start-Only (CSO) bit                        |    |

| A.8.3.2.7 DLL-Only-Activation (UOA) bit                    |    |

| A.8.3.2.8 S/T-Interface-Activity-Indicator (SAI) bit       |    |

| A.8.3.2.9 Alarm Indicator Bit (AIB)                        |    |

| A.8.3.2.10 Network Indicator Bit (NIB) for network use     |    |

| A.8.3.2.11 Reserved bits                                   |    |

| A.8.3.3 Embedded Operations Channel (EOC) functions        |    |

| A.8.3.3.1 EOC frame                                        |    |

| A.8.3.3.2 Mode of operation                                |    |

| A.8.3.3.3 Addressing                                       |    |

| A.8.3.3.4 Definition of required EOC functions             |    |

| A.8.3.3.5 Codes for required EOC functions                 |    |

|                                                            |    |

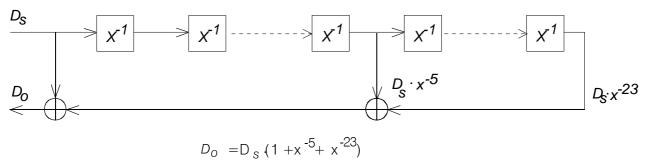

| A.9 Scrambling                                             | 44 |

| A.10 Start-up and control                                  |    |

| A.10.1 Signals used for start-up and control               |    |

| A.10.1.1 Signals during start-up                           |    |

| A.10.1.2 Line rate during start-up                         |    |

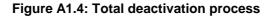

| A.10.1.3 Start-up sequence                                 |    |

| A.10.1.4 Wake-up.                                          |    |

| A.10.1.5 Progress indicators                               |    |

| A.10.1.5.1 Start-up                                        |    |

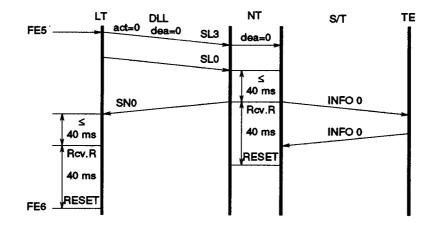

| A.10.1.5.2 Deactivation                                    |    |

| A.10.2 Timers                                              |    |

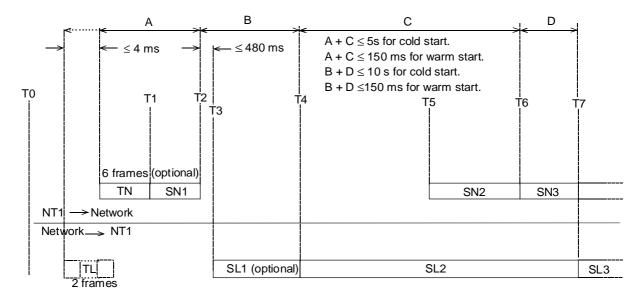

| A.10.3 Description of the start-up procedure               |    |

| A.10.3.1 Start-up from customer equipment                  |    |

| A.10.3.2 Start-up from the network                         |    |

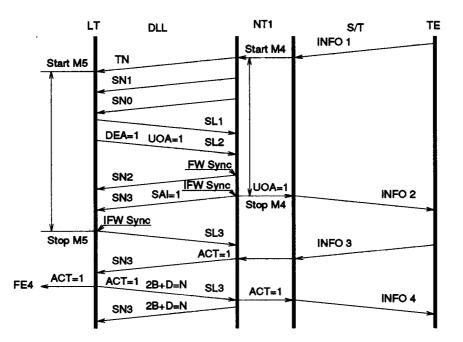

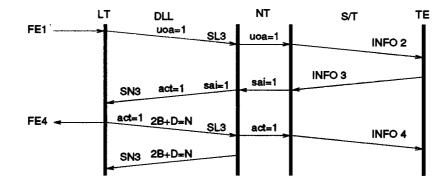

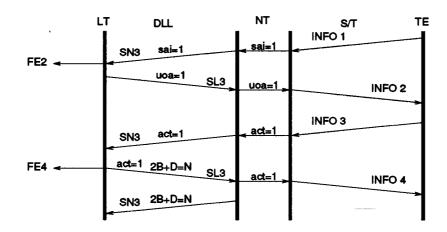

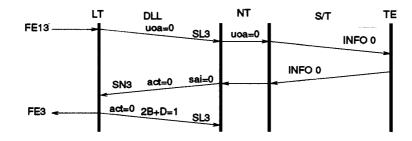

| A.10.3.3 Sequence charts                                   |    |

| A.10.3.4 Transparency                                      |    |

| A.10.4 State transition table for the NT1                  |    |

| A.10.5 State transition table for the LT                   |    |

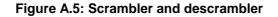

| A.10.6 Activation times.                                   |    |

|                                                            |    |

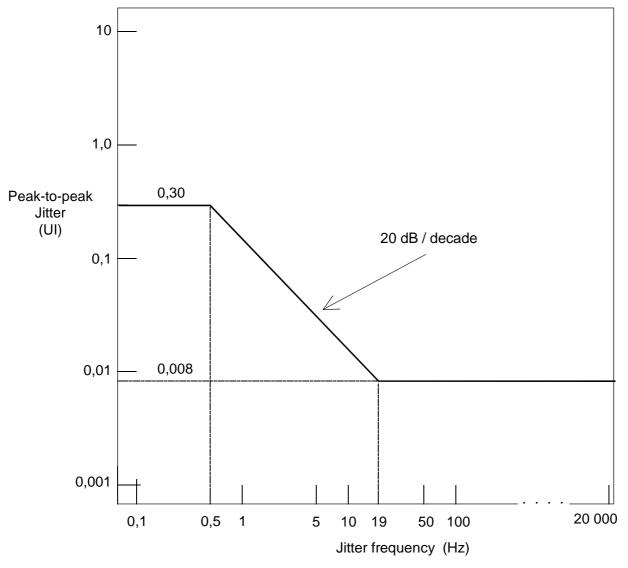

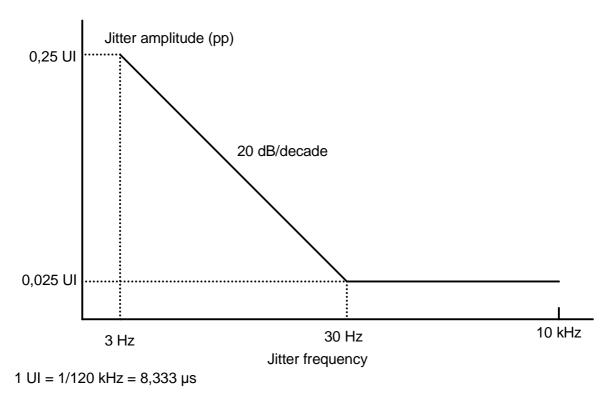

| A.11 Jitter                                                |    |

| A.11.1 NT1 input signal jitter tolerance                   |    |

| A.11.2 NT1 output jitter limitations                       |    |

| A.11.3 LT input signal jitter tolerance                    |    |

| A.11.4 LT output jitter and synchronization                |    |

| A.11.5 REG jitter tolerance and output jitter limitations  |    |

| A.11.6 Test conditions for jitter measurements             | 63 |

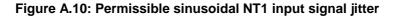

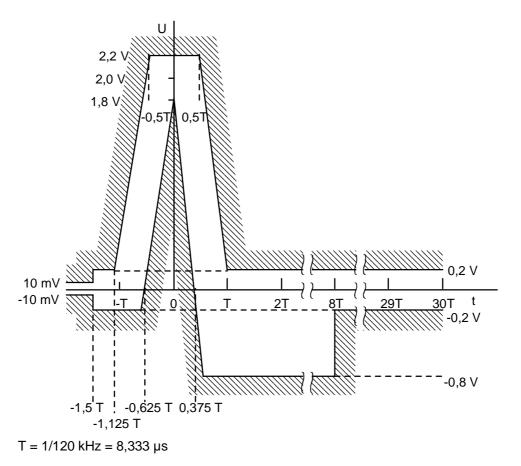

| A.12 Transmitter output characteristics of NT1, REG and LT |    |

| A.12.1 Pulse amplitude                                     |    |

| A.12.2 Pulse shape                                         |    |

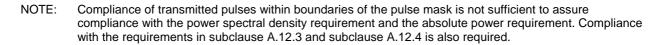

| A.12.3 Signal power                                        |    |

| Power Power                                                |    |

A.7

A.8

A.8.1

A.8.2

A.8.3

A.8.3.1

A.8.3.1.1

A.8.3.1.2

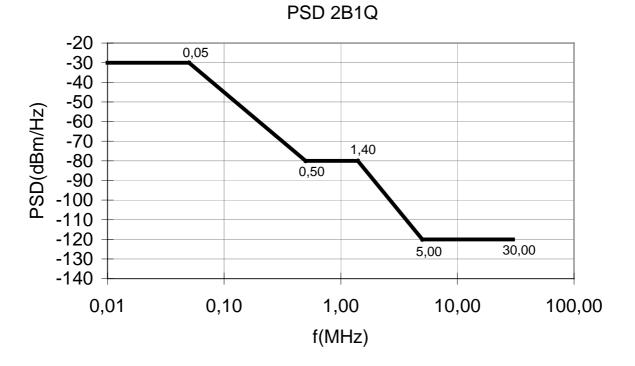

| A.12.4<br>A.12.4.1<br>A.12.5<br>A.12.5.1<br>A.12.5.2 | Transmitter linearity<br>Requirements<br>Linearity test method                              | 65<br>66<br>66<br>66 |

|------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------|

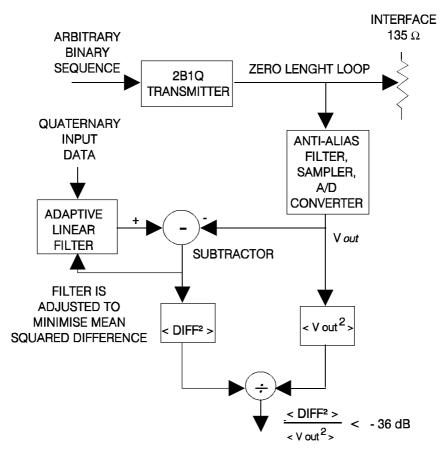

| A.13 T<br>A.13.1<br>A.13.2<br>A.13.3<br>A.13.3.1     | 'ransmitter/receiver termination                                                            | 67<br>67<br>67       |

| Annex                                                | A1 (informative): Extension functions of the system using 2B1Q line code                    | 69                   |

| A1.1 Ir                                              | ntroduction                                                                                 | 69                   |

| A1.2 N                                               | T1 Power status bits                                                                        | 69                   |

| A1.3 N                                               | TM bit                                                                                      | 69                   |

| A1.4 C                                               | SO bit                                                                                      | 70                   |

| A1.5 U                                               | JOA bit                                                                                     | 70                   |

| A1.6 S.                                              | AI bit                                                                                      | 70                   |

| A1.7 A                                               | JIB                                                                                         | 70                   |

| Annex                                                | A2 (informative): Discussion of EOC addressing                                              | 78                   |

|                                                      | Addresses 1 through 6 (intermediate elements)                                               |                      |

|                                                      | action of intermediate elements                                                             |                      |

|                                                      | action of NT                                                                                |                      |

|                                                      | ummary                                                                                      |                      |

|                                                      | B (normative): Definition of a system using Modified Monitoring State (MMS) 43<br>line code |                      |

| B.1 L                                                | ine code                                                                                    | 80                   |

| B.2 S                                                | ymbol rate                                                                                  | 80                   |

| B.2.1<br>B.2.1.1                                     | Clock symbol requirements                                                                   |                      |

| В.2.1.1<br>В.2.1.2                                   | LT clock tolerance                                                                          |                      |

| B.3 F                                                | rame structure                                                                              | 80                   |

| B.3.1                                                | Frame length                                                                                |                      |

| B.3.2<br>B.3.3                                       | Symbol allocation LT to NT1<br>Symbol allocation NT1 to LT                                  |                      |

| B.4 F                                                | rame word                                                                                   | 81                   |

| B.4.1                                                | Frame word in direction LT to NT1                                                           |                      |

| B.4.2                                                | Frame word in direction NT1 to LT                                                           |                      |

|                                                      |                                                                                             |                      |

|                                                      | Iultiframe                                                                                  |                      |

|                                                      | rame offset at NT1                                                                          |                      |

| B.8 C<br>B.8.1                                       | C <sub>L</sub> channel<br>Bit rate                                                          |                      |

| B.8.2                                                | Structure                                                                                   | 82                   |

| B.8.3                                                | Protocols and procedures                                                                    | 82                   |

| B.10 Activation/deactivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| B.10.1 Signals used for activation                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                          |

| B.10.2 Definition of internal timers                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                          |

| B.10.3 Description of the activation procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                          |

| B.10.4 NT1 state transition table                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                          |

| B.10.5 LT state transition table                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                          |

| B.10.6 Activation times                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                          |

| B.11 Jitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 90                                                                                                                                       |

| B.11.1 Limits of maximum tolerable input jitter                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                          |

| B.11.2 Output jitter of NT1 in absence of input jitter                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                          |

| B.11.3 Timing extraction jitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                          |

| B.11.4 Test conditions for jitter measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                          |

| B.12 Transmitter output characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 91                                                                                                                                       |

| B.12.1 Pulse amplitude                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                          |

| B.12.2 Pulse shape                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                          |

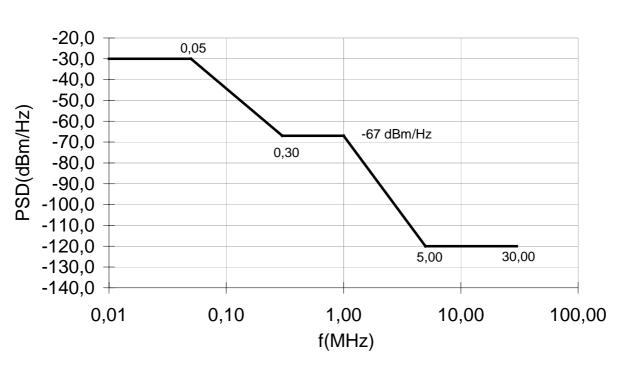

| B.12.3 Signal power                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                          |

| B.12.4 Power spectral density                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                          |

| B.12.4.1 Sliding window PSD requirement                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                          |

| B.12.5 Transmitter signal non-linearity                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                          |

| B.13 Transmitter/receiver termination                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 94                                                                                                                                       |

| B.13.1 Impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                          |

| B.13.2 Return loss                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                          |

| B.13.3 Longitudinal conversion loss                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 94                                                                                                                                       |

| Annex B1 (informative): Extension functions for a system with MM                                                                                                                                                                                                                                                                                                                                                                                                                               | /IS43 line code95                                                                                                                        |

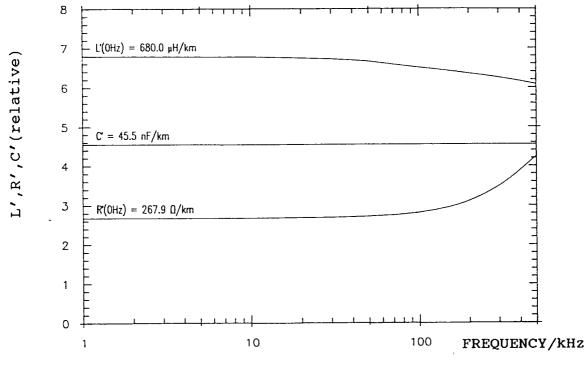

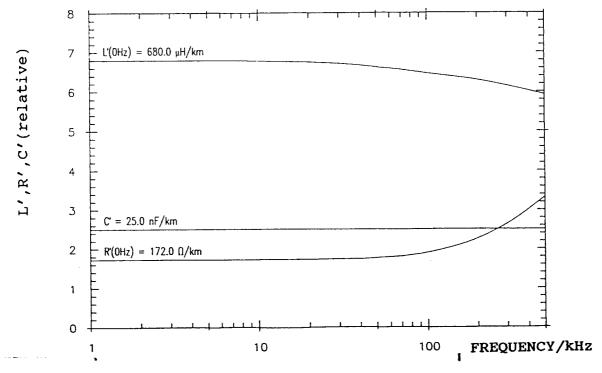

| Annex C (informative): Detailed test cable characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                          |

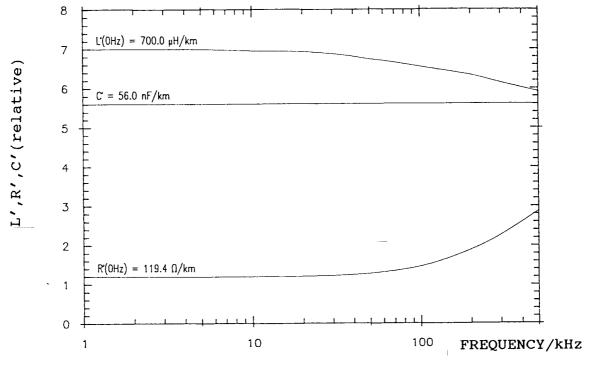

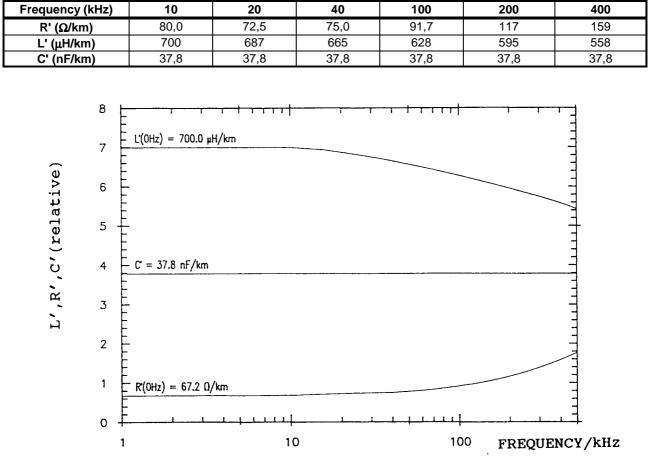

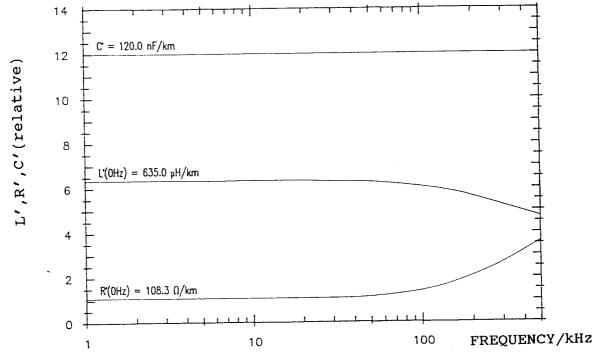

| C.1.1 Parameters of 0,4 mm PE cable<br>C.1.2 Parameters of 0.5 mm PE cable                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                          |

| C.1.3 Parameters of 0,6 mm PE cable                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                          |

| C.1.4 Parameters of 0,8 mm PE cable                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 00                                                                                                                                       |

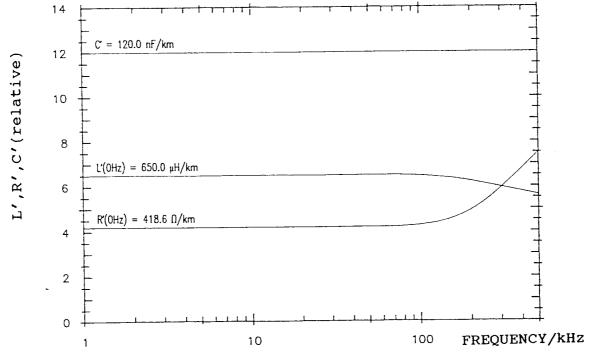

| C.1.5 Parameters of 0,32 mm PVC cable                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                          |

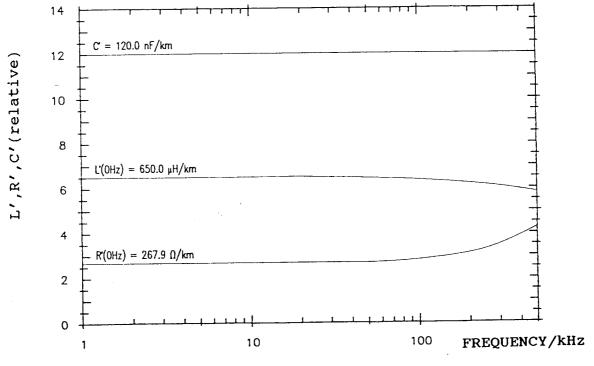

| C.1.6 Parameters of 0,4 mm PVC cable                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                          |

| C.1.7 Parameters of 0,63 mm PVC cable                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                          |

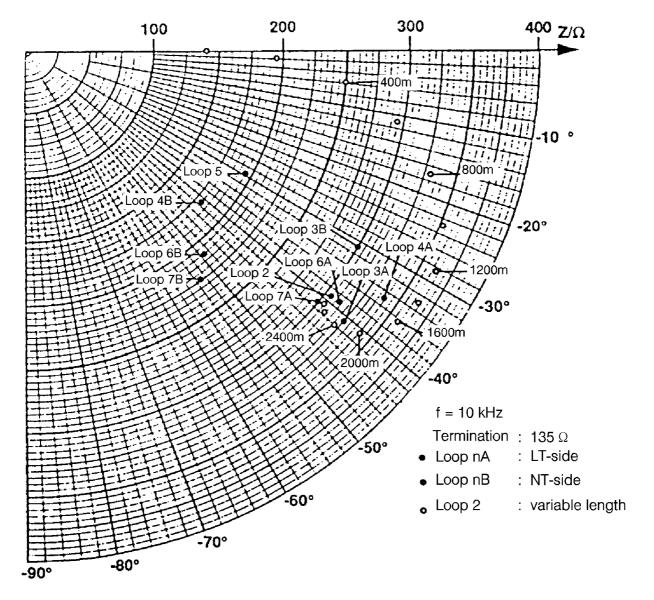

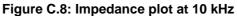

| <ul><li>C.1.7 Parameters of 0,63 mm PVC cable</li><li>C.2 Impedance plot of test loops</li></ul>                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                          |

| <ul> <li>C.1.7 Parameters of 0,63 mm PVC cable</li> <li>C.2 Impedance plot of test loops</li> <li>C.2.1 Impedance plot at 10 kHz</li> </ul>                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                          |

| <ul> <li>C.1.7 Parameters of 0,63 mm PVC cable</li> <li>C.2 Impedance plot of test loops</li> <li>C.2.1 Impedance plot at 10 kHz</li> <li>C.2.2 Impedance plot at 20 kHz</li> </ul>                                                                                                                                                                                                                                                                                                            |                                                                                                                                          |

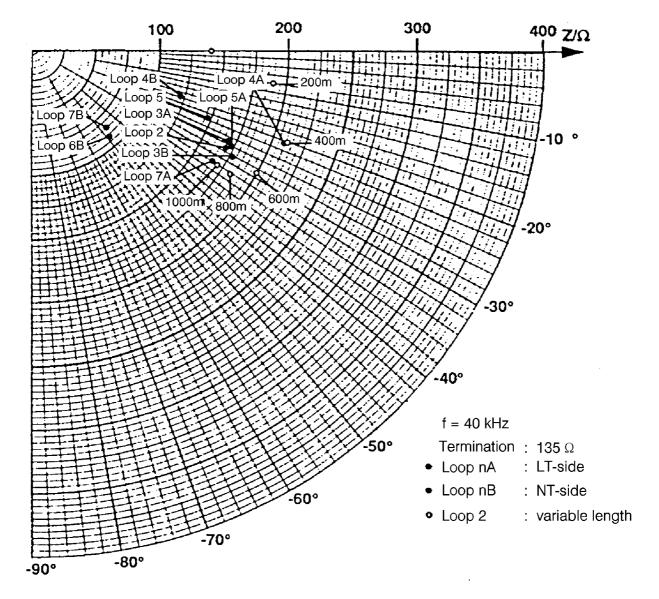

| <ul> <li>C.1.7 Parameters of 0,63 mm PVC cable.</li> <li>C.2 Impedance plot of test loops</li> <li>C.2.1 Impedance plot at 10 kHz</li> <li>C.2.2 Impedance plot at 20 kHz</li> <li>C.2.3 Impedance plot at 40 kHz</li> </ul>                                                                                                                                                                                                                                                                   | 100<br>101<br>102<br>103<br>103<br>104<br>104                                                                                            |

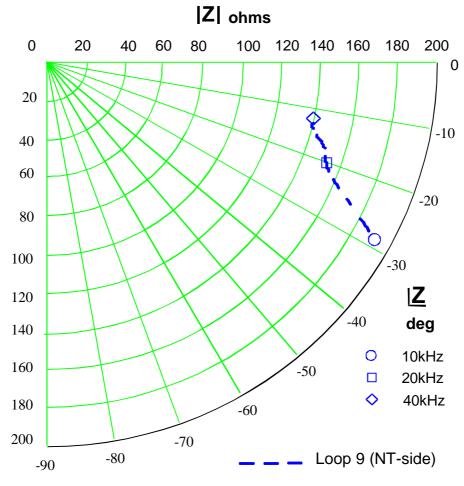

| <ul> <li>C.1.7 Parameters of 0,63 mm PVC cable</li> <li>C.2 Impedance plot of test loops</li> <li>C.2.1 Impedance plot at 10 kHz</li> <li>C.2.2 Impedance plot at 20 kHz</li> <li>C.2.3 Impedance plot at 40 kHz</li> <li>C.2.4 Impedance plot loop 9</li> </ul>                                                                                                                                                                                                                               | 100<br>101<br>102<br>103<br>103<br>103<br>104<br>105<br>106                                                                              |

| <ul> <li>C.1.7 Parameters of 0,63 mm PVC cable.</li> <li>C.2 Impedance plot of test loops</li> <li>C.2.1 Impedance plot at 10 kHz</li> <li>C.2.2 Impedance plot at 20 kHz</li> <li>C.2.3 Impedance plot at 40 kHz</li> <li>C.2.4 Impedance plot loop 9</li> <li>C.3 Frequency response of test loops</li> </ul>                                                                                                                                                                                | 100<br>101<br>102<br>103<br>103<br>103<br>104<br>105<br>106<br>107                                                                       |

| <ul> <li>C.1.7 Parameters of 0,63 mm PVC cable.</li> <li>C.2 Impedance plot of test loops</li> <li>C.2.1 Impedance plot at 10 kHz.</li> <li>C.2.2 Impedance plot at 20 kHz.</li> <li>C.2.3 Impedance plot at 40 kHz.</li> <li>C.2.4 Impedance plot loop 9</li> <li>C.3 Frequency response of test loops</li> <li>C.3.1 Frequency response of loop 2</li> </ul>                                                                                                                                 | 100<br>101<br>102<br>103<br>103<br>103<br>104<br>105<br>106<br>107<br>107                                                                |

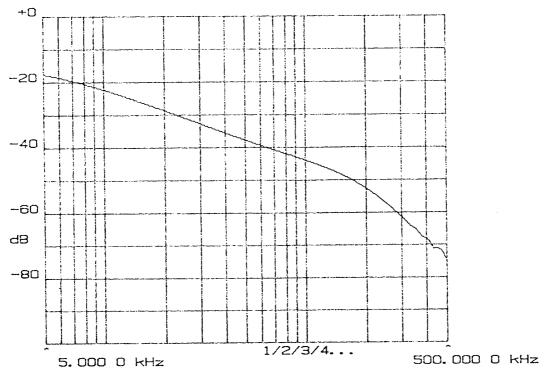

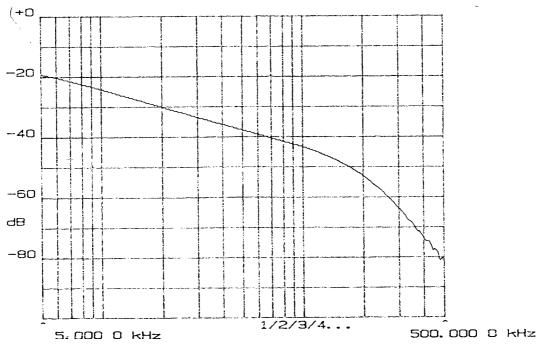

| <ul> <li>C.1.7 Parameters of 0,63 mm PVC cable</li> <li>C.2 Impedance plot of test loops</li> <li>C.2.1 Impedance plot at 10 kHz</li> <li>C.2.2 Impedance plot at 20 kHz</li> <li>C.2.3 Impedance plot at 40 kHz</li> <li>C.2.4 Impedance plot loop 9</li> <li>C.3 Frequency response of test loops</li> <li>C.3.1 Frequency response of loop 2</li> <li>C.3.2 Frequency response of loop 3</li> </ul>                                                                                         | 100<br>101<br>102<br>103<br>103<br>104<br>105<br>106<br>107<br>107<br>107                                                                |

| <ul> <li>C.1.7 Parameters of 0,63 mm PVC cable</li> <li>C.2 Impedance plot of test loops</li> <li>C.2.1 Impedance plot at 10 kHz</li> <li>C.2.2 Impedance plot at 20 kHz</li> <li>C.2.3 Impedance plot at 40 kHz</li> <li>C.2.4 Impedance plot loop 9</li> <li>C.3 Frequency response of test loops</li> <li>C.3.1 Frequency response of loop 2</li> <li>C.3.2 Frequency response of loop 3</li> <li>C.3.3 Frequency response of loop 4</li> </ul>                                             | 100<br>101<br>102<br>103<br>103<br>103<br>104<br>104<br>105<br>106<br>106<br>107<br>107<br>107<br>107                                    |

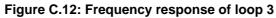

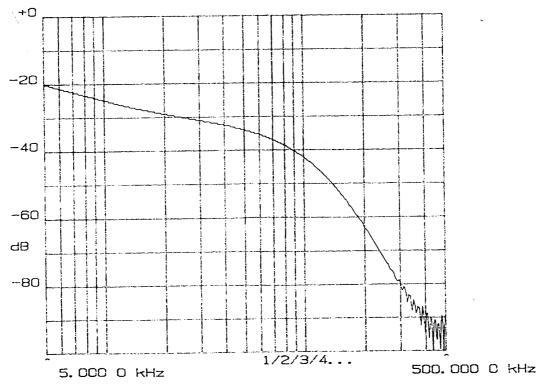

| <ul> <li>C.1.7 Parameters of 0,63 mm PVC cable</li> <li>C.2 Impedance plot of test loops</li> <li>C.2.1 Impedance plot at 10 kHz</li> <li>C.2.2 Impedance plot at 20 kHz</li> <li>C.2.3 Impedance plot at 40 kHz</li> <li>C.2.4 Impedance plot loop 9</li> <li>C.3 Frequency response of test loops</li> <li>C.3.1 Frequency response of loop 2</li> <li>C.3.2 Frequency response of loop 3</li> <li>C.3.3 Frequency response of loop 4</li> <li>C.3.4 Frequency response of loop 5</li> </ul> | 100<br>101<br>102<br>103<br>103<br>103<br>104<br>105<br>106<br>106<br>107<br>107<br>107<br>107<br>108<br>108                             |

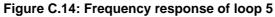

| <ul> <li>C.1.7 Parameters of 0,63 mm PVC cable.</li> <li>C.2 Impedance plot of test loops</li></ul>                                                                                                                                                                                                                                                                                                                                                                                            | 100<br>101<br>102<br>103<br>103<br>103<br>104<br>105<br>106<br>107<br>107<br>107<br>107<br>107<br>107<br>108<br>108<br>108               |

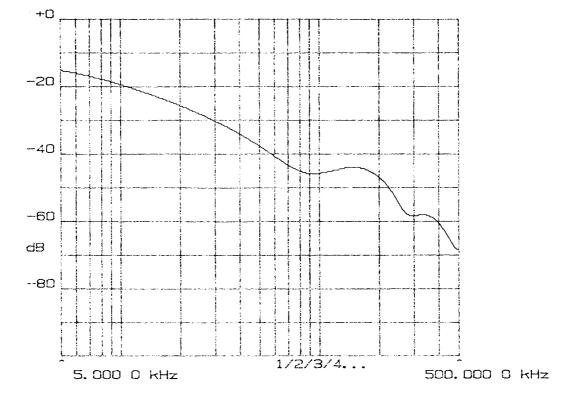

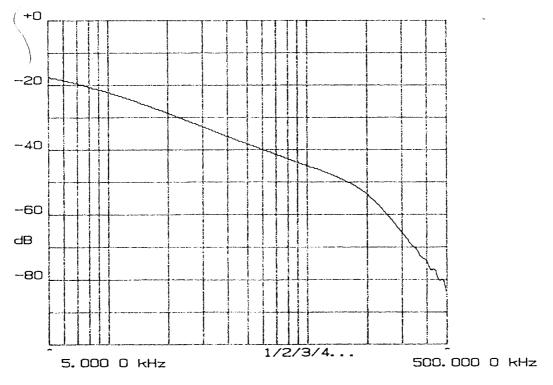

| <ul> <li>C.1.7 Parameters of 0,63 mm PVC cable.</li> <li>C.2 Impedance plot of test loops</li></ul>                                                                                                                                                                                                                                                                                                                                                                                            | 100<br>101<br>102<br>103<br>103<br>104<br>105<br>106<br>107<br>107<br>107<br>107<br>107<br>107<br>108<br>108<br>108<br>109               |

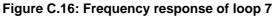

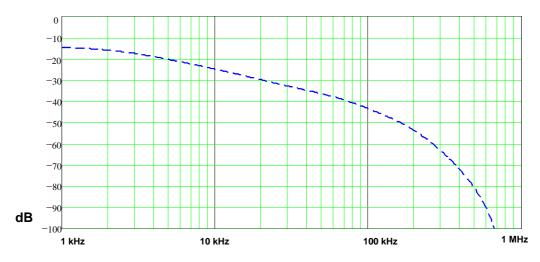

| <ul> <li>C.1.7 Parameters of 0,63 mm PVC cable.</li> <li>C.2 Impedance plot of test loops</li></ul>                                                                                                                                                                                                                                                                                                                                                                                            | 100<br>101<br>102<br>103<br>103<br>103<br>104<br>105<br>106<br>107<br>107<br>107<br>107<br>107<br>107<br>108<br>108<br>108<br>109<br>109 |

| <ul> <li>C.1.7 Parameters of 0,63 mm PVC cable.</li> <li>C.2 Impedance plot of test loops</li></ul>                                                                                                                                                                                                                                                                                                                                                                                            | 100<br>101<br>102<br>103<br>103<br>103<br>104<br>105<br>106<br>107<br>107<br>107<br>107<br>107<br>107<br>108<br>108<br>108<br>109<br>109 |

| <ul> <li>C.1.7 Parameters of 0,63 mm PVC cable.</li> <li>C.2 Impedance plot of test loops</li></ul>                                                                                                                                                                                                                                                                                                                                                                                            | 100<br>101<br>102<br>103<br>103<br>103<br>104<br>105<br>106<br>107<br>107<br>107<br>107<br>107<br>107<br>107<br>107                      |

# Intellectual Property Rights

IPRs essential or potentially essential to the present document may have been declared to ETSI. The information pertaining to these essential IPRs, if any, is publicly available for **ETSI members and non-members**, and can be found in SR 000 314: "*Intellectual Property Rights (IPRs); Essential, or potentially Essential, IPRs notified to ETSI in respect of ETSI standards*", which is available from the ETSI Secretariat. Latest updates are available on the ETSI Web server (http://www.etsi.org/ipr).

Pursuant to the ETSI IPR Policy, no investigation, including IPR searches, has been carried out by ETSI. No guarantee can be given as to the existence of other IPRs not referenced in SR 000 314 (or the updates on the ETSI Web server) which are, or may be, or may become, essential to the present document.

# Foreword

This Technical Specification (TS) has been produced by ETSI Technical Committee Transmission and Multiplexing (TM).

The present editorial update does improve the safety related provisions in the document.

### 1 Scope

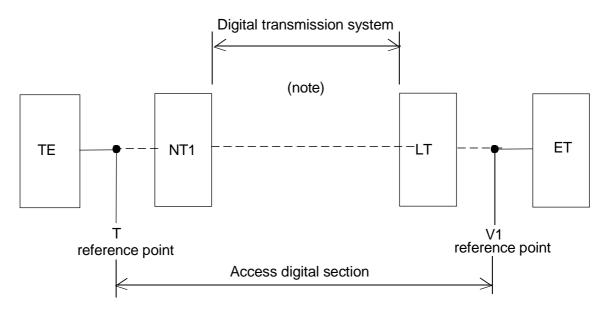

The present document covers the characteristics and parameters of a digital transmission system at the network side of the NT1 to form part of the access digital section for the Integrated Services Digital Network (ISDN) basic rate access using echo cancellation method.

The present document specifies support for:

- full duplex; and

- bit sequence independent,

transmission of two B-channels and one D-channel as defined in ITU-T Recommendation I.412 [12] and the supplementary functions of the access digital section defined in ETR 001 [7].

The line codes of systems specified in the present document are 2B1Q (2 Binary 1 Quaternary) and MMS 43-code (Modified Monitoring State 43-code). Systems using a 2B1Q line code are covered in annex A. Systems using a MMS line code are covered in annex B. Only one of the line codes has to be realized in a transmission system. Figure 1 shows the boundaries of the digital transmission system in relation to the access digital section.

NOTE: In the present document, digital transmission system refers to a line system using metallic local lines. The use of one intermediate regenerator (REG) may be required.

#### Figure 1: Access digital section and transmission system boundaries

The concept of the access digital section is used in order to allow a functional and procedural description and a definition of the network requirements.

NOTE: The reference points T and V<sub>1</sub> are not identical and therefore the access digital section is not symmetric.

The concept of a digital transmission system is used in order to describe the characteristics of an implementation, using a specific medium, in support of the access digital section.

#### 1.1 Objectives

Considering that the access digital section between the local exchange and the customer is one key element of the successful introduction of ISDN into the network, the following requirements for the specification have been taken into account:

- to operate on existing 2-wire unloaded lines, open wires being excluded;

- the objective is to achieve 100 % cable fill for ISDN basic access without pair selection, cable rearrangements or removal of Bridged Taps (BTs);

- the objective to be able to extend ISDN basic access provided services to the majority of customers without the use of regenerators. In the remaining few cases, special arrangements may be required;

- coexistence in the same cable unit with most of the existing services like telephony and voice band data transmission;

- various national regulations concerning Electro-Magnetic Compatibility (EMC) should be taken into account;

- power feeding from the network under normal or restricted modes via the basic access to be provided;

- the capability to support maintenance functions to be provided.

### 2 References

The following documents contain provisions which, through reference in this text, constitute provisions of the present document.

- References are either specific (identified by date of publication, edition number, version number, etc.) or non-specific.

- For a specific reference, subsequent revisions do not apply.

- For a non-specific reference, the latest version applies.

- A non-specific reference to an ETS shall also be taken to refer to later versions published as an EN with the same number.

- [1] ETSI ETS 300 012 (1998): "Integrated Services Digital Network (ISDN); Basic user-network interface; Layer 1 specification and test principles".

- [2] ETSI ETS 300 019 (1994): "Equipment Engineering (EE); Environmental conditions and environmental tests for telecommunications equipment".

- [3] ETSI ETS 300 047-5 (1992): "Integrated Services Digital Network (ISDN); Basic access safety and protection; Part 5: Interface I<sub>b</sub> protection".

- [4] ETSI ETS 300 297 (1995): "Integrated Services Digital Network (ISDN); Access digital section for ISDN basic access".

- [5] ETSI ETS 300 386-1 (1994): "Equipment Engineering (EE); Telecommunication network equipment; Electro-Magnetic Compatibility (EMC) requirements; Part 1: Product family overview, compliance criteria and test levels".

- [6] ETSI EN 300 386-2 (V1.1): "Electromagnetic compatibility and Radio spectrum Matters (ERM); Telecommunication network equipment; ElectroMagnetic Compatibility (EMC) requirements; Part 2: Product family standard".

- [7] ETSI ETR 001 (1990): "Integrated Services Digital Network (ISDN); Customer access maintenance".

- [8] ETSI EN 60950: "Safety of information technology equipment including electrical business equipment.".

- [9] ITU-T Recommendation G.117 (1996): "Transmission aspects of unbalance about earth".

- [10] ITU-T Recommendation G.821 (1996): "Error performance of an international digital connection operating at a bit rate below the primary rate and forming part of an integrated services digital network".

- [11] ITU-T Recommendation G.823 (1993): "The control of jitter and wander within digital networks which are based on the 2 048 kbit/s hierarchy".

| [12] | ITU-T Recommendation I.412 (1988): "ISDN user-network interfaces - Interface structures and access capabilities".                                                             |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [13] | ITU-T Recommendation K.17 (1988): "Tests on power-fed repeaters using solid-state devices in order to check the arrangements for protection from external interference".      |

| [14] | ITU-T Recommendation K.20 (1996): "Resistibility of telecommunication switching equipment to overvoltages and overcurrents".                                                  |

| [15] | ITU-T Recommendation K.21(1996): "Resistibility of subscriber's terminal to overvoltages and overcurrent".                                                                    |

| [16] | Council Directive 89/336/EEC of 3 May 1989 on the approximation of the laws of the Member States relating to electromagnetic compatibility.                                   |

| [17] | ETSI ETR 080 (1996): "Transmission and Multiplexing (TM); Integrated Services Digital Network (ISDN) basic rate access; Digital transmission system on metallic local lines". |

| [18] | ETSI EG 201 212: "Electrical Safety; Classification of interfaces for equipment to be connected to telecommunication networks."                                               |

# 3 Abbreviations

For the purposes of the present document, the following abbreviations apply:

| 2B1Q | 2 Binary, 1 Quaternary              |

|------|-------------------------------------|

| A/D  | Analogue to Digital                 |

| AC   | Alternating Current                 |

| AIB  | Alarm Indicator Bit                 |

| BER  | Bit Error Rate                      |

| BT   | Bridged Tap                         |

| CCP  | Cross Connection Point              |

| CRC  | Cyclic Redundancy Check             |

| CSO  | Cold-Start-Only                     |

| DC   | Direct Current                      |

| DLL  | Digital Local Line                  |

| DSL  | Digital Subscriber Line             |

| DTS  | Digital Transmission System         |

| EC   | Echo Canceller                      |

| ECH  | Echo Cancellation Hybrid            |

| EMC  | ElectroMagnetic Compatibility       |

| EOC  | Embedded Operations Channel         |

| ET   | Exchange Termination                |

| FE   | Failure Element                     |

| FEBE | Far End Block Error                 |

| FW   | Frame Word                          |

| IFW  | Inverted Frame Word                 |

| ISDN | Integrated Services Digital Network |

| LCL  | Longitudinal Conversion Loss        |

| LT   | Line Termination                    |

| MDF  | Main Distribution Frame             |

| MMS  | Modified Monitoring State           |

| NEXT | Near End Crosstalk                  |

| NIB  | Network Indicator Bit               |

| NT   | Network Termination                 |

| NTM  | NT1 Test Mode                       |

| ppm  | parts per million                   |

| PSL  | Power Sum Loss                      |

| REG  | Regenerator                         |

| rms  | root mean squared                   |

|      |                                     |

| SAI | S/T-interface-Activity Indicator |

|-----|----------------------------------|

| SDP | Subscriber Distribution Point    |

| TE  | Terminal Equipment               |

| UI  | Unit Interval                    |

| UNI | User Network Interface           |

| UOA | DLL-Only-Activation              |

|     |                                  |

# 4 Functions

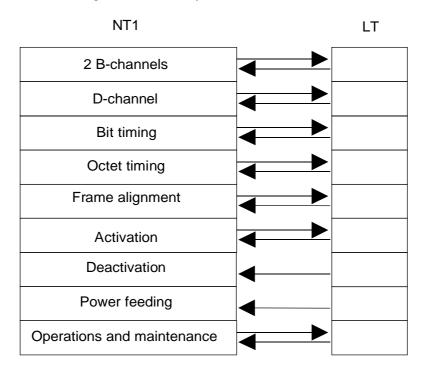

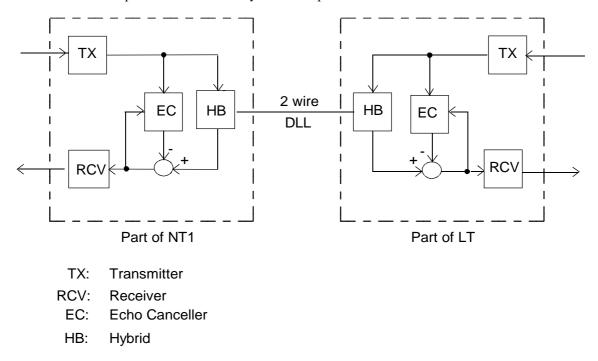

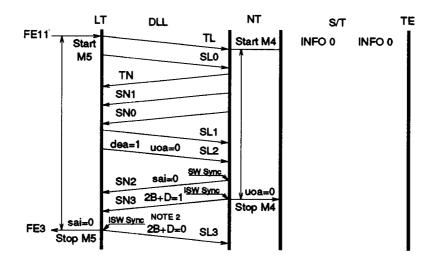

Figure 2 shows the functions of the digital transmission system on metallic local lines.

12

NOTE: The optional use of one regenerator shall be foreseen.

#### Figure 2: Functions of the digital transmission system

#### 4.1 B-channel

This function provides, for each direction of transmission, two independent 64 kbit/s channels for use as B-channels (as defined in ITU-T Recommendation I.412 [12]).

#### 4.2 D-channel

This function provides, for each direction of transmission, one D-channel at a bit rate of 16 kbit/s, (as defined in ITU-T Recommendation I.412 [12]).

### 4.3 Bit timing

This function provides bit (signal element) timing to enable the receiving equipment to recover information from the aggregate bit stream. Bit timing for the direction NT1 to LT shall be derived from the clock received by the NT1 from the LT.

#### 4.4 Octet timing

This function provides 8 kHz octet timing for the B-channels. It shall be derived from the frame alignment.

### 4.5 Frame alignment

This function enables the NT1 and the LT to recover the time division multiplexed channels.

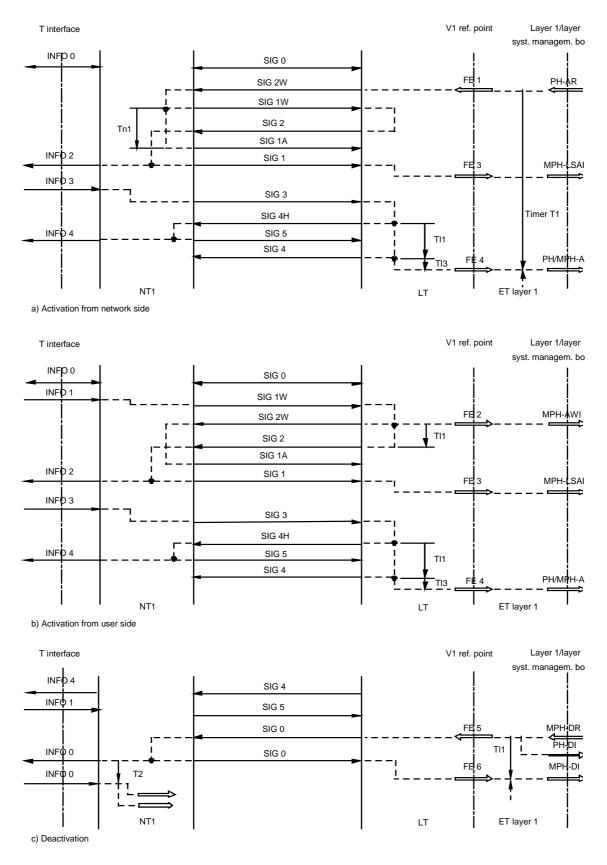

### 4.6 Activation from LT or NT1

This function restores the Digital Transmission System (DTS) between the LT and NT1 to its normal operational status. Procedures required to implement this function are described in clause 8.

13

Activation from the LT may apply to the DTS only or to the DTS plus the customer equipment. In case the customer equipment is not connected, the DTS can still be activated (see note in subclause 4.9).

### 4.7 Deactivation

This function is specified in order to permit the NT1 and the regenerator (if it exists) to be placed in a low power consumption mode or to reduce intrasystem crosstalk to other systems. The procedures and exchange of information are described in clause 8. This deactivation should be initiated only by the exchange (ET).

### 4.8 Power feeding

This function provides for remote power feeding of one regenerator (if required), NT1 and restricted mode power feeding at the T reference point.

NOTE: The general power feeding strategy, given in clause 10, may not be applicable for extremely long local lines. In such cases, specific power feeding methods (e.g. use of batteries in the NT1 or local power feeding of the NT1) may be applied. The specific methods are outside the scope of the present document.

### 4.9 Operations and maintenance

This function provides the recommended actions and information described in ETR 001 [7].

The following categories of functions have been identified:

- maintenance command (e.g. loopback control in the regenerator or the NT1);

- maintenance information (e.g. line errors);

- indication of fault conditions;

- information regarding power feeding in NT1.

- NOTE: The functions required for operations and maintenance of the NT1 and one regenerator (if required) and for some activation/deactivation procedures are combined in one transport capability to be transmitted along with the 2B+D channels. This transport capability is named the  $C_L$  channel.

# 5 Transmission medium

### 5.1 Description

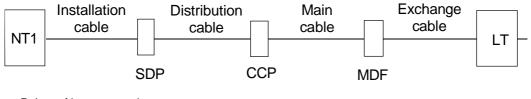

The transmission medium over which the digital transmission system is expected to operate, is the local line distribution network.

A local line distribution network employs cables of pairs to provide services to customers.

In a local line distribution network, customers are connected to the local exchange via local lines.

A metallic local line is expected to be able to simultaneously carry bidirectional digital transmission providing ISDN basic rate access between LT and NT1.

To simplify the provision of ISDN basic access, a digital transmission system shall be capable of satisfactory operation over the majority of metallic local lines without requirement of any special conditioning. Maximum penetration of metallic local lines is obtained by keeping ISDN requirements at a minimum.

In the following, the term Digital Local Line (DLL) is used to describe a metallic local line that meets minimum ISDN requirements.

### 5.2 Minimum ISDN requirements

- a) No loading coils;

- b) No open wires;

- c) When bridged taps (BTs) are present, the following rules apply:

- maximum number of BTs: 2;

- maximum BT length: 500 m.

NOTE: A BT is an unterminated twisted pair section bridged across the line.

### 5.3 DLL physical characteristics

In addition to satisfying the minimum ISDN requirements, a DLL is constructed of one or more cable sections that are spliced or interconnected together.

The distribution or main cable is structured as follows:

- cascade of cable sections of different diameters and lengths;

- one or more BTs may exist at various points in feeder and distribution cables.

A general description is shown in figure 3 and typical examples of cable characteristics are given in table 1.

Points of interconnection:

- MDF: Main Distribution Frame

- CCP: Cross Connection Point (or splice)

SDP: Subscriber Distribution Point

Figure 3: DLL physical model

|                                                                                            | Exchange cable  | Main cable         | Distribution cable  | Installation cable  |

|--------------------------------------------------------------------------------------------|-----------------|--------------------|---------------------|---------------------|

| Wire diameter                                                                              | 0,5; 0,6;       |                    |                     | 0,4; 0,5;           |

| (mm)                                                                                       | 0,32; 0,4       | 0,3 1,4            | 0,3 1,4             | 0,6; 0,8;           |

|                                                                                            |                 |                    |                     | 0,9; 0,63           |

| Structure                                                                                  | SQ (B) or TP    | SQ (B) or TP (L)   | SQ (B) or TP (L)    | SQ or TP or UP      |

|                                                                                            | (L)             |                    |                     |                     |

| Maximum                                                                                    | 1 200           | 2 400 (0,4 mm)     | 600 (0,4 mm)        | 2 (aerial)          |

| number of pairs                                                                            |                 | 4 800 (0,32 mm)    |                     | 600 (in house)      |

| Installation                                                                               |                 | underground        | underground         | aerial (drop)       |

|                                                                                            |                 | in ducts or aerial | or aerial           | in ducts (in house) |

| Capacitance                                                                                | 55 120          | 25 60              | 25 60               | 35 120              |

| (nF/km at 800 Hz                                                                           | )               |                    |                     |                     |

| Wire insulation                                                                            | PVC, FRPE       | PE, paper pulp     | paper, PE, Cell PE  | PE, PVC             |

|                                                                                            |                 |                    |                     |                     |

| TP:                                                                                        | Twisted Pairs   | PE:                | Polyethylene        |                     |

| SQ:                                                                                        | Star Quads      | PVC:               | Polyvinylchloride   | e                   |

| UP:                                                                                        | Untwisted Pairs | Pulp:              | Pulp of paper       |                     |

| L:                                                                                         | Layer           | Cell Pl            | E: Cellular Foam Po | olyethylene         |

| B:                                                                                         | Bundles (units) | FRPE:              | Fire Resistant PE   |                     |

| NOTE: This table is intended to describe the cables presently installed in the local loop. |                 |                    |                     |                     |

Table 1: Cable characteristics

### 5.4 DLL characteristics

The transmitted signal will suffer impairment due to crosstalk, impulsive noise and the non-linear variation with frequency of DLL characteristics.

#### 5.4.1 Principal characteristics

The principal electrical characteristics are:

- insertion loss (X), limited to 36 dB at 40 kHz for the system described in annex A and to 32 dB at 40 kHz for the system described in annex B;

- group delay, limited to 80 µs at 40 kHz;

- characteristic impedance, comprising real and negative imaginary parts, both of which vary non-linearly with frequency.

- NOTE: The main reason for the difference of the value X for the two line systems is the system defined in annex B has a lower output power (peak voltage at output port), which provides lower signal to noise ratio against the adjusted noise level provided at the input port during performance tests.

#### 5.4.2 Crosstalk

Crosstalk noise, in general, is due to finite coupling loss between pairs sharing the same cable, especially those pairs that are physically adjacent. Finite coupling loss between pairs causes a vestige of the signal flowing on one DLL (disturber DLL) to be coupled into an adjacent DLL (disturbed DLL). This vestige is known as crosstalk noise.

Near-End Crosstalk (NEXT) is assumed to be the dominant type of crosstalk.

Intrasystem NEXT or self NEXT results when all pairs interfering with each other in a cable carrying the same digital transmission system.

Intersystem NEXT results when pairs carrying different digital transmission systems interfere with each other. Definition of intersystem NEXT is not part of the present document.

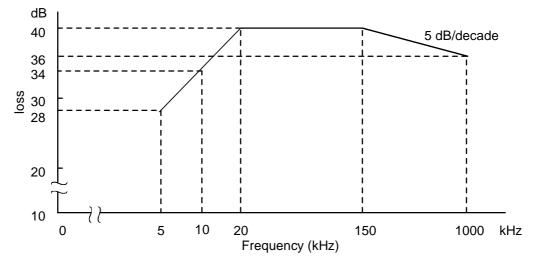

Intrasystem NEXT noise coupled into a disturbed DLL from a number of DLL disturbers is represented as being due to an equivalent single disturber DLL with a coupling loss versus frequency characteristic known as Power Sum Loss (PSL). Its value is 50 dB at 40 kHz and decreases by 15 dB/decade with frequency.

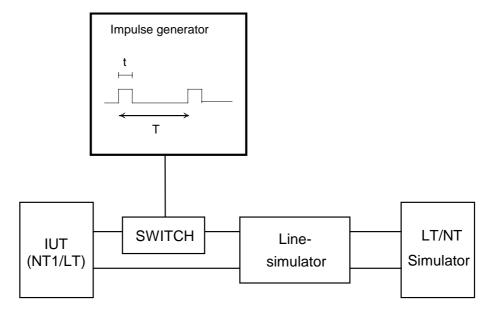

#### 5.4.3 Unbalance about earth

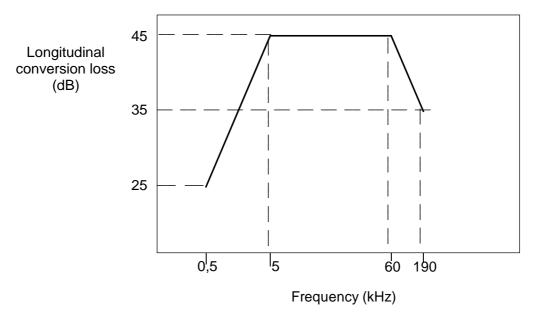

The DLL shall have finite balance about earth. Unbalance about earth is described in terms of Longitudinal Conversion Loss (LCL). Worst case value is 45,5 dB at 40 kHz decreasing with 5 dB/decade with frequency.

#### 5.4.4 Impulse noise

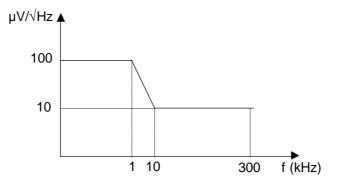

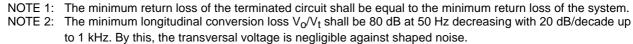

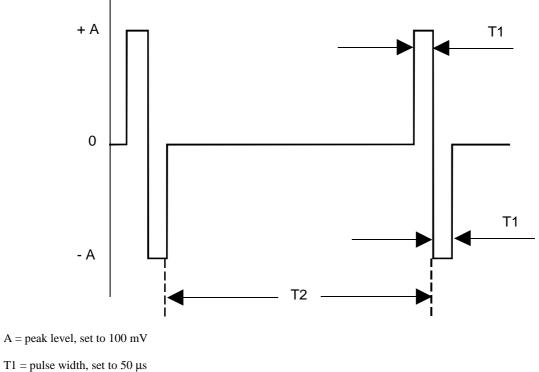

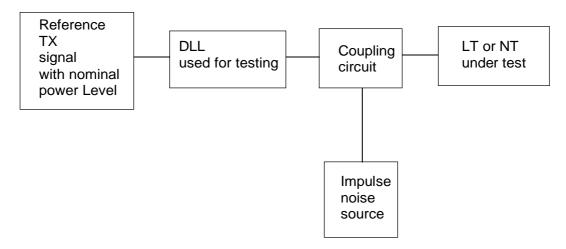

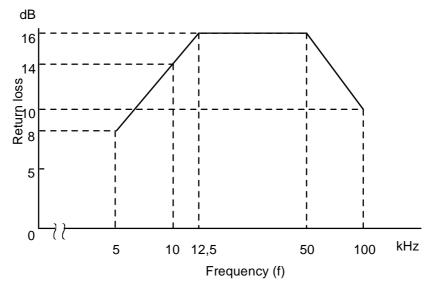

The DLL will have impulse noise resulting from other systems sharing the same cables as well as from other sources. The design-requirement is an impulsive noise corresponding to figure 4.

#### Figure 4: Impulse noise

#### 5.4.5 Micro interruptions

A micro interruption is a temporary line interruption due to external mechanical activity on the copper wires constituting the transmission path, for example, at the cable splice. Splices can be hand made wire to wire junctions, and during cable life oxidation phenomena and mechanical vibrations can induce micro interruptions at these critical points.

The effect of a micro interruption on the transmission system can be a failure of the digital transmission link, together with a failure of the power feeding (if provided) for the duration of the micro interruption.

The objective is that the presence of a micro interruption of specified maximum length shall not deactivate the system, and the system shall activate if it has deactivated due to a longer interruption.

The system shall be able to perform an activation if deactivating after interruptions longer than 10 ms.

# 6 System performance

### 6.1 Performance requirements

Performance limits for the access digital section are specified in ITU-T Recommendation G.821 [10]. The DTS performance shall be such that these performance limits are met. For the purpose of conformance, a DTS is required to meet the specific laboratory performance tests that are defined in the following subclauses.

The defined performance tests cover several aspects:

- the performance of the system, when activated, with several test loops and noise injected;

- to allow reduced test time where appropriate;

- the ability of the system to activate successfully even with a noise injected, which may result in a degraded performance when activated.

For the latter item, the activation time may be greater than the limits defined in ETS 300 297 [4], for those tests where the expected error performance may be below  $10^{-7}$ , but activated status shall be reached in all tests.

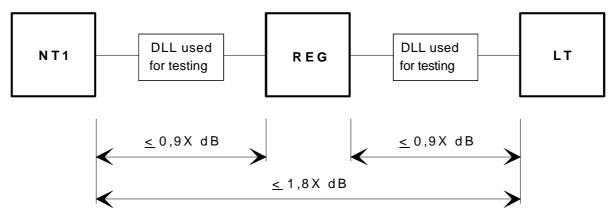

#### 6.1.1 System performance with Regenerators (REGs)

If enhanced transmission range is required then a REG may be inserted between the LT and the NT. The LT - REG - NT combination shall be expected to meet the same BER and latency targets as a normal (non regenerated) link.

The REG may be inserted at any convenient intermediate point in the loop providing that:

- a) the overall insertion loss (X) of the loop without the REG is < 1,8 X dB;

- b) the REG is located within 0,9 X dB of the LT (see figure 5).

There may be further restrictions in the line length due to power feeding.

Figure 5: Access digital section with REG

#### 6.2 Performance measurements

Laboratory performance measurement of a particular digital transmission system requires the following preparations:

- a) definition of a number of DLL models to represent physical and electrical characteristics encountered in local line distribution networks;

- b) simulation of the electrical environment caused by impulsive noise and finite crosstalk coupling loss to other pairs in the same cable;

- c) specification of laboratory performance tests to verify that the performance limits referred to in subclause 6.1 are met.

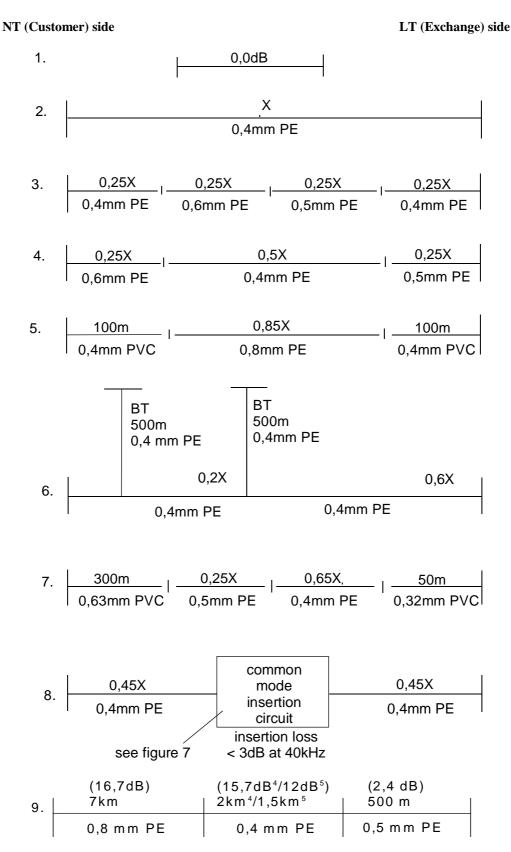

#### 6.2.1 DLL physical models

Some representative models of DLLs (test loops) for evaluating the performance of transceivers for transmission systems are defined in figure 6.

NOTE 1: The value of X (insertion loss) is 36 dB at 40 kHz for the system described in annex A and 32 dB at 40 kHz for the system described in annex B.

NOTE 2: Due to mismatches and BTs, the total DLL attenuation differs from the sum of the attenuation of the parts.

NOTE 3: Attenuation of separate sections is measured with 135  $\Omega$  termination.

NOTE 4: Based on 36 dB overall insertion loss at 40 kHz for the system described in annex A.

NOTE 5: Based on 32 dB overall insertion loss at 40 kHz for the system described in annex B.

#### Figure 6: DLL physical models for laboratory testing

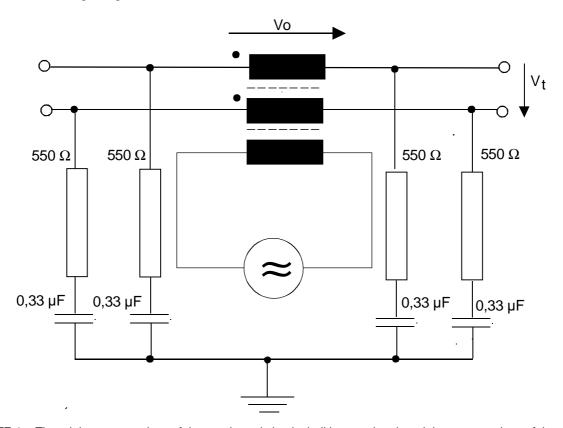

A brief description of the intention of the DLL physical models (shown in figure 6) used for laboratory testing is given:

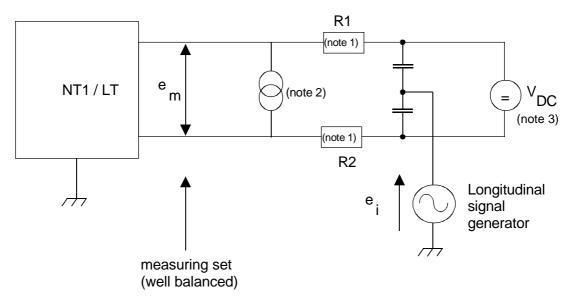

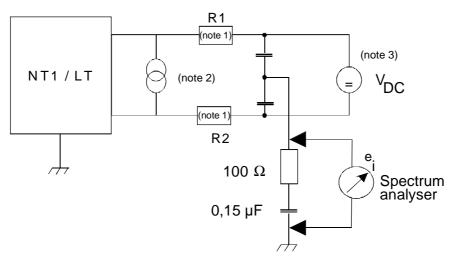

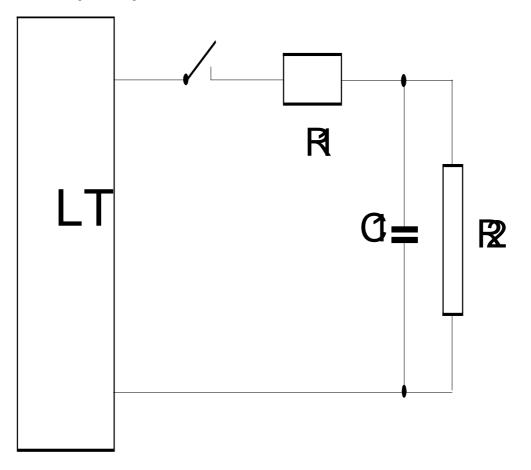

- 1) void;