# ETSI EN 300 420 V1.2.1 (2001-07)

European Standard (Telecommunications series)

Access and Terminals (AT); 2 048 kbit/s digital structured leased lines (D2048S); Terminal equipment interface

Reference REN/AT-020007

Keywords digital, leased line, network, ONP, terminal

### ETSI

#### 650 Route des Lucioles F-06921 Sophia Antipolis Cedex - FRANCE

Tel.: +33 4 92 94 42 00 Fax: +33 4 93 65 47 16

Siret N° 348 623 562 00017 - NAF 742 C Association à but non lucratif enregistrée à la Sous-Préfecture de Grasse (06) N° 7803/88

Important notice

Individual copies of the present document can be downloaded from: http://www.etsi.org

The present document may be made available in more than one electronic version or in print. In any case of existing or perceived difference in contents between such versions, the reference version is the Portable Document Format (PDF). In case of dispute, the reference shall be the printing on ETSI printers of the PDF version kept on a specific network drive within ETSI Secretariat.

Users of the present document should be aware that the document may be subject to revision or change of status. Information on the current status of this and other ETSI documents is available at <a href="http://www.etsi.org/tb/status/">http://www.etsi.org/tb/status/</a>

If you find errors in the present document, send your comment to: editor@etsi.fr

### **Copyright Notification**

No part may be reproduced except as authorized by written permission. The copyright and the foregoing restriction extend to reproduction in all media.

> © European Telecommunications Standards Institute 2001. All rights reserved.

# Contents

| Intelle        | ectual Property Rights                                | 5  |

|----------------|-------------------------------------------------------|----|

| Forew          | /ord                                                  | 5  |

| Introd         | luction                                               | 6  |

| 1              | Scope                                                 | 7  |

|                | References                                            |    |

|                | Definitions and abbreviations                         |    |

| 3.1            | Definitions                                           |    |

| 3.2            | Abbreviations                                         |    |

| 4              |                                                       |    |

|                | Requirements                                          |    |

| 4.1            | Physical characteristics                              |    |

| 4.1.1          | Hardwired connection                                  |    |

| 4.1.2<br>4.2   | Alternative means of connection                       |    |

| 4.2<br>4.2.1   | Electrical characteristics                            |    |

|                | Output port                                           |    |

| 4.2.1.1        | ~-8888                                                |    |

| 4.2.1.2        |                                                       |    |

| 4.2.1.3        | - 1 8                                                 |    |

| 4.2.1.4        | I B                                                   |    |

| 4.2.1.5        | - 1 - 5                                               |    |

| 4.2.1.6        | · · · · · ·                                           |    |

| 4.2.1.7        |                                                       |    |

| 4.2.1.8        | 1                                                     |    |

| 4.2.1.8        |                                                       |    |

| 4.2.1.8        |                                                       |    |

| 4.2.1.8        |                                                       |    |

|                | ű                                                     |    |

| 4.2.2          | Input port                                            |    |

| 4.2.2.1        | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~               |    |

| 4.2.2.2        | 1                                                     |    |

| 4.2.2.3        | 1                                                     |    |

| 4.2.2.4        | 5.0                                                   |    |

| 4.2.2.5        |                                                       |    |

| 4.2.2.6        | I                                                     |    |

| 4.2.2.7        | I J                                                   |    |

| 4.2.2.8        | 1                                                     |    |

| 4.2.2.9        | 1                                                     |    |

| 4.2.2.9        | e                                                     |    |

| 4.2.2.9<br>4.3 | 6                                                     |    |

|                | Safety                                                |    |

| 4.4<br>4.5     | Over voltage<br>ElectroMagnetic Compatibility (EMC)   |    |

| 4.3            |                                                       |    |

| Annex          | x A (normative): Test methods                         | 18 |

| A.1            | General                                               | 18 |

| A.1.1          | Additional information to support the test            |    |

| A.1.2          | Equipment connection                                  |    |

|                |                                                       |    |

| A.2            | Test methods                                          |    |

| A.2.1          | Signal coding at the output port                      |    |

| A.2.2          | Waveform shape at output port                         |    |

| A.2.3          | Output timing                                         |    |

| A.2.4          | Return loss at input port                             |    |

| A.2.5          | Input loss tolerance and immunity against reflections |    |

| A.2.6 Tolerable longitudii            | nal voltage, HDB3 input coding                         |    |

|---------------------------------------|--------------------------------------------------------|----|

| A.2.7 Impedance towards ground        |                                                        |    |

|                                       | ter                                                    |    |

|                                       |                                                        |    |

|                                       | and CRC-4 generation                                   |    |

|                                       | sing the E-bits<br>the E-bits to indicate errored SMFs |    |

|                                       |                                                        |    |

|                                       | 'e                                                     |    |

| 1                                     | t                                                      |    |

|                                       | nment                                                  |    |

| Annex B (normative):                  | Definition of HDB3 code                                | 27 |

| · · · · · ·                           |                                                        |    |

| B.1 General                           |                                                        |    |

| B.2 Definition                        |                                                        |    |

| Annex C (normative):                  | Definition of frame structure                          |    |

| C.1 Frame structure                   |                                                        |    |

| C.2 CRC-4                             |                                                        | 33 |

|                                       |                                                        |    |

| e                                     |                                                        |    |

| Annex D (normative):                  | Requirements Table (RT)                                |    |

| Annex E (informative):                | Timing synchronization                                 |    |

| E.1 General                           |                                                        | 37 |

|                                       |                                                        |    |

| •                                     |                                                        |    |

| E.2 Further information               |                                                        |    |

| Annex F (informative):                | Bibliography                                           |    |

| · · · · · · · · · · · · · · · · · · · |                                                        |    |

| History                               |                                                        |    |

# Intellectual Property Rights

IPRs essential or potentially essential to the present document may have been declared to ETSI. The information pertaining to these essential IPRs, if any, is publicly available for **ETSI members and non-members**, and can be found in ETSI SR 000 314: "Intellectual Property Rights (IPRs); Essential, or potentially Essential, IPRs notified to ETSI in respect of ETSI standards", which is available from the ETSI Secretariat. Latest updates are available on the ETSI Web server (http://www.etsi.org/ipr).

Pursuant to the ETSI IPR Policy, no investigation, including IPR searches, has been carried out by ETSI. No guarantee can be given as to the existence of other IPRs not referenced in ETSI SR 000 314 (or the updates on the ETSI Web server) which are, or may be, or may become, essential to the present document.

# Foreword

This European Standard (Telecommunications series) has been produced by ETSI Technical Committee Access and Terminals (AT).

The present document results from a mandate from the Commission of the European Community (CEC) to provide standards for the support of the Directive on Open Network Provision (ONP) of leased lines (92/44/EEC).

There are two other standards directly related to the present document:

- EN 300 418: "Access and Terminals (AT); 2 048 kbit/s digital unstructured and structured leased lines (D2048U and D2048S); Network interface presentation";

- EN 300 419: "Access and Terminals (AT); 2 048 kbit/s digital structured leased lines (D2048S); Connection characteristics".

The present document is based on information from ITU-T Recommendations and ETSI publications and the relevant documents are quoted where appropriate.

| National transposition dates                                                              |                   |  |  |

|-------------------------------------------------------------------------------------------|-------------------|--|--|

| Date of adoption of this EN:                                                              | 29 June 2001      |  |  |

| Date of latest announcement of this EN (doa):                                             | 30 September 2001 |  |  |

| Date of latest publication of new National Standard<br>or endorsement of this EN (dop/e): | 31 March 2002     |  |  |

| Date of withdrawal of any conflicting National Standard (dow):                            | 31 March 2002     |  |  |

# Introduction

The Council Directive on the application of ONP to leased lines (92/44/EEC) concerns the harmonization of conditions for open and efficient access to, and use of, the leased lines provided over public telecommunications networks, and the availability throughout the European Union (EU) of a minimum set of leased lines with harmonized technical characteristics.

The consequence of the Directive is that telecommunications organizations within the EU shall make available a set of leased lines between points in these countries with specified connection characteristics and specified interfaces.

Two categories (voluntary and regulatory) of standard were used for the interfaces of terminal equipment designed for connection to the ONP leased lines. Technical Basis for Regulations (TBRs) gave the earlier essential requirements under the Directive 91/263/EEC, later replaced by 98/13/EC, for attachment to the leased lines, whereas other voluntary standards (ETSs or ENs) gave the full technical specifications for these interfaces. This document, which is based on an earlier ETS, belongs to the second category.

The requirements of TBR 13 are a subset of the present document.

The present version of the present document has been produced to introduce some necessary changes.

ETS 300 166 and ITU-T Recommendations G.703 [1], G.704 [2] and G.706 were used as the basis for the terminal interface aspects of the present document.

# 1 Scope

The present document specifies the physical and electrical characteristics (except safety, over voltage and EMC aspects), the necessary functional characteristics and the corresponding test principles for a terminal equipment interface for connection to the Network Termination Points (NTPs) of Open Network Provision (ONP) 2 048 kbit/s digital structured leased lines using 120  $\Omega$  interfaces with an information transfer rate of 1 984 kbit/s without restriction on binary content.

The present document is to ensure that the interface of the terminal equipment is compatible with the ONP 2 048 kbit/s digital structured leased line. A terminal equipment interface that conforms to the present document will also be compatible with an ONP 2 048 kbit/s unstructured leased line. The present document is applicable to all interfaces designed for connection to the leased line, however in the cases of apparatus that carries a particular service, of complex apparatus and of apparatus in private networks, other requirements may apply in addition to the present document.

Customer premises wiring and installation between the terminal equipment and the NTP are outside the scope of the present document.

# 2 References

The following documents contain provisions which, through reference in this text, constitute provisions of the present document.

- References are either specific (identified by date of publication and/or edition number or version number) or non-specific.

- For a specific reference, subsequent revisions do not apply.

- For a non-specific reference, the latest version applies.

- [1] ITU-T Recommendation G.703 (1998): "Physical/electrical characteristics of hierarchical digital interfaces".

- [2] ITU-T Recommendation G.704 (1998): "Synchronous frame structures used at 1 544, 6 312, 2 048, 8 448 and 44 736 kbit/s hierarchical levels".

- [3] ITU-T Recommendation O.151 (1992): "Error performance measuring equipment operating at the primary rate and above".

- [4] ITU-T Recommendation O.171 (1997): "Timing jitter and wander measuring equipment for digital systems which are based on the plesiochronous digital hierarchy (PDH)".

- [5] ETSI EN 300 418: " Access and Terminals (AT); 2 048 kbit/s digital unstructured and structured leased lines (D2048U and D2048S); Network interface presentation".

- [6] ETSI EN 300 419: "Access and Terminals (AT); 2 048 kbit/s digital structured leased lines (D2048S); Connection characteristics".

# 3 Definitions and abbreviations

### 3.1 Definitions

For the purposes of the present document, the following terms and definitions apply:

**errored Sub-MultiFrame:** Sub-MultiFrame (SMF) where the calculated Cyclic Redundancy Check-4 bit (CRC-4) does not correspond with the CRC-4 contained within the next SMF (see clause C.2.2)

frame: sequence of 256 bits of which the first 8 bits define the frame structure (see annex C)

**leased lines:** telecommunications facilities provided by a public telecommunications network that provide defined transmission characteristics between NTPs and that do not include switching functions that the user can control, (e.g. on-demand switching)

multiframe: sequence of two SMFs containing the multiframe alignment word (see annex C)

**Network Termination Point (NTP):** physical connections and their technical access specifications which form part of the public telecommunications network and are necessary for access to and efficient communication through that public network

PRBS(2<sup>15</sup>-1): Pseudo Random Bit Sequence (PRBS) (as defined in clause 2.1 of ITU-T Recommendation O.151 [3])

$S_a$  bits: bits 4 to 8 (bits  $S_{a4}$  to  $S_{a8}$ ) in frames not containing the frame alignment signal (see annex C)

Sub-Multiframe (SMF): sequence of 8 frames, each of 256 bits, over which the CRC-4 is calculated (see annex C)

terminal equipment: equipment intended to be connected to the public telecommunications network, i.e.:

- to be connected directly to the termination of a public telecommunication network; or

- to interwork with a public telecommunications network being connected directly or indirectly to the termination of a public telecommunications network,

in order to send, process, or receive information.

### 3.2 Abbreviations

For the purposes of the present document, the following abbreviations apply:

| AIS<br>AMI | Alarm Indication Signal<br>Alternate Mark Inversion                                                    |

|------------|--------------------------------------------------------------------------------------------------------|

| CRC-4      | Cyclic Redundancy Check-4 bit                                                                          |

| D2048S     | 2 048 kbit/s digital structured leased line                                                            |

| dc         | direct current                                                                                         |

| EMC        | ElectroMagnetic Compatibility                                                                          |

| HDB3       | High Density Bipolar code of order 3 (see annex B)                                                     |

| ISDN       | Integrated Services Digital Network                                                                    |

| NTP        | Network Termination Point                                                                              |

| ONP        | Open Network Provision                                                                                 |

| ppm        | parts per million                                                                                      |

| PRBS       | Pseudo Random Bit Sequence                                                                             |

| RAI        | Remote Alarm Indication                                                                                |

| rms        | root mean square                                                                                       |

| RT         | Requirements Table                                                                                     |

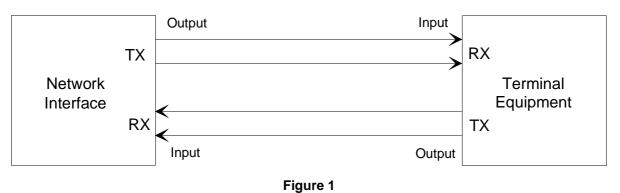

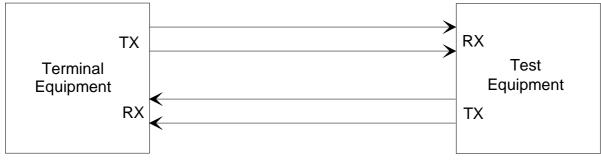

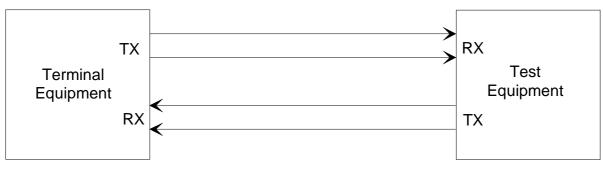

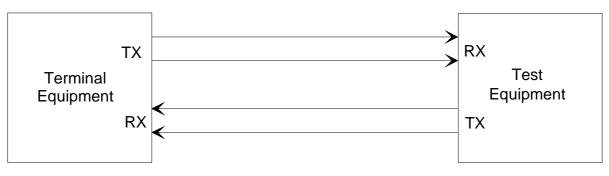

| RX         | RX is a signal input (at either the terminal equipment interface or the test equipment, see figure 1)  |

| SDH        | Synchronous Digital Hierarchy                                                                          |

| SMF        | Sub-MultiFrame                                                                                         |

| ТХ         | TX is a signal output (at either the terminal equipment interface or the test equipment, see figure 1) |

| UI         | Unit Interval                                                                                          |

### 4 Requirements

The terminal equipment interface is for use with 2 048 kbit/s structured leased lines that provide bi-directional, point-to-point digital connections with an information transfer rate of 1 984 kbit/s without restriction on binary content. Any structuring of the data within the transparent 1 984 kbit/s part of the frame is the responsibility of the user.

### 4.1 Physical characteristics

Currently no standardized connector is readily available. Consequently, the only method of connection that can be specified in the present document is the use of solid conductors of 0,4 mm to 0,6 mm. The present document requires the terminal equipment to be capable of presenting either a point for the attachment of unterminated solid conductors, or solid conductors themselves (see clause 4.1.1). It is a requirement that such a connection method be available to be provided for use with the terminal equipment if necessary.

In order to allow connection to be made using other methods (e.g. connectors), the terminal equipment is permitted to be supplied with a connection method suitable for use with those methods (see clause 4.1.2).

- NOTE 1: The following are examples of arrangements that comply with the requirements. The list below should not be regarded as an exhaustive list of all permitted arrangements:

- a) a cord, permanently connected to the terminal equipment at one end and unterminated at the other end, with wires that are solid conductors with diameters in the range 0,4 mm to 0,6 mm;

- b) a cord, connected via a plug and socket to the terminal equipment at one end and unterminated at the other end, with wires that are solid conductors with diameters in the range 0,4 mm to 0,6 mm;

- c) an insulation displacement connector, designed to accept wires with solid conductors with diameters in the range 0,4 mm to 0,6 mm, but with no cord;

- d) a screw connector, designed to accept wires with solid conductors with diameters in the range 0,4 mm to 0,6 mm, but with no cord;

- e) the arrangement in b) plus one or more additional alternative cords with the same plug or socket arrangement at the terminal end and any plug or socket at the other end;

- f) the arrangement in c) or d) plus one or more cords suitable for connection to the terminal equipment at one end and any plug or socket at the other end.

The transmit pair is the output from the terminal equipment interface. The receive pair is the input to the terminal equipment interface, as shown in figure 1. Where the terms "output" and "input" are used without qualification in the present document, they refer to the terminal equipment interface.

NOTE 2: The use of a shielded cord or cable may be necessary to meet radiation and immunity requirements defined in ElectroMagnetic Compatibility (EMC) standards.

### 4.1.1 Hardwired connection

**Requirement:** the terminal equipment shall provide:

- a) a set of connection contacts (e.g. an insulation displacement connector or a screw terminal block) to which solid wire conductors with diameters in the range 0,4 mm to 0,6 mm may be connected; or

- b) a wiring arrangement connected by any means to the terminal equipment, with unterminated solid wire conductors with diameters in the range 0,4 mm to 0,6 mm at the end distant from the terminal equipment.

Test: there is no test. All subsequent tests are carried out via the specified connection method.

### 4.1.2 Alternative means of connection

Any alternative means of connection may be provided in addition to the connection arrangements under clause 4.1.1.

### 4.2 Electrical characteristics

### 4.2.1 Output port

### 4.2.1.1 Signal coding

**Requirement:** the signal transmitted at the output port shall comply with the High Density Bipolar code of order 3 (HDB3) encoding rules (see annex B).

Test: the test shall be conducted according to clause A.2.1.

### 4.2.1.2 Waveform shape

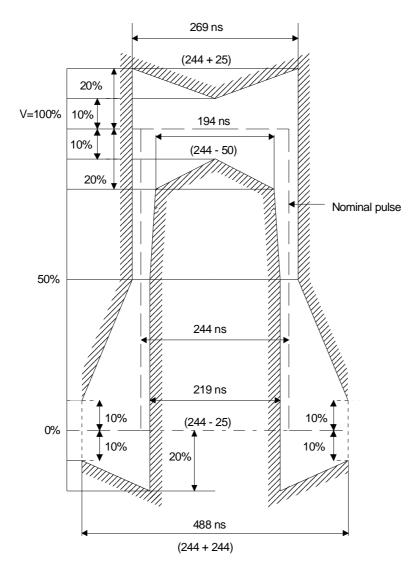

**Requirement:** the pulse at the output port shall comply with the requirements given in table 1 and figure 2, based on ITU-T Recommendation G.703 [1].

| Pulse shape (nominally rectangular)                                                         | All marks of a valid signal shall conform to the mask<br>(see figure 2) irrespective of the polarity. The value V<br>corresponds to the nominal peak voltage of a mark. |

|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Test load impedance                                                                         | 120 $\Omega$ non-reactive                                                                                                                                               |

| Nominal peak voltage V of a mark                                                            | 3 V                                                                                                                                                                     |

| Peak voltage of a space                                                                     | 0 ± 0,3 V                                                                                                                                                               |

| Nominal pulse width                                                                         | 244 ns                                                                                                                                                                  |

| Ratio of the amplitudes of positive and negative pulses at the centre of the pulse interval | 0,95 to 1,05                                                                                                                                                            |

| Ratio of the widths of positive and negative pulses at the nominal half amplitude           | 0,95 to 1,05                                                                                                                                                            |

Figure 2: Pulse mask for 2 048 kbit/s pulse

**Test:** the test shall be conducted according to clause A.2.2.

### 4.2.1.3 Output timing

This requirement is such that the terminal equipment is capable of operating when connected to leased lines capable of carrying user timing within the range 2 048 kbit/s  $\pm$ 50 parts per million (ppm) and when connected to leased lines that provide timing that is synchronous to the network timing. For further information see annex E.

**Requirement:** the terminal equipment shall have:

- a) an internal clock which shall provide a bit rate at the output port within the limits of 2 048 kbit/s ±50 ppm; and

- b) the capability to provide a clock loop such that the signal timing at the output port is derived from the timing at the input port.

The terminal equipment may also have:

c) an external reference signal input from which the output timing may be derived.

**Test:** for case a) the test shall be conducted according to clause A.2.3. The capability to provide a clock loop, case b), and the derivation of a clock signal from an external reference signal input, case c), are covered by the test of clause A.2.8.

### 4.2.1.4 Impedance towards ground

**Requirement:** where the terminal equipment has a ground, the impedance towards ground of the output port shall be greater than  $1\ 000\ \Omega$  for frequencies in the range 10 Hz to 1 MHz when measured with a sinusoidal test voltage of 2 V root mean square (rms). For the purpose of this requirement, ground shall be the terminal equipment common reference point or test reference point.

NOTE: This requirement is included to allow transformerless implementations.

Test: the test shall be conducted according to clause A.2.7.

### 4.2.1.5 Output jitter

**Requirement:** the peak-to-peak output jitter shall not exceed the limits of table 2 when measured with a band pass filter with linear cut-off with the defined cut-off frequencies. At frequencies below the lower 3 dB point, the attenuation of the high pass filter shall rise with a value equal to 20 dB per decade. At frequencies above the upper 3 dB point, the attenuation of the low pass filtration shall rise with a value greater than, or equal to, 60 dB per decade.

For the purpose of testing, any signal input from which the output timing is derived shall be provided with the maximum tolerable input jitter, and with the maximum tolerable input frequency deviation, as specified by the manufacturer.

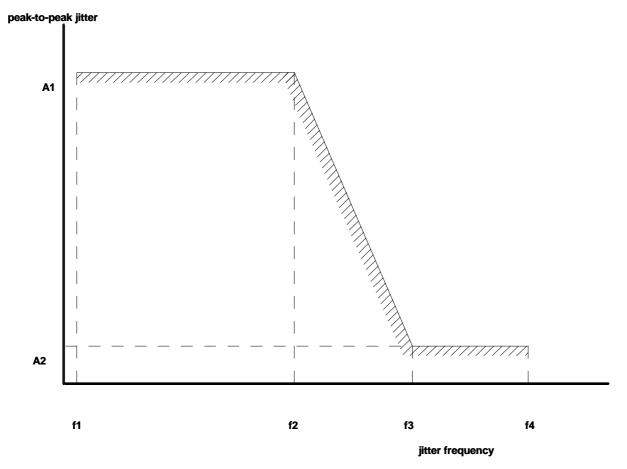

Where the output timing of the terminal equipment is taken from the leased line, the input to the terminal equipment shall be provided with components of sinusoidal jitter at points on the curve of figure 3 and table 4.

NOTE: A separate requirement for output jitter at frequencies below 40 Hz is not required because the measurement filter with a first order lower cut-off will allow the jitter to have a spectrum whose amplitude rises at 20 dB/decade as the frequency reduces below 40 Hz. Where timing is taken from the leased line, the test uses input jitter frequencies from 20 Hz upwards.

### Table 2: Maximum output jitter

| Measurement filter bandwidth |               | Output jitter                   |

|------------------------------|---------------|---------------------------------|

| Lower cut-off                | Upper cut-off | Unit Interval (UI) peak-to-peak |

| (high pass)                  | (low pass)    | (maximum)                       |

| 40 Hz                        | 100 kHz       | 0,11 UI                         |

Test: the test shall be conducted according to clause A.2.8.

### 4.2.1.6 Output return loss

There are no requirements for output return loss under the present document.

NOTE: A requirement for output return loss may be added to the present document when appropriate specifications become available.

### 4.2.1.7 Output signal balance

There are no requirements for output signal balance under the present document.

NOTE: The effects of the output signal imbalance are covered under the EMC Directive (89/336/EEC).

### 4.2.1.8 Output structure

**Requirement:** the bit stream transmitted at the output of the terminal equipment shall be structured as defined in clause C.1.

Test: the test shall be conducted according to clause A.2.9.1.

### 4.2.1.8.1 CRC-4

**Requirement:** the CRC-4 bits transmitted at the output of the terminal equipment shall be as defined in tables C.1 and C.2 and clause C.2.1 of annex C and shall correspond to the data transmitted at the output of the terminal equipment.

**Test:** the test shall be conducted according to clause A.2.9.1.

### 4.2.1.8.2 Use of the E-bits

The terminal equipment shall comply either with clause 4.2.1.8.2.1 or clause 4.2.1.8.2.2.

4.2.1.8.2.1 Terminals not using the E-bits

This clause is applicable to those terminal equipments which do not use the E-bits to indicate errored SMFs.

**Requirement:** both E-bits transmitted at the output of the terminal equipment shall be set to binary ONE in all instances.

**Test:** the test shall be conducted according to clause A.2.9.2.

#### 4.2.1.8.2.2 Terminals using the E-bits to indicate errored SMFs

This clause is applicable to those terminal equipments which use the E-bits to indicate errored SMFs.

**Requirement:** the E-bits transmitted at the output of the terminal equipment shall indicate errored SMFs in the input bit stream. One E-bit in a multiframe shall be set to binary ZERO for each errored SMF received in the input bit stream. The E-bits corresponding to non-errored SMFs shall be set to binary ONE. Any delay between the detection of an errored SMF and the setting of the E-bit that indicates the errored SMF shall be less than 1 second.

Test: the test shall be conducted according to clause A.2.9.3.

### 4.2.1.8.3 Use of the A-bit

The terminal equipment shall comply either with clause 4.2.1.8.3.1 or clause 4.2.1.8.3.2.

#### 4.2.1.8.3.1 Terminals not using the A-bit

**Requirement:** the A-bit transmitted at the output of the terminal equipment shall be set to binary ZERO in all instances.

**Test:** the test shall be conducted according to clause A.2.9.4.

#### 4.2.1.8.3.2 Terminals using the A-bit

**Requirement:** the A-bit transmitted at the output of the terminal equipment shall be set to binary ZERO in normal operation but may be changed from binary ZERO to binary ONE within 30 ms of any of the following conditions occurring in the input bit stream:

- a) three consecutive incorrect frame alignment signals, (the correct frame alignment signal is defined in table C.1);

- b) there being = 915 errored SMFs out of 1 000 SMFs.

The terminal may also change the A-bit from binary ZERO to binary ONE within 30 ms of:

c) bit 2 in frames not containing the frame alignment signal being in error (i.e. bit 2 is a binary ZERO) on three consecutive occasions.

For a terminal equipment recovering from loss of frame alignment (i.e. the A-bit set to binary ONE) the A-bit transmitted at the output of the terminal equipment shall be set from binary ONE to binary ZERO within 30 ms of any of the following conditions occurring in the input bit stream:

14

- d) for the first time, the presence of the correct frame alignment signal (as defined in table C.1); and

- e) the absence of the frame alignment signal in the following frame detected by verifying that bit 2 of the basic frame is a binary ONE; and

- f) for the second time, the presence of the correct frame alignment signal in the next frame.

Test: the test shall be conducted according to clause A.2.9.4.

### 4.2.1.8.4 Use of the S<sub>a</sub> bits

There is no requirement on the value or setting of the S<sub>a</sub> bits at the output of the terminal equipment.

### 4.2.2 Input port

### 4.2.2.1 Signal coding

**Requirement:** the input port shall decode without error HDB3 encoded signals in accordance with HDB3 encoding rules (see annex B).

Test: the test shall be conducted according to clause A.2.6.

### 4.2.2.2 Input return loss

**Requirement:** the input return loss with respect to  $120 \Omega$  at the interface shall be greater than or equal to the values given in table 3, which is taken from clause 9.3 of ITU-T Recommendation G.703 [1].

### Table 3: Input port minimum return loss

| Frequency range        | Return loss |

|------------------------|-------------|

| 51 kHz to 102 kHz      | 12 dB       |

| 102 kHz to 2 048 kHz   | 18 dB       |

| 2 048 kHz to 3 072 kHz | 14 dB       |

Test: the test shall be conducted according to clause A.2.4.

### 4.2.2.3 Input loss tolerance

**Requirement:** the input port shall decode without errors a 2 048 kbit/s signal as defined in clauses 4.2.1.1 and 4.2.1.2 above but modified by a cable or artificial cable with the following characteristics:

- a) attenuation that follows a <sup>1</sup>f law with values throughout the range 0 to 6 dB at 1 024 kHz; and

- b) characteristic impedance of 120  $\Omega$  with a tolerance of  $\pm 20$  % in the frequency range from 200 kHz up to, but not including, 1 MHz, and  $\pm 10$  % at 1 MHz.

Test: the test shall be according to clause A.2.5.

### 4.2.2.4 Immunity against reflections

**Requirement:** when a signal comprising a combination of a normal signal and an interfering signal is applied to the input port, via an artificial cable with a loss in the range 0 dB to 6 dB at 1 MHz, no errors shall result due to the interfering signal.

The normal signal shall be a signal encoded according to HDB3, shaped according to the mask of figure 2, with a binary content in accordance with a PRBS $(2^{15}-1)$ .

The interfering signal shall be the same as the normal signal except that the level is attenuated by 18 dB, the bit rate is within 2 048 kbit/s  $\pm$ 50 ppm and the timing shall not be synchronized to the normal signal.

**Test:** the test shall be conducted according to clause A.2.5.

### 4.2.2.5 Tolerable longitudinal voltages

**Requirement:** the receiver shall operate without errors with any input signal in the presence of a longitudinal voltage of magnitude 2 V rms over the frequency range 10 Hz to 30 MHz.

NOTE: This requirement is included to allow transformerless implementations.

**Test:** the test shall be conducted according to clause A.2.6.

### 4.2.2.6 Impedance towards ground

**Requirement:** where the terminal equipment has a ground, the impedance towards ground of the input port shall be greater than  $1\ 000\ \Omega$  for frequencies in the range 10 Hz to 1 MHz when measured with a sinusoidal test voltage of 2 V rms. For the purpose of this requirement, ground shall be the terminal equipment common reference point or test reference point.

NOTE: This requirement is included to allow transformerless implementations.

**Test:** the test shall be conducted according to clause A.2.7.

### 4.2.2.7 Input jitter tolerance

**Requirement:** the terminal equipment shall tolerate at its input port the maximum input jitter as shown in table 4 and figure 3.

NOTE: Terminal equipment with more than one input will normally need to be designed with a wander buffer of at least 18 µs, however, to accommodate the wander that may be produced by Synchronous Digital Hierarchy (SDH) networks, up to 40 µs may be needed.

#### Table 4: Input jitter tolerance

| Peak-to-peak amplitude (UI) |     |    | Frequency | (Hz)   |         |

|-----------------------------|-----|----|-----------|--------|---------|

| A1                          | A2  | f1 | f2        | f3     | f4      |

| 1,5                         | 0,2 | 20 | 2 400     | 18 000 | 100 000 |

Figure 3: Input jitter tolerance

**Test:** the test shall be conducted according to clause A.2.8.

### 4.2.2.8 Input clock tolerance

**Requirement:** the terminal equipment shall decode without error HDB3 encoded signals over the frequency range 2 048 kbit/s ±50 ppm.

Test: the test shall be conducted in accordance with clause A.2.8.

### 4.2.2.9 Input frame structure

### 4.2.2.9.1 Frame alignment

**Requirement:** the input port shall accept an input bit stream with a frame and multiframe structure as defined in annex C. The terminal equipment shall be capable of achieving frame alignment in order to separate the user data from the frame information.

Frame alignment shall be achieved following:

- a) for the first time, the presence of the correct frame alignment signal; and

- b) the absence of the frame alignment signal in the following frame detected by verifying that bit 2 of the basic frame is a binary ONE; and

- c) for the second time, the presence of the correct frame alignment signal in the next frame, provided that the data does not contain any simulated frame alignment words.

The terminal equipment shall continue to maintain frame alignment in the event of receiving one or two consecutive incorrect frame alignment signals. On receipt of three consecutive incorrect frame alignment signals the terminal equipment shall consider frame alignment to have been lost and initiate a search for frame alignment.

Frame alignment may also be considered to have been lost following:

- d) the occurrence of = 915 errored SMFs out of 1 000 SMFs; or

- e) bit 2 in frames not containing the frame alignment signal being in error on three consecutive occasions; or

- f) the inability to achieve multiframe alignment within 8 ms (see clause 4.2.2.9.2).

Test: the test shall be conducted in accordance with clause A.2.10.1.

### 4.2.2.9.2 Multiframe alignment

This requirement is optional and applies only to those terminal equipments needing to obtain multiframe alignment in order to extract CRC-4 information in order to comply with clause 4.2.1.8.2.2.

**Requirement:** CRC-4 multiframe alignment shall be achieved if at least two valid CRC-4 multiframe alignment signals can be located within 8 ms (the time separating two CRC-4 multiframe alignment signals being 2 ms or a multiple of 2 ms). If multiframe alignment cannot be achieved within 8 ms it shall be assumed that frame alignment is due to a spurious frame alignment signal and a research for frame alignment shall be initiated.

NOTE: The research for frame alignment should be started at a point just after the location of the assumed spurious frame alignment signal. This will usually avoid realignment onto the spurious frame alignment signal.

Test: the test shall be conducted in accordance with clause A.2.10.2.

### 4.3 Safety

Requirements for safety are outside the scope of the present document.

Safety standards are published by CENELEC.

- NOTE 1: An example of such a CENELEC product safety standard is EN 60950 (see annex F).

- NOTE 2: For safety categories of interfaces, see EG 201 212. This document is also available from CENELEC as ROBT-002.

- NOTE 3: Designers should take into account the minimum impedance towards ground specified in the present document.

### 4.4 Over voltage

Over voltage aspects are outside of the scope of the present document.

### 4.5 ElectroMagnetic Compatibility (EMC)

EMC requirements are outside the scope of the present document.

# Annex A (normative): Test methods

# A.1 General

This annex describes the test principles to determine the compliance of a terminal equipment against the requirements of the present document.

18

It is outside the scope of the present document to identify the specific details of the implementation of the tests.

A terminal equipment may be designed for through-connecting and may fulfil the electrical requirements only if through-connected. In these cases the requirements of the present document are valid and the tests shall be carried out with the through-connection terminated as specified by the manufacturer.

Details of test equipment accuracy and the specification tolerance of the test devices are not included in all cases. Where such details are provided they shall be complied with, but the way they are expressed shall not constrain the method of implementing the test.

NOTE: Attention is drawn to the issue of measurement uncertainty which may be addressed in future documents. Not all the required test results make allowance for spurious events during testing (e.g. errors due to EMC effects), which may make it necessary to repeat a test.

The test configurations given do not imply a specific realization of test equipment or test arrangement, or the use of specific test devices for conformance testing. However, any test configuration used shall provide those test conditions specified under "interface state", "stimulus" and "monitor" for each individual test.

The test equipment shall be a device, or a group of devices, that is capable of generating a stimulus signal conforming to the present document and capable of monitoring the signal received from the interface.

### A.1.1 Additional information to support the test

The following facilities shall be provided by the terminal equipment interface under test:

- a) an ability to configure the terminal equipment such that it provides a transparent loopback of the input to the output; and

- b) an ability to transmit a given bit pattern, e.g. PRBS(2<sup>15</sup>-1), within the 1 984 kbit/s user channel.

Where a) or b) cannot be provided, the terminal equipment supplier shall provide an alternative means of performing the test.

NOTE: Where terminals equipments use the E-bits to indicate errored SMFs, this may be used as an alternative to a transparent loopback in order to determine if data at the input has been correctly received.

### A.1.2 Equipment connection

The tests in the present document shall be carried out using the connection method suitable for use with unterminated solid conductors as defined in clause 4.1.1. However, in the case of the tests specified in clauses A.2.2, A.2.4 and A.2.7, an alternative method of connection may be provided by the terminal equipment supplier for test purposes. In this case, this method of connection shall be used for these tests because the requirement considers any wiring to be part of the installation cabling.

NOTE: This alternative method of connection is for test purposes only and has been introduced because the characteristics tested in clauses A.2.2, A.2.4 and A.2.7 are based on ITU-T Recommendation G.703 [1] which makes no allowance for additional wiring. This alternative method may not be the same as the alternative method of connection referred to in clause 4.1 which is for operational use.

# A.2 Test methods

One test may cover more than one requirement. The scope of each test is defined under the heading "purpose".

### A.2.1 Signal coding at the output port

**Purpose:** to verify that the signal coding at the terminal equipment output port complies with the HDB3 coding rules as required by clause 4.2.1.1.

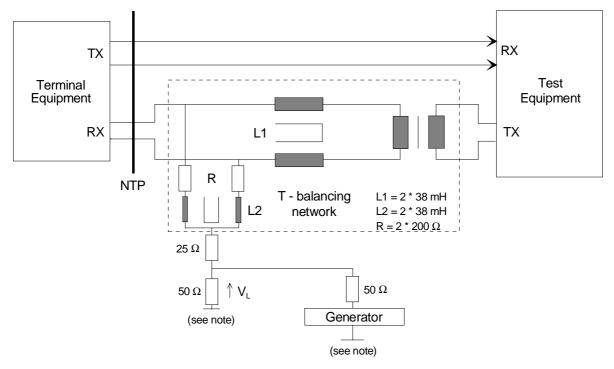

### **Test configuration (see figure A.1):**

### Interface state: powered.

**Stimulus:** the terminal equipment shall transmit a HDB3 bit stream according to the frame structure of annex C. The binary content of the data contained in bits 9 to 256 of the frame shall be a bit stream including the sequences <0000><even number of binary ONEs><0000> and <0000><odd number of binary ONEs><0000>, where 0 = space and 1 = mark input to the HDB3 encoder, (see note).

**Monitor:** the output bit stream for a test period of sufficient time to allow transmission of 100 occurrences of the above patterns plus the latency period of the error detection mechanism.

**Results:** there shall be no errors in the decoded bit stream.

NOTE: A pseudo random bit stream, e.g. PRBS(2<sup>15</sup>-1), will be acceptable if the bit patterns of the above clause are included in the bit stream.

### A.2.2 Waveform shape at output port

Purpose: to verify conformance of the output waveform shape with the requirements of clause 4.2.1.2.

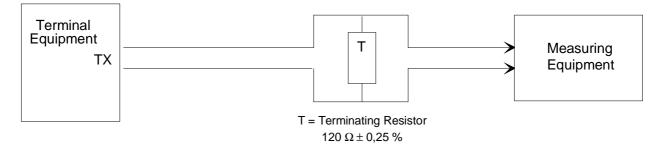

### Test configuration (see figure A.2):

Figure A.2: Waveform shape at output port

#### Interface state: powered.

#### Stimulus: undefined.

#### Monitor:

- marks and spaces transmitted by the terminal equipment, measuring the amplitude and shape of positive and negative pulses (measured at the centre of the pulse interval) and the time duration of positive and negative pulses (measured at the nominal half of the pulse amplitude, i.e. 1,5 V);

- the overall measurement accuracy shall be better than 90 mV. All the measurements shall be performed using measuring equipment capable of recording direct current (dc). A bandwidth of 200 MHz or greater shall be used to ensure the capture of over or undershoot of the pulse.

#### **Results:**

- both positive and negative pulses shall be within the mask of figure 2, where V = 100 % shall be 3 V;

- the bit interval corresponding to a space shall not present voltages higher than  $\pm 0.3$  V;

- the ratio between the amplitude of positive and negative pulses shall be contained in the range from 0,95 to 1,05;

- the ratio between the pulse widths of positive and negative pulses shall be in the range from 0,95 to 1,05.

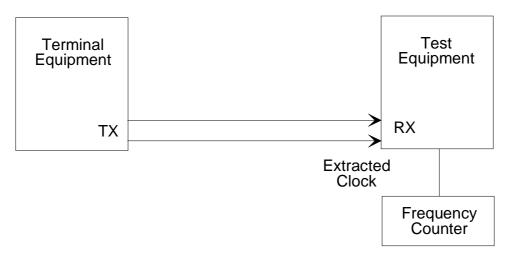

### A.2.3 Output timing

**Purpose:** to verify the bit rate is within the limits of 2 048 kbit/s  $\pm$ 50 ppm when the terminal equipment is generating timing from an internal clock, clause 4.2.1.3.

#### **Test configuration (see figure A.3):**

- the terminal equipment shall be configured to provide output timing from the internal clock source. The terminal equipment output shall be any HDB3 encoded bit stream.

Figure A.3: Output timing

Interface State: powered.

Stimulus: undefined.

Monitor: the bit rate from the terminal equipment output port.

**Results:** the bit rate shall be within the limits of 2 048 kbit/s  $\pm$ 50 ppm.

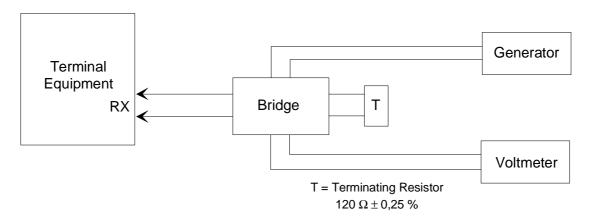

### A.2.4 Return loss at input port

**Purpose:** to verify that the return loss of the receive pair of the terminal equipment interface complies with the requirements of clause 4.2.2.2.

### Test configuration (see figure A.4):

Figure A.4: Return loss at input port

#### Interface state: powered.

**Stimulus:** sinusoidal signal of 3 V peak at the input to the terminal equipment with a frequency variable between 51 kHz and 3 072 kHz.

**Monitor:** voltage measured across the bridge, representing a terminating resistor of 120  $\Omega$ , using a selective voltmeter with a bandwidth of less than 1 kHz.

**Results:** the measured return loss shall be greater than or equal to the values in table 3 of clause 4.2.2.2.

NOTE: The characteristics of the generator and of the voltmeter may be different depending on the implementation of the bridge, however, the total error of the test set-up should be less than 0,5 dB in the range between 10 dB and 20 dB. When connected to a  $120 \Omega \pm 0,25 \%$  resistor the measured return loss of the bridge should be 20 dB higher than the limits specified for the interface.

### A.2.5 Input loss tolerance and immunity against reflections

**Purpose:** to check the input port immunity against an interfering signal combined with the input signal, as specified in clause 4.2.2.4, both without cable (i.e. 0 dB attenuation loss) and with a cable attenuation of 6 dB, as specified in clause 4.2.2.3.

### Test configuration (see figure A.5):

- the interfering signal shall be combined with the main signal in a combining network of impedance  $120 \Omega$ , with zero dB loss in the main path and an attenuation in the interference path of 18 dB;

- the cable simulator shall have an attenuation of 6 dB measured at 1 024 kHz and an attenuation characteristic that follows a <sup>1</sup>f law over the frequency range 100 kHz to 10 MHz;

- the conformance of the interface shall be verified in the following test conditions:

- a) without cable simulator and without interfering signal; and

- b) with cable simulator and without interfering signal; and

- c) without cable simulator and with interfering signal; and

- d) with cable simulator and with interfering signal.

- the test shall be repeated with the wires at the terminal equipment interface input (RX) reversed.

### Figure A.5: Immunity against reflections

Interface state: powered, with received data looped back to the output port.

### Stimulus:

- the output signal of the test equipment shall be HDB3 encoded and conform to a pulse shape as defined in figure 15 of ITU-T Recommendation G.703 [1], which is reproduced in figure 2 of the present document. The bit stream shall be structured into frames, with the CRC-4, according to ITU-T Recommendation G.704 [2]. Within the frames not containing the frame alignment signal, bit 3 (Remote Alarm Indication (RAI)) shall be set to 0 and bits 4 to 8 ( $S_{a4}$  to  $S_{a8}$ ) shall be set to 1. The binary content of the data contained in bits 9 to 256 of the frame shall be a PRBS(2<sup>15</sup>-1). The bit rate shall be within the limits 2 048 kbit/s ±50 ppm;

- the interfering signal from the pattern generator shall:

- a) be HDB3 encoded and conform to a pulse shape as defined in figure 15 of ITU-T Recommendation G.703 [1], which is reproduced in figure 2 of the present document; and

- b) have a binary content with a  $PRBS(2^{15}-1)$ ; and

- c) have a bit rate within the limits 2 048 kbit/s ±50 ppm, not synchronized to the output signal of the test equipment.

Monitor: data at output port of the terminal equipment.

**Results:** verify that the data received from the equipment under test is identical with the generated sequence for a period of at least one minute.

### A.2.6 Tolerable longitudinal voltage, HDB3 input coding

**Purpose:** to check minimum tolerance to longitudinal voltages at the input of the terminal equipment, as specified in clause 4.2.2.5, and correct recognition of HDB3 code, as specified in clause 4.2.2.1.

### **Test configuration (see figure A.6):**

NOTE: This point shall be connected to the terminal equipment common reference point or to the equipment test reference point.

### Figure A.6: Tolerable longitudinal voltage and HDB3 input coding

Interface state: powered, with received data looped back to the output port of the terminal equipment.

#### Stimulus:

- the output signal of the test equipment shall be HDB3 encoded and conform to a pulse shape as defined in figure 15 of ITU-T Recommendation G.703 [1], which is reproduced in figure 2 of the present document. The bit stream shall be structured into frames, with the CRC-4, according to ITU-T Recommendation G.704 [2]. Within the frames not containing the frame alignment signal, bit 3 (RAI) shall be set to 0 and bits 4 to 8 ( $S_{a4}$  to  $S_{a8}$ ) shall be set to 1. The binary content of the data contained in bits 9 to 256 of the frame shall be a PRBS(2<sup>15</sup>-1);

- a longitudinal voltage V<sub>L</sub> of 2 V rms, ±20 mV with a frequency variable between 10 Hz and 30 MHz shall be applied for a minimum of 2 seconds.

Monitor: data at output port of the terminal equipment.

**Results:** verify that the data received from the equipment under test is identical with the generated sequence.

NOTE: The inherent longitudinal conversion loss of the T-balancing network should be greater than 30 dB.

### A.2.7 Impedance towards ground

**Purpose:** to check terminal equipment input and output ports impedance towards ground, as specified in clauses 4.2.1.4 and 4.2.2.6.

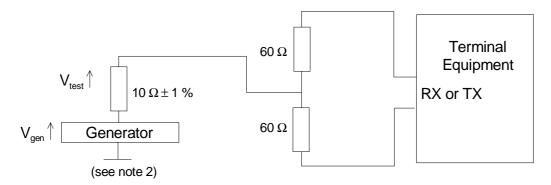

**Test configuration (see figure A.7):**

- NOTE 1: The 60  $\Omega$  resistors should be within 1 % and matched to better than 0,1 %.

- NOTE 2: This point shall be connected to the terminal equipment common reference point or to the equipment test reference point.

#### Figure A.7: Impedance towards ground

Interface state: powered.

**Stimulus:** sinusoidal test signal ( $V_{oen}$ ) of 2 V rms, ±20 mV applied over the frequency range 10 Hz to 1 MHz.

Monitor: voltage of V<sub>test</sub>.

**Results:** voltage V<sub>test</sub> shall be less than 19,2 mV rms.

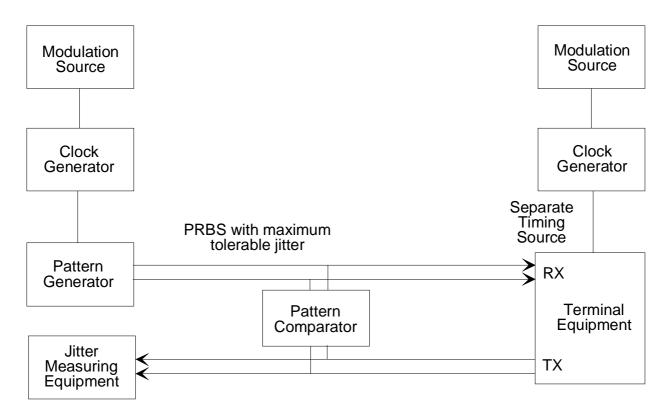

### A.2.8 Input and output jitter

**Purpose:** this test is used to measure tolerance to input jitter (clause 4.2.2.7), maximum output jitter (clause 4.2.1.5) and operation over the specified timing input range (clause 4.2.2.8).

NOTE: Further information on the measurement of jitter can be found in ITU-T Supplement number 3.8, Fascicle IV.4 (1988).

#### **Test Configuration (see figure A.8):**

- the terminal equipment shall be tested in each of the following configurations (where these modes of operation are supported):

- a) output timing referenced to the internal clock; and

- b) output timing referenced to any external clock source from which timing can be derived (including derivation from the input signal).

### Figure A.8: Jitter measurement

Interface state: powered, with received data looped back to the output port.

### Stimulus:

- the output signal of the pattern generator shall be HDB3 encoded and conform to a pulse shape as defined in figure 15 of ITU-T Recommendation G.703 [1], which is reproduced in figure 2 of the present document. The bit stream shall be structured into frames, with the CRC-4, according to ITU-T Recommendation G.704 [2]. Within the frames not containing the frame alignment signal, bit 3 (RAI) shall be set to 0 and bits 4 to 8 (S<sub>a4</sub> to S<sub>a8</sub>) shall be set

- to 1. The binary content of the data contained in bits 9 to 256 of the frame shall be a  $PRBS(2^{15}-1)$ ;

- measurements shall be made with both the input signals at the digital rate limits and between these limits, sufficient to verify jitter compliance over the specified frequency range. As a minimum the test shall be performed at the upper and lower limits and at the nominal rate;

- the modulation source for the terminal equipment input bit stream shall generate individual components of sinusoidal jitter at points on the curve of figure 3 and table 4;

- the modulation source for the external timing (if needed) shall be independent from that for the input signal and shall generate the maximum tolerable jitter, and maximum frequency deviation, as specified by the manufacturer of the terminal equipment;

- it may be necessary to synchronize the two clock generators to avoid a high occurrence of slips.

#### Monitor:

- a) the signal transmitted by the terminal equipment; and

- b) the jitter extracted from this signal, using equipment complying with ITU-T Recommendation O.171 [4], with defined cut-off frequencies as shown in table 2 of the present document.

- a) there shall be no bit errors reported by the test equipment within the period of the test; and

- b) the peak-to-peak jitter shall comply with table 2 when measured with linear filters with the defined cut-off frequencies.

- NOTE: The modulation source may be included in the clock generator and/or the pattern generator, or it may be provided separately.

### A.2.9 Frame structure

### A.2.9.1 Output structure and CRC-4 generation

**Purpose:** to test the correct output structure (clause 4.2.1.8) and CRC-4 generation (clause 4.2.1.8.1) at the terminal equipment output port.

### Test configuration (see figure A.9):

Figure A.9: Frame structure

### Interface state: powered.

### Stimulus:

- the output signal of the test equipment shall be HDB3 encoded and conform to a pulse shape as defined in figure 15 of ITU-T Recommendation G.703 [1], which is reproduced in figure 2 of the present document, and a framing structure as defined in ITU-T Recommendation G.704 [2];

- the terminal equipment shall transmit a HDB3 bit stream with a binary content that has a frame structure according to annex C of the present document. The binary content of the data contained in bits 9 to 256 of the frame shall be a pseudo random bit stream, e.g. PRBS(2<sup>15</sup>-1).

Monitor: the frame alignment signal and CRC-4 in the output bit stream from the terminal equipment.

### **Results:**

- the frame alignment signal and bit 2 of the frame not containing the frame alignment signal shall be as defined in table C.1;

- the CRC-4 shall correspond with the data in the previous SMF, as defined in clause C.2 and clause C.2.1.

### A.2.9.2 Terminals not using the E-bits

**Purpose:** to verify that for terminal equipments not using the E-bit to indicate SMF errors, the E-bits are set to binary ONE, as specified in clause 4.2.1.8.2.1.

### **Test configuration (see figure A.9):**

#### Interface state: powered.

#### Stimulus:

- the terminal equipment shall transmit a HDB3 bit stream according to the frame structure of annex C. The binary content of the data contained in bits 9 to 256 of the frame shall be a pseudo random bit stream, e.g. PRBS(2<sup>15</sup>-1);

- the output signal of the test equipment shall be HDB3 encoded and conform to a pulse shape as defined in figure 15 of ITU-T Recommendation G.703 [1], which is reproduced in figure 2 of the present document, and a framing structure as defined in ITU-T Recommendation G.704 [2]. The test equipment shall generate the stimuli as defined in column 1 of table A.1.

| Table A.1: | Terminals    | not sup | porting | the E-bit |

|------------|--------------|---------|---------|-----------|

|            | 1 criminal 3 | not sup | porting |           |

| Stimulus from test equipment           | Result |

|----------------------------------------|--------|

| Continuous SMFs with correct CRC-4     | E = 1  |

| Continuous SMFs with incorrect CRC-4   | E = 1  |

| Signal causing loss of frame alignment |        |

| (e.g. Alarm Indication Signal (AIS))   | E = 1  |

Monitor: the E-bit in the output bit stream from the terminal equipment.

**Results:** the E-bit shall be as defined in column 2 of table A.1.

### A.2.9.3 Terminals using the E-bits to indicate errored SMFs

**Purpose:** to verify that for terminal equipments using the E-bit to indicate SMF errors, the E-bits are set correctly to indicate errored SMFs, as specified in clause 4.2.1.8.2.2.

### **Test configuration (see figure A.9):**

Interface state: powered.

#### Stimulus:

- the terminal equipment shall transmit a HDB3 bit stream according to the frame structure of annex C. The binary content of the data contained in bits 9 to 256 of the frame shall be a pseudo random bit stream, e.g. PRBS(2<sup>15</sup>-1);

- the output signal of the test equipment shall be HDB3 encoded and conform to a pulse shape as defined in figure 15 of ITU-T Recommendation G.703 [1], which is reproduced in figure 2 of the present document, and a framing structure as defined in ITU-T Recommendation G.704 [2]. The test equipment shall generate the stimuli as defined in column 1 of table A.2.

### Table A.2: Terminals using the E-bits to indicate errored SMFs

| Stimulus from test equipment                                    | Result                                                              |  |

|-----------------------------------------------------------------|---------------------------------------------------------------------|--|

| One SMF with an incorrect CRC-4 within a stream of              | One E-bit of $E = 0$ , sent within 1 second of the errored SMF, the |  |

| SMFs with correct CRC-4s                                        | other E-bits being E = 1.                                           |  |

| Two consecutive SMFs with incorrect CRC-4s within               | Two consecutive E-bits of $E = 0$ , sent within 1 second of the     |  |

| a stream of SMFs with correct CRC-4s                            | errored SMF, the other E-bits being $E = 1$ .                       |  |

| NOTE: Two consecutive E-bits may be in consecutive multiframes. |                                                                     |  |

Monitor: the E-bit in the output bit stream from the terminal equipment.

**Results:** the E-bit shall be as defined in column 2 of table A.2.

### A.2.9.4 Use of the A-bit

**Purpose:** to verify that the A-bit is set correctly to indicate conditions at the terminal equipment input port as specified in clause 4.2.1.8.3.1 or clause 4.2.1.8.3.2.

#### **Test configuration (see figure A.9):**

#### Interface state: powered.

### Stimulus:

- the terminal equipment shall transmit a HDB3 bit stream according to the frame structure of annex C. The binary content of the data contained in bits 9 to 256 of the frame shall be a pseudo random bit stream, e.g. PRBS(2<sup>15</sup>-1);

- the output signal of the test equipment shall be HDB3 encoded and conform to a pulse shape as defined in figure 15 of ITU-T Recommendation G.703 [1], which is reproduced in figure 2 of the present document, and a framing structure as defined in ITU-T Recommendation G.704 [2]. The binary content of the data contained in bits 9 to 256 of the frame shall be a fixed pattern that does not contain a simulated frame alignment signal. The test equipment shall generate the stimuli as defined in column 1 of table A.3.

|   | Stimulus from test equipment (see notes 1 and 2)                                                                                                                                                                                                                                                                                                                                                                                     | Result (see note 3)                                                                                                                                                                                                                                |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | Continuous frame sequence containing one incorrect frame alignment signal. (2 F 2 F 2 / F 2 F 2 F)                                                                                                                                                                                                                                                                                                                                   | A = 0                                                                                                                                                                                                                                              |

| 2 | Continuous frame sequence containing two consecutive incorrect frame alignment signals.<br>(2 F 2 F 2 /F 2 /F 2 F 2 F)                                                                                                                                                                                                                                                                                                               | A = 0                                                                                                                                                                                                                                              |

| 3 | Continuous frame sequence containing three consecutive incorrect frame alignment signals.<br>(2 F 2 F 2 /F 2 /F 2 /F 2 F 2 F.)                                                                                                                                                                                                                                                                                                       | A = 1 within 30 ms of the<br>last incorrect frame<br>alignment signal, returning<br>to A = 0 within 30 ms of two<br>correct frame alignment<br>signals.                                                                                            |

| 4 | Continuous frames with three consecutive incorrect frame alignment signals, then N x frame sequences alternating correct and incorrect frame alignment signals, a correct frame then M x frame sequences with the correct frame alignment signal but with the frames not containing the frame alignment signal with bit 2 = 0, followed by continuous correct frames.<br>(2 F 2 F 2 /F 2 /F 2 /F Nx(2 F 2 /F) 2 F Mx(/2 F) 2 F 2 F.) | A = 1 within 30 ms of the<br>third incorrect frame<br>alignment signal, staying at<br>A = 1 until $A = 0$ within<br>30 ms of two consecutive<br>correct frame alignment<br>signals.<br>It is recommended that M<br>and N be between 40 and<br>100. |

| 5 | Continuous frames with two consecutive frames not h containing the frame alignment signal having bit $2 = 0$ .<br>(2 F 2 F /2 F /2 F 2 F 2 F)                                                                                                                                                                                                                                                                                        | A = 0                                                                                                                                                                                                                                              |

| 6 | Continuous frames with three consecutive frames not containing the frame alignment signal having bit 2 = 0.<br>(2 F 2 F /2 F /2 F /2 F 2 F 2 F)                                                                                                                                                                                                                                                                                      | A = 1 shall be set within<br>30 ms of the third frame<br>with bit 2 = 0, returning to<br>A = 0 within 30 ms of two<br>correct frame alignment<br>signals.                                                                                          |

| 7 | Continuous frames with 914 consecutive errored SMFs.<br>followed by 86 consecutive non-errored SMFs,<br>followed by 914 consecutive errored SMFs,<br>followed by continuous non-errored SMFs.<br>(SMF SMF 914x/SMF 86xSMF 914x/SMF SMF)                                                                                                                                                                                              | A = 0                                                                                                                                                                                                                                              |

### Table A.3: Terminals using the A-bit

|      | Stimulus from test equipment (see notes 1 and 2)                                  | Result (see note 3)        |  |  |  |

|------|-----------------------------------------------------------------------------------|----------------------------|--|--|--|

| 8    | Continuous frames with 915 consecutive errored SMFs,                              | During this time the A-bit |  |  |  |

|      | followed by 85 consecutive non-errored SMFs,                                      | shall                      |  |  |  |

|      | followed by 915 consecutive errored SMFs,                                         | change at least once from  |  |  |  |

|      | followed by continuous non-errored SMFs.                                          | A = 0 to $A = 1$           |  |  |  |

|      | (SMF SMF 915x/SMF 85xSMF 915x/SMF SMF)                                            | and back to $A = 0$ .      |  |  |  |

| NOTE | 1: Each test defined within the table shall be preceded by sufficient correct fra | ames to ensure frame and   |  |  |  |

|      | multiframe alignment.                                                             |                            |  |  |  |

| NOTE | TE 2: F is a frame with a correct frame alignment signal;                         |                            |  |  |  |

|      | /F is a frame with an incorrect frame alignment signal;                           |                            |  |  |  |

|      | 2 is the frame not containing the frame alignment signal having bit 2 set to 1;   |                            |  |  |  |

|      | /2 is the frame not containing the frame alignment signal having bit 2 set to 0;  |                            |  |  |  |

|      | SMF is a Sub-MultiFrame having correct frame alignment and correct CRC-4 bits;    |                            |  |  |  |

|      | /SMF is a Sub-MultiFrame having correct frame alignment and incorrect CRC-4 bits. |                            |  |  |  |

| NOTE | 3: Result for terminals complying with clause 4.2.1.8.3.2.                        |                            |  |  |  |

Monitor: the A-bit in the output bit stream from the terminal equipment.

#### **Results:**

- for terminal equipments complying with clause 4.2.1.8.3.1 (i.e. those not using the A-bit), the A-bit shall be set to binary ZERO for all stimuli in column 2 of table A.3;

- for terminal equipments complying with clause 4.2.1.8.3.2 (i.e. those using the A-bit), the A-bit shall be as defined in table A.3. Requirements tested by test 6 of table A.3 is an optional requirements, it shall only be performed if this implementation is declared by the manufacturer.

### A.2.10 Input frame structure

### A.2.10.1 Frame alignment

**Purpose:** to verify that the terminal equipment input port can achieve frame alignment as specified in clause 4.2.2.9.1. Terminal equipments using the A-bit according to clause 4.2.1.8.3.2 and conforming to the tests in clause A.2.9.4 do not need to be tested as defined in this clause since conformance is demonstrated by compliance with clause A.2.9.4.

### **Test configuration (see figure A.10):**

Figure A.10: Frame alignment

Interface state: powered, with received data from bits 9 to 256 of the input frame looped back to the output port.

**Stimulus:** the output signal of the test equipment shall be HDB3 encoded and conform to a pulse shape as defined in figure 15 of ITU-T Recommendation G.703 [1], which is reproduced in figure 2 of the present document, and a framing structure as defined in ITU-T Recommendation G.704 [2]. The binary content of the data contained in bits 9 to 256 of the frame shall be a fixed pattern that does not contain any simulated frame alignment signal. The test equipment shall generate the stimuli as defined in column 1 of table A.4.

| Table A.4: | Frame | alignment |

|------------|-------|-----------|

|------------|-------|-----------|

|         | Stimulus from test equipment (see notes 1 and 2)                                  | Result                                   |  |  |  |

|---------|-----------------------------------------------------------------------------------|------------------------------------------|--|--|--|

| 1       | Continuous frame sequence containing one incorrect frame                          | No breaks in the data.                   |  |  |  |

|         | alignment signal.                                                                 | No errors in the received data.          |  |  |  |

|         | (2 F 2 F 2 /F 2 F 2 F)                                                            |                                          |  |  |  |

| 2       | Continuous frame sequence containing two consecutive                              | No breaks in the data.                   |  |  |  |

|         | incorrect frame alignment signals.                                                | No errors in the received data.          |  |  |  |

|         | (2 F 2 F 2 /F 2 /F 2 F 2 F)                                                       |                                          |  |  |  |

| 3       | Continuous frame sequence containing three consecutive                            | Any break in the data                    |  |  |  |

|         | incorrect frame alignment signals.                                                | shall be less than 20,5 ms.              |  |  |  |

|         | (2 F 2 F 2 /F 2 /F 2 /F 2 F 2 F)                                                  |                                          |  |  |  |

| 4       | Continuous frames with three consecutive incorrect frame                          | Any break in data transmission           |  |  |  |

|         | alignment signals, then N x frame sequences alternating                           | shall be less than                       |  |  |  |

|         | correct and incorrect frame alignment signals, a correct                          | 20,75 + 0,5 x (N + M/2) ms.              |  |  |  |

|         | frame then M x frame sequences with the correct frame                             | It is recommended that M and N           |  |  |  |

|         | alignment signal but with the frames not containing the                           | be between 40 and 100.                   |  |  |  |

|         | frame alignment signal with bit $2 = 0$ ,                                         |                                          |  |  |  |

|         | followed by continuous correct frames.                                            |                                          |  |  |  |

|         | (2 F 2 F 2 /F 2 /F 2 /F Nx(2 F 2 /F) 2 F Mx (/2 F) 2 F 2 F)                       |                                          |  |  |  |

| 5       | Continuous frames with two consecutive frames not                                 | No breaks in the data.                   |  |  |  |

|         | containing the frame alignment signal having bit $2 = 0$ .                        | No errors in the received data.          |  |  |  |

|         | (2 F 2 F /2 F /2 F 2 F 2 F)                                                       |                                          |  |  |  |

| 6       | Continuous frames with three consecutive frames not                               | A break in the data may occur            |  |  |  |

|         | containing the frame alignment signal having bit $2 = 0$ .                        | in some implementations.                 |  |  |  |

|         | (2 F 2 F /2 F /2 F /2 F 2 F 2 F)                                                  | Any break shall be less than             |  |  |  |

|         |                                                                                   | 20,5 ms.                                 |  |  |  |

| 7       | Continuous frames with 914 consecutive errored SMFs,                              | No breaks in the data.                   |  |  |  |

|         | followed by 86 consecutive non-errored SMFs,                                      | No errors in the received data.          |  |  |  |

|         | followed by 914 consecutive errored SMFs,                                         |                                          |  |  |  |

|         | followed by continuous non-errored SMFs.                                          |                                          |  |  |  |