Technical Specification

Transmission and Multiplexing (TM);

High bit-rate Digital Subscriber Line (HDSL)

transmission systems on metallic local lines;

HDSL core specification and applications for combined

ISDN-BA and 2 048 kbit/s transmission

#### Reference

RTS/TM-06009 (aic00jor.PDF)

#### Keywords

access, basic, digital, HDSL, ISDN, local loop, rate, subscriber, transmission

#### **ETSI**

#### Postal address

F-06921 Sophia Antipolis Cedex - FRANCE

#### Office address

650 Route des Lucioles - Sophia Antipolis

Valbonne - FRANCE

Tel.: +33 4 92 94 42 00 Fax: +33 4 93 65 47 16

Siret N° 348 623 562 00017 - NAF 742 C

Association à but non lucratif enregistrée à la

Sous-Préfecture de Grasse (06) N° 7803/88

#### Internet

secretariat@etsi.fr

Individual copies of this ETSI deliverable

can be downloaded from

http://www.etsi.org

#### **Copyright Notification**

No part may be reproduced except as authorized by written permission. The copyright and the foregoing restriction extend to reproduction in all media.

© European Telecommunications Standards Institute 1998. All rights reserved.

# Contents

| Intelle            | ectual Property Rights                                              | 11 |

|--------------------|---------------------------------------------------------------------|----|

| Forew              | ord                                                                 | 11 |

| 1                  | Scope                                                               | 12 |

| 2                  | References                                                          | 13 |

| 3                  | Abbreviations                                                       | 14 |

| 4                  | Reference configuration and functional description                  | 15 |

| 5                  | HDSL core specification                                             | 18 |

| 5.1                | Functions                                                           |    |

| 5.1.1              | Transparent transport of core frames.                               |    |

| 5.1.2              | Stuffing and destuffing                                             |    |

| 5.1.2              | CRC-6 procedures and transmission error detection                   |    |

| 5.1.3              | Error reporting                                                     |    |

| 5.1.4              | Failure detection                                                   |    |

| 5.1.6              | Failure reporting                                                   |    |

| 5.1.0              | Bit timing                                                          |    |

| 5.1.7              | Frame alignment                                                     |    |

| 5.1.9              | HDSL transceiver autonomous start-up control                        |    |

| 5.1.10             | Loopback control and co-ordination                                  |    |

| 5.1.10             | Mapping between core frames and HDSL frames                         |    |

| 5.1.11             | Control of the maintenance channel                                  |    |

| 5.1.12             | Synchronization and co-ordination of HDSL transceivers              |    |

| 5.1.13             | Identification of pairs                                             |    |

| 5.1.14             | Correction of pairs                                                 |    |

| 5.1.15             | Remote power feeding                                                |    |

| 5.1.10             | Wetting current                                                     |    |

| 5.1.17<br>5.2      | Transmission medium                                                 |    |

| 5.2.1              | Description Description                                             |    |

| 5.2.1              | Minimum Digital Local Line (DLL) requirements for HDSL applications |    |

| 5.2.2              | DLL physical characteristics                                        | 20 |

| 5.2.4              | DLL electrical characteristics                                      |    |

| 5.2.4<br>5.2.4.1   |                                                                     |    |

| 5.2.4.1<br>5.2.4.2 |                                                                     |    |

| 5.2.4.2<br>5.2.4.3 | 1 7                                                                 |    |

| 5.2.4.3<br>5.2.4.4 |                                                                     |    |

| 5.2.4.4<br>5.2.4.5 |                                                                     |    |

| 5.2.4.5<br>5.2.4.6 | •                                                                   |    |

| 5.2.4.0<br>5.3     | Transmission method                                                 |    |

| 5.3.1              | General                                                             |    |

| 5.3.1              | Transmission on three pairs                                         |    |

| 5.3.2<br>5.3.3     | Transmission on three pairs                                         |    |

|                    | <u>.</u>                                                            |    |

| 5.3.4              | Transmission on one pair                                            |    |

| 5.3.5              | Transmission on four pairs                                          |    |

| 5.3.6              |                                                                     |    |

| 5.3.7              | Line baud rate                                                      |    |

| 5.4                | Frame structure                                                     |    |

| 5.4.1              | Core frame                                                          |    |

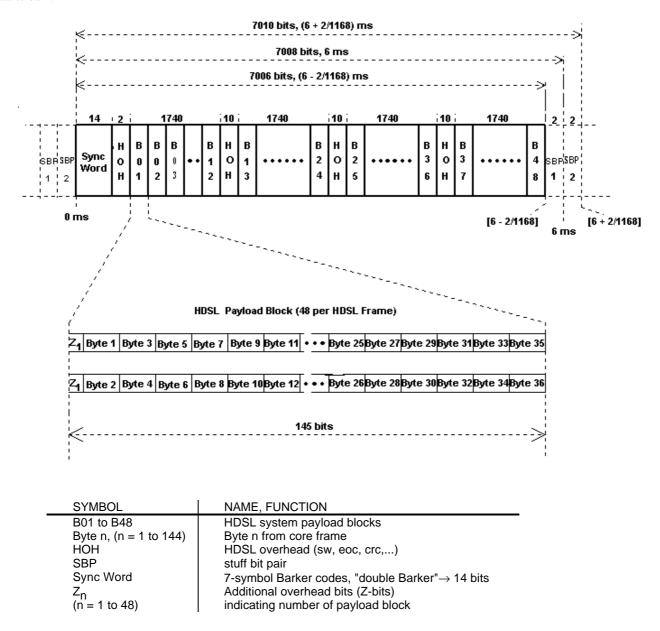

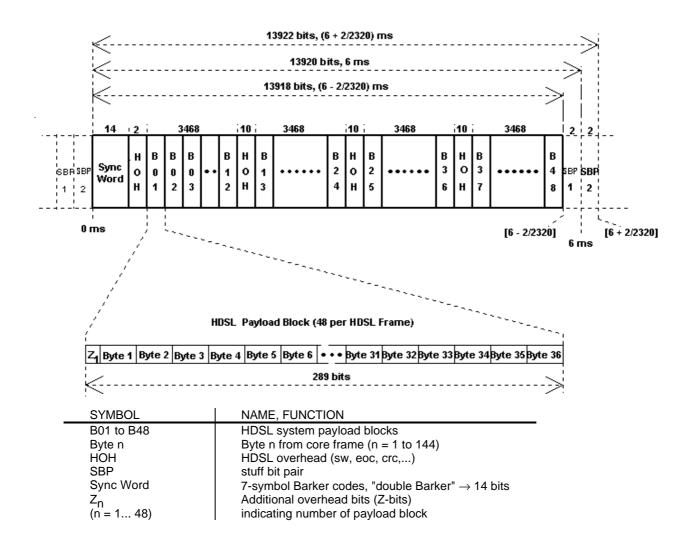

| 5.4.2<br>5.4.2.1   | 2B1Q HDSL frame structure                                           |    |

| 5.4.2.1            |                                                                     |    |

| 5.4.2.1            | 1 ,                                                                 |    |

| 5.4.2.1            | 1 ,                                                                 |    |

| 5.4.2.1            | 1 7                                                                 |    |

| 5.4.2.2            | e                                                                   |    |

| 5.4.3              | Scrambling method                                                   | 36 |

| 5.5              | HDSL embedded operations channel (eoc)                |    |

|------------------|-------------------------------------------------------|----|

| 5.5.1            | Functions of the HDSL eoc                             | 39 |

| 5.5.2            | HDSL eoc acknowledgement protocol                     | 39 |

| 5.5.2.1          | Message/echo response protocol state                  | 40 |

| 5.5.2.2          | Unable To Comply (UTC) mode of operation              | 40 |

| 5.5.3            | The HDSL eoc data read/write mode                     |    |

| 5.5.3.1          | Data read protocol                                    |    |

| 5.5.3.2          | HDSL eoc data read mode requirements                  |    |

| 5.5.3.3          | Data write protocol                                   |    |

| 5.5.3.4          | HDSL eoc data write mode requirements                 |    |

| 5.5.4            | HDSL eoc message list                                 |    |

|                  |                                                       |    |

| 5.5.5            | HDSL eoc message set requirements                     |    |

| 5.5.6            | Data registers in the NTU and in regenerators         |    |

| 5.5.7            | Noise margin                                          |    |

| 5.5.7.1          | General                                               |    |

| 5.5.7.2          | Coding of the noise margin values                     |    |

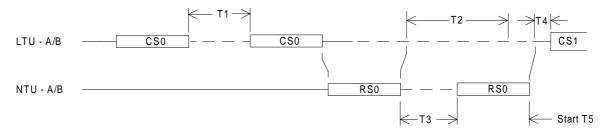

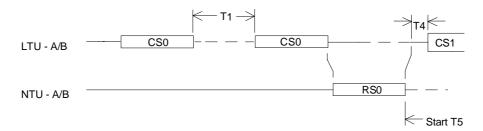

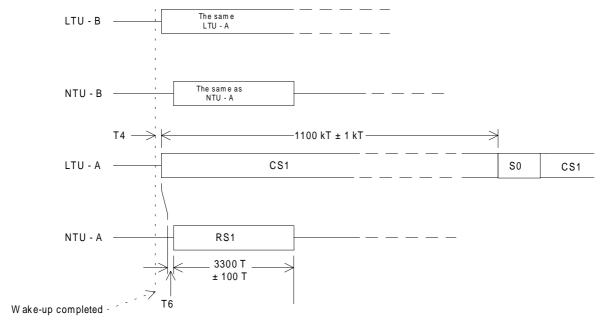

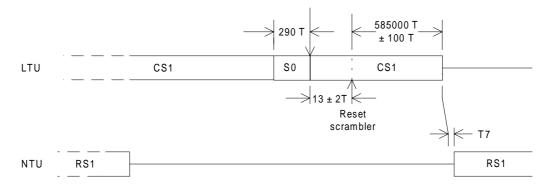

| 5.6              | Start-up procedure                                    |    |

| 5.6.1            | General                                               |    |

| 5.6.1.1          | Start-up                                              |    |

| 5.6.1.2          | Activation of HDSL transceiver pairs                  | 49 |

| 5.6.1.3          | Transparency                                          | 49 |

| 5.6.1.4          | Noise margin                                          | 49 |

| 5.6.2            | Control and status signals                            | 49 |

| 5.6.2.1          | Control signals                                       | 49 |

| 5.6.2.1.1        | QUIET                                                 |    |

| 5.6.2.1.2        | ACTREQ                                                |    |

| 5.6.2.2          | Status signals                                        |    |

| 5.6.2.2.1        | LOSW                                                  |    |

| 5.6.2.2.2        | LOSWT                                                 |    |

| 5.6.2.2.3        | LOS                                                   |    |

| 5.6.2.2.4        | LOST                                                  |    |

| 5.6.2.2.5        | INDC                                                  |    |

| 5.6.2.2.6        | INDRINDR                                              |    |

| 5.6.3            | Transmitted signals                                   |    |

|                  | e e e e e e e e e e e e e e e e e e e                 |    |

| 5.6.3.1          | Silent                                                |    |

| 5.6.3.2          | S0 signal                                             |    |

| 5.6.3.3          | S1 signal                                             |    |

| 5.6.3.4          | 2B1Q data                                             |    |

| 5.6.4            | Timers                                                |    |

| 5.6.4.1          | T1                                                    |    |

| 5.6.4.2          | T2                                                    |    |

| 5.6.4.3          | T3                                                    | 51 |

| 5.6.4.4          | T4                                                    | 51 |

| 5.6.4.5          | T-Act                                                 | 51 |

| 5.6.4.6          | Timer values                                          | 51 |

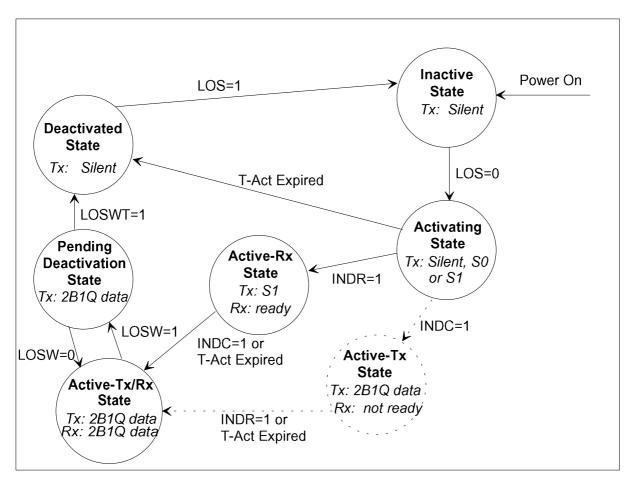

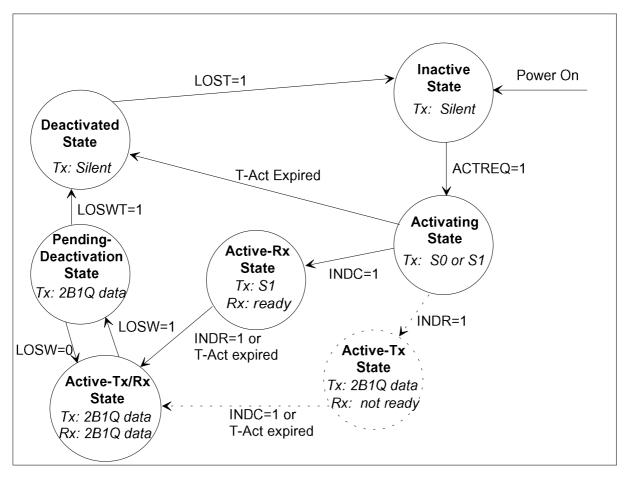

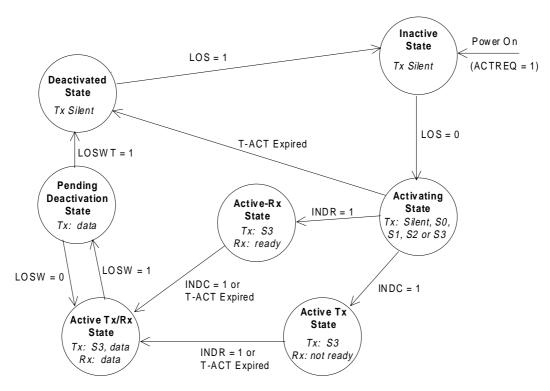

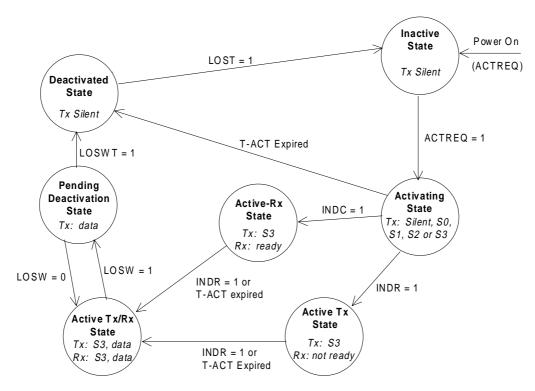

| 5.6.5            | Activation state diagrams                             | 52 |

| 5.6.5.1          | HDSL transceiver states at the NTU                    |    |

| 5.6.5.2          | HDSL transceiver states at the LTU                    |    |

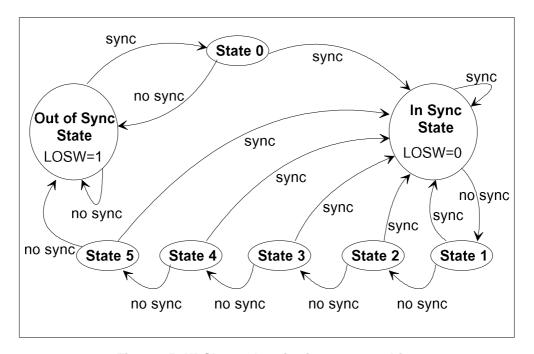

| 5.6.5.3          | The HDSL synchronization state machine                |    |

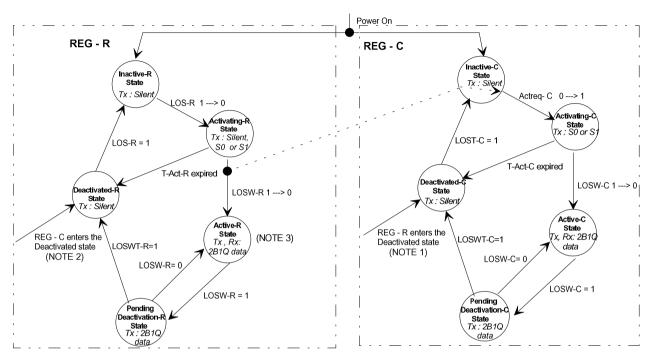

| 5.6.6            | Regenerator related procedures                        |    |

| 5.6.6.1          | Activation state diagrams for the REG                 |    |

| 5.6.6.1.1        | HDSL transceiver states at the REG-R                  |    |

| 5.6.6.1.2        | HDSL transceiver states at the REG-C                  |    |

| 5.0.0.1.2<br>5.7 | Operation and Maintenance (O&M)                       |    |

|                  |                                                       |    |

| 5.7.1            | Functions at the LTU external O&M reference point.    |    |

| 5.7.2            | Functions at the NTU external O&M reference point     |    |

| 5.7.3            | O&M messages and functions supported by the HDSL core |    |

| 5.7.4            | Power feeding related O&M functions                   |    |

| 5.7.5            | Regenerator behaviour                                 |    |

| 5.7.5.1          | Response to LOS/LFA                                   | 65 |

| 5.7.5.2          | Operation of loopback 1A                                     |    |

|------------------|--------------------------------------------------------------|----|

| 5.8              | Electrical characteristics of a single 2B1Q transceiver      | 66 |

| 5.8.1            | General                                                      |    |

| 5.8.2            | Transmitter/Receiver impedance and return loss               |    |

| 5.8.3            | Transceiver reference clock                                  |    |

| 5.8.4            | Transmitter output characteristics                           |    |

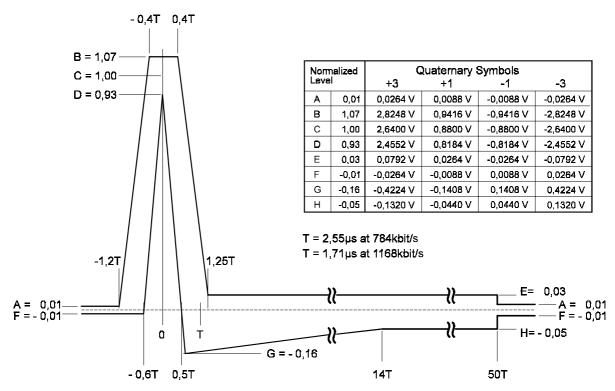

| 5.8.4.1          | Pulse amplitude                                              |    |

| 5.8.4.2          | Pulse shape                                                  |    |

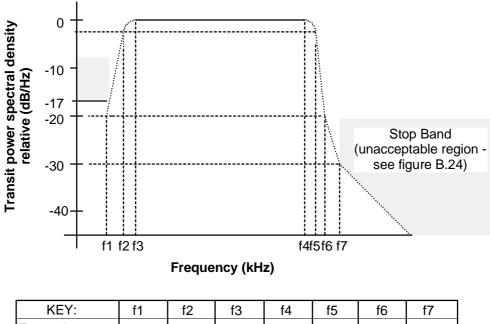

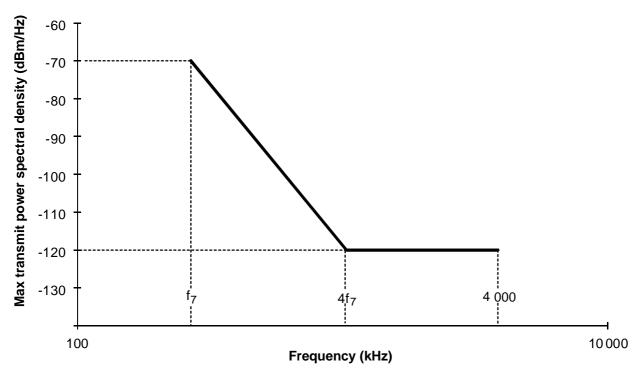

| 5.8.4.3          | Power Spectral Density (PSD)                                 |    |

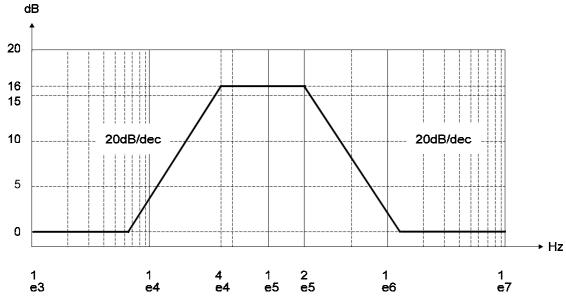

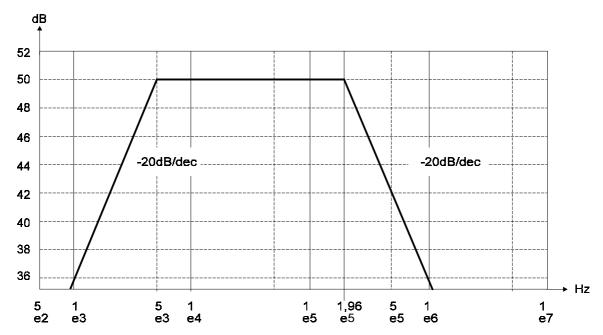

| 5.8.4.3.1        | PSD for 392 kbaud systems                                    |    |

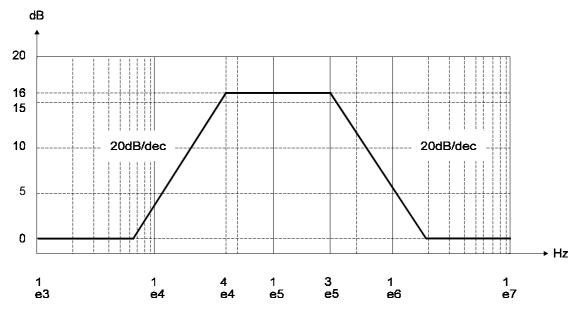

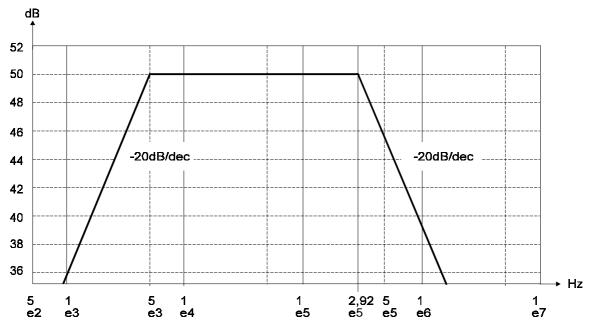

| 5.8.4.3.2        | PSD for 584 kbaud systems                                    |    |

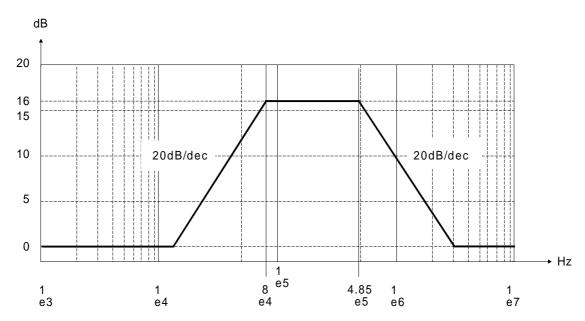

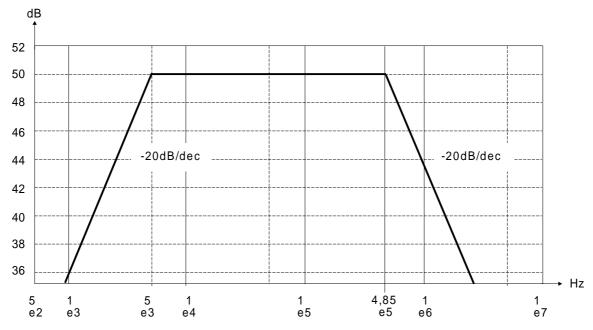

| 5.8.4.3.3        | PSD for 1 160 kbaud systems                                  |    |

| 5.8.4.4          | Total power                                                  | 70 |

| 5.8.5            | Unbalance about earth                                        |    |

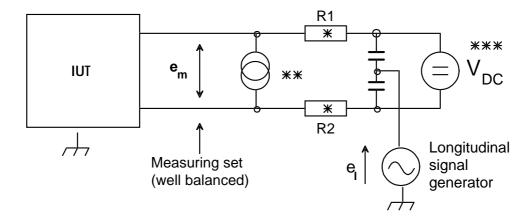

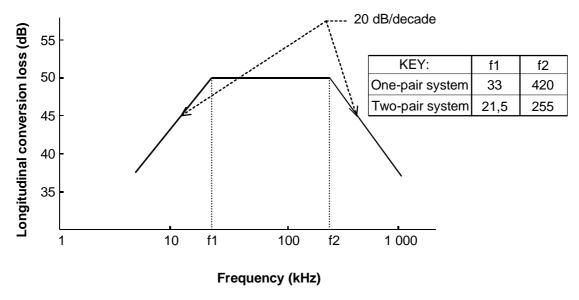

| 5.8.5.1          | Longitudinal Conversion Loss (LCL)                           | 71 |

| 5.8.5.2          | Longitudinal output voltage                                  |    |

| 5.9              | Performance of individual HDSL transceivers                  | 74 |

| 5.9.1            | Performance requirements                                     |    |

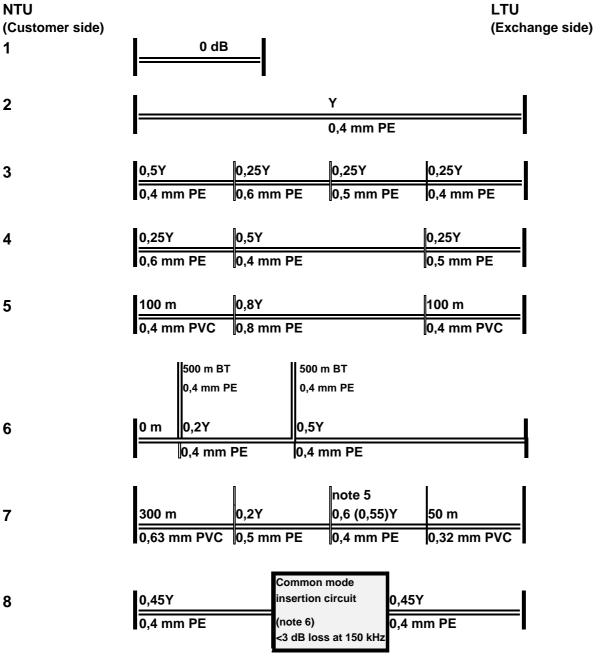

| 5.9.2            | DLL physical models (test loops)                             | 74 |

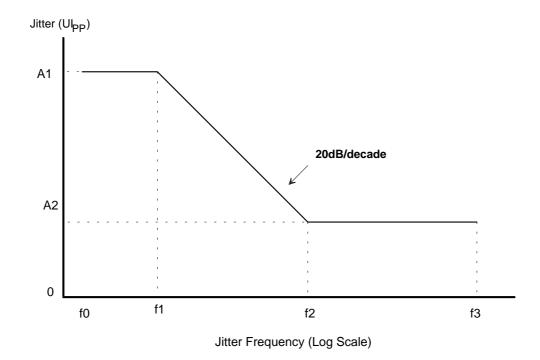

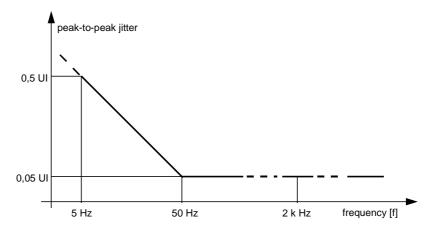

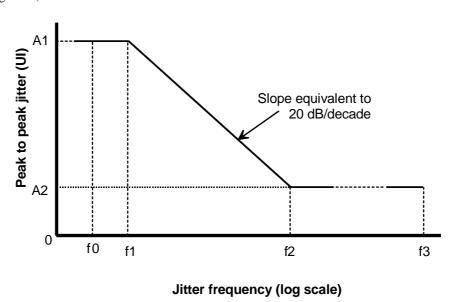

| 5.9.3            | Jitter and wander                                            | 74 |

| 5.9.3.1          | General                                                      | 74 |

| 5.9.3.2          | Input jitter tolerance at the HDSL transceiver at the NTU    | 75 |

| 5.9.3.3          | Output jitter limitations at the HDSL transceiver at the NTU |    |

| 5.9.3.4          | Input jitter tolerance at the HDSL transceiver at the LTU    | 75 |

| 5.9.3.5          | Output jitter limitation of the HDSL transceiver at the LTU  | 75 |

| 6 C              | ommon circuitry specification                                | 76 |

|                  |                                                              |    |

| 6.1              | Delay difference buffer                                      |    |

| 6.2<br>6.2.1     | The pair identification mechanism                            |    |

|                  | Pair identification initial values                           |    |

| 6.2.2<br>6.2.3   | Pair identification at the NTU                               |    |

| 6.2.3<br>6.3     | Pair identification at the LTU                               |    |

|                  | Laboratory performance measurements                          |    |

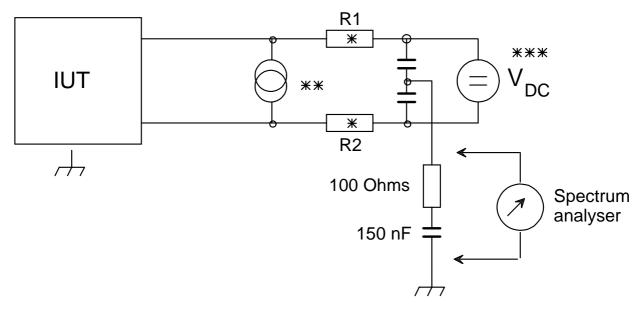

| 6.3.1            | Test configuration                                           |    |

| 6.3.2            | 8                                                            |    |

| 6.3.3<br>6.3.3.1 | Test procedure with shaped noise                             |    |

| 6.3.3.2          |                                                              |    |

|                  | Generation                                                   |    |

| 6.3.3.3          | Injection                                                    |    |

| 6.3.3.4          | Tolerances and calibration                                   |    |

| 6.3.3.4.1        | 0 dB level calibration                                       |    |

| 6.3.3.4.2        | Test loop tolerances                                         |    |

| 6.3.4            | Test procedure for impulse noise                             |    |

| 6.3.4.1          | Impulse noise test waveform                                  |    |

| 6.3.4.2          | Impulse noise test measurement                               |    |

| 6.3.4.3          | Impulse noise test performance requirements                  |    |

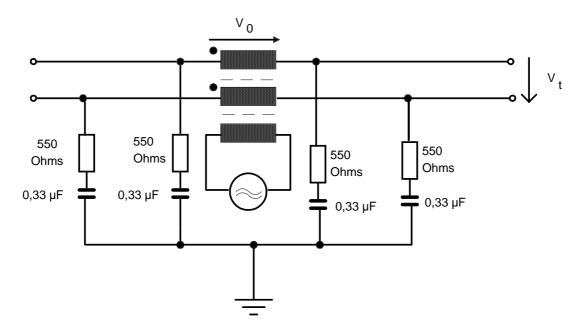

| 6.3.5            | Common mode rejection test                                   |    |

| 6.3.6            | Micro-interruption test                                      | 83 |

| 7 A              | pplication specific requirements                             | 85 |

| 7.1              | Application specific requirements for ISDN PRA               |    |

| 7.1.1            | Mapping of 2 048 kbit/s to HDSL                              |    |

| 7.1.2            | Mapping of HDSL maintenance functions to the interface       |    |

| 7.1.3            | Performance Performance                                      |    |

| 7.1.3.1          | Performance specification                                    |    |

| 7.1.3.1          | Signal transfer delay                                        |    |

| 7.1.3.2          | Clock specification for external interfaces                  |    |

| 7.1.3.3.1        | NTU clock tolerance                                          |    |

| 7.1.3.3.1        | LTU clock tolerance                                          |    |

| 7.1.3.3.2        | Jitter specification                                         |    |

| 7.1.3.3.4        | Wander specification                                         |    |

|                  |                                                              |    |

| 7.1.3.4                     | Laboratory performance measurement                                                               |     |

|-----------------------------|--------------------------------------------------------------------------------------------------|-----|

| 7.2                         | Application specific requirements for the 2 048 kbit/s digital unstructured leased line (D2048U) | 89  |

| 7.2.1                       | Application interfaces                                                                           |     |

| 7.2.1.1                     | Application interface at the customer side                                                       | 89  |

| 7.2.1.2                     | Application interface at the network side                                                        | 89  |

| 7.2.2                       | Mapping of the D2048U signal to HDSL                                                             | 89  |

| 7.2.3                       | Mapping of HDSL maintenance functions to the interface                                           | 89  |

| 7.2.4                       | Performance                                                                                      |     |

| 7.2.4.1                     | Performance specification                                                                        |     |

| 7.2.4.2                     | Signal transfer delay                                                                            |     |

| 7.2.4.3                     | Clock specification for external interfaces                                                      |     |

| 7.2.4.3.1                   | NTU clock tolerance                                                                              |     |

| 7.2.4.3.2                   | LTU clock tolerance                                                                              |     |

| 7.2.4.3.3                   | Jitter specification                                                                             |     |

| 7.2.4.4                     | Laboratory performance measurements                                                              |     |

| 7.2. <del>4</del> .4<br>7.3 | Application specific requirements for the 2 048 kbit/s digital structured leased line (D2048S)   |     |

| 7.3<br>7.3.1                | Application interfaces                                                                           |     |

| 7.3.1<br>7.3.1.1            | Application interfaces Application interface at the customer side                                |     |

|                             |                                                                                                  |     |

| 7.3.1.2                     | Application interface at the network side                                                        |     |

| 7.3.2                       | Mapping of the D2048S signal to HDSL                                                             |     |

| 7.3.3                       | Mapping of HDSL maintenance functions to the interface                                           |     |

| 7.3.4                       | Performance                                                                                      |     |

| 7.3.4.1                     | Performance specification                                                                        |     |

| 7.3.4.2                     | Signal transfer delay                                                                            |     |

| 7.3.4.3                     | Clock specification for external interfaces.                                                     |     |

| 7.3.4.3.1                   | NTU clock tolerance                                                                              |     |

| 7.3.4.3.2                   | LTU clock tolerance                                                                              |     |

| 7.3.4.3.3                   | Jitter specification                                                                             |     |

| 7.3.4.4                     | Laboratory performance measurements                                                              |     |

| 7.4                         | Application specific requirements for fractional installation                                    | 94  |

| 7.4.1                       | Mapping of fractional services to HDSL                                                           | 94  |

| 7.4.1.1                     | Overview of mapping procedure                                                                    | 94  |

| 7.4.1.2                     | Details of mapping of the application interface from the HDSL core frame                         | 94  |

| 7.4.1.3                     | Details of HDSL core frame mapping into HDSL frame                                               | 94  |

| 7.4.1.4                     | Optional external mappings into the application frame                                            | 94  |

| 7.4.2                       | Mapping of HDSL maintenance functions to the interface                                           | 95  |

| 7.4.3                       | Performance                                                                                      | 100 |

| 7.4.3.1                     | Performance specification                                                                        | 100 |

| 7.4.3.2                     | Clock specification for external interfaces                                                      |     |

| 7.4.3.2.1                   | Clock tolerance                                                                                  |     |

| 7.4.3.2.2                   | Jitter and wander specifications                                                                 |     |

| 7.4.3.3                     | Laboratory performance measurements                                                              |     |

| 7.5                         | Application specific requirements for partial operation                                          |     |

| 7.5.1                       | Mapping of the application frame for partial operation application                               |     |

| 7.5.2                       | Mapping of HDSL maintenance functions to the interface                                           |     |

| 7.5.3                       | Performance                                                                                      |     |

| 7.5.4                       | Remote power feeding.                                                                            |     |

| 7.5.5                       | Partial failure criteria.                                                                        |     |

| 7.5.6                       | Action following partial failure                                                                 |     |

| 7.5.0<br>7.5.7              | Time slot prioritization/reallocation                                                            |     |

| 7.5.7<br>7.6                | Application specific requirements for the 2 048 kbit/s mapped into TU-12 structure               |     |

| 7.6.1                       |                                                                                                  |     |

| 7.6.1<br>7.6.2              | Reference configuration                                                                          |     |

|                             | Application Interfaces                                                                           |     |

| 7.6.2.1                     | Application interface at the customer side                                                       |     |

| 7.6.2.2                     | Application interface at the network side                                                        |     |

| 7.6.3                       | Mapping of application frame into HDSL using TU-12 structure                                     |     |

| 7.6.3.1                     | Mapping of application frame into VC-12 structure                                                |     |

| 7.6.3.2                     | Mapping of VC-12 into TU-12                                                                      |     |

| 7.6.3.3                     | Mapping of TU-12 into HDSL                                                                       |     |

| 7.6.4                       | Mapping of HDSL maintenance functions to the interface                                           | 106 |

| 7.6.5     | Performance                                                                                           | 107 |

|-----------|-------------------------------------------------------------------------------------------------------|-----|

| 7.6.5.1   | Performance specification                                                                             | 107 |

| 7.6.5.2   | Signal transfer delay                                                                                 | 107 |

| 7.6.5.3   | Clock specification                                                                                   |     |

| 7.6.5.3.1 | Clock synchronization at the NTU                                                                      |     |

| 7.6.5.3.2 | Jitter specification                                                                                  |     |

| 7.6.5.4   | Laboratory performance measurement                                                                    |     |

| 7.7       | Application specific requirements for the simultaneous connection of 2 048 kbit/s digital signals and | 100 |

| 1.1       | ISDN-BA inside the HDSL core frame                                                                    | 111 |

| 7.7.1     |                                                                                                       |     |

|           | Reference Configuration                                                                               |     |

| 7.7.2     | Application interfaces                                                                                |     |

| 7.7.2.1   | Application interfaces at the customer side                                                           |     |

| 7.7.2.1.1 | 2 048 kbit/s interfaces                                                                               |     |

| 7.7.2.1.2 | ISDN interfaces                                                                                       |     |

| 7.7.2.2   | Application interfaces at the network side                                                            |     |

| 7.7.2.2.1 | 2 048 kbit/s interfaces                                                                               | 111 |

| 7.7.2.2.2 | ISDN interfaces                                                                                       | 111 |

| 7.7.3     | Mapping procedures                                                                                    | 112 |

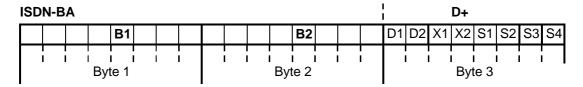

| 7.7.3.1   | Conversion of the ISDN-BA signals                                                                     | 112 |

| 7.7.3.2   | Mapping of the ISDN-BA to the core frame                                                              | 112 |

| 7.7.3.3   | Core frame mapping into HDSL frame                                                                    |     |

| 7.7.4     | Mapping of HDSL maintenance functions to the interface                                                |     |

| 7.7.5     | Performance                                                                                           |     |

| 7.7.5.1   | Performance specification                                                                             |     |

| 7.7.5.2   | Signal transfer delay                                                                                 |     |

| 7.7.5.3   | Clock specification                                                                                   |     |

| 7.7.5.3.1 | NTU clock tolerance                                                                                   |     |

| 7.7.5.3.1 |                                                                                                       |     |

|           | LTU clock tolerance                                                                                   |     |

| 7.7.5.3.3 | ISDN clock tolerance                                                                                  |     |

| 7.7.5.3.4 | Clock synchronization for ISDN-BA                                                                     |     |

| 7.7.5.3.5 | Jitter and wander specification                                                                       |     |

| 7.7.5.4   | Laboratory performance measurements                                                                   |     |

| 7.7.6     | Power feeding                                                                                         | 117 |

| 7.8       | Application specific requirements for the simultaneous connection of 2 048 kbit/s digital signals and |     |

|           | analogue telephone lines inside the HDSL core frame                                                   |     |

| 7.8.1     | Reference Configuration                                                                               |     |

| 7.8.2     | Application interfaces                                                                                |     |

| 7.8.2.1   | Application interface at the customer side                                                            | 118 |

| 7.8.2.1.1 | 2 048 kbit/s interfaces                                                                               | 118 |

| 7.8.2.1.2 | Analogue telephone interfaces                                                                         | 118 |

| 7.8.2.2   | Application interface at the network side                                                             | 118 |

| 7.8.2.2.1 | 2 048 kbit/s interfaces                                                                               |     |

| 7.8.2.2.2 | Analogue telephone interfaces                                                                         | 118 |

| 7.8.3     | Mapping procedures                                                                                    |     |

| 7.8.3.1   | Conversion of the analogue telephone signals                                                          |     |

| 7.8.3.2   | Mapping of the combined signals to the core frame                                                     |     |

| 7.8.3.3   | Core frame mapping into HDSL frame                                                                    |     |

| 7.8.4     | Mapping of HDSL maintenance functions to the interface                                                |     |

|           |                                                                                                       |     |

| 7.8.5     | Performance Specification                                                                             |     |

| 7.8.5.1   | Performance specification                                                                             |     |

| 7.8.5.2   | Signal transfer delay                                                                                 |     |

| 7.8.5.3   | Clock specification                                                                                   |     |

| 7.8.5.3.1 | NTU clock tolerance                                                                                   |     |

| 7.8.5.3.2 | LTU clock tolerance                                                                                   |     |

| 7.8.5.3.3 | Clock synchronization for analogue telephony interfaces                                               |     |

| 7.8.5.3.4 | Void                                                                                                  |     |

| 7.8.5.3.5 | Jitter and wander specification                                                                       |     |

| 7.8.5.4   | Laboratory performance measurements                                                                   |     |

| 7.8.6     | Power feeding                                                                                         | 121 |

| 8               | Power feeding                                                                   |     |

|-----------------|---------------------------------------------------------------------------------|-----|

| 8.1             | General                                                                         |     |

| 8.2             | Wetting current                                                                 |     |

| 8.3             | Remote power feeding aspects                                                    |     |

| 8.3.1           | Remote power feeding aspects at the LTU                                         |     |

| 8.3.2           | Remote power feeding aspects at the NTU                                         |     |

| 8.3.3           | Remote power feeding aspects at the regenerator                                 | 123 |

| 9               | Environmental requirements                                                      | 124 |

| 9.1             | Climatic conditions                                                             |     |

| 9.2             | Safety                                                                          |     |

| 9.3             | Overvoltage protection                                                          |     |

| 9.4             | Electromagnetic compatibility (EMC)                                             |     |

| Anne            | ex A (informative): Detailed definition of cable characteristics and test loops | 125 |

| A.1             | Typical characteristics of cables                                               |     |

|                 | 1 -                                                                             |     |

| A.2             | Theoretical characteristics of test loops for Y = 31 dB at 150 kHz              | 126 |

| Anne            | ex B (normative): High bit-rate Digital Subscriber Line (HDSL) CAP based system | 128 |

| B.1             | Scope and general information                                                   | 128 |

| B.1.1           | Scope                                                                           |     |

| B.2             | References                                                                      | 128 |

| B.3             | Abbreviations                                                                   | 128 |

| B.4             | Reference configuration and functional description                              |     |

|                 |                                                                                 |     |

| B.5             | HDSL core specification                                                         |     |

| B.5.1           | Functions                                                                       |     |

| B.5.2           |                                                                                 |     |

| B.5.3<br>B.5.3. |                                                                                 |     |

| B.5.3.          | <u>*</u>                                                                        |     |

| B.5.3.          |                                                                                 |     |

| B.5.3.          |                                                                                 |     |

| B.5.3.          | 1 7                                                                             |     |

| B.5.3.          | ± • •                                                                           |     |

| B.5.3.          |                                                                                 |     |

| B.5.4           | ·                                                                               |     |

| B.5.4.          |                                                                                 |     |

| B.5.4.          | 1 ,                                                                             |     |

| B.5.4.          |                                                                                 |     |

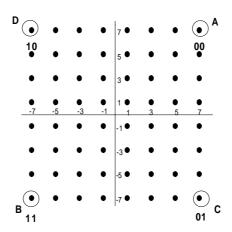

| B.5.5           | č                                                                               |     |

| B.5.5.          |                                                                                 |     |

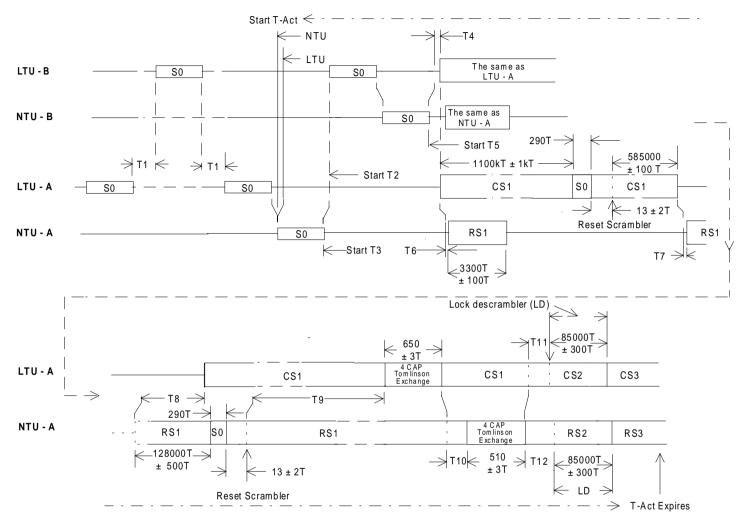

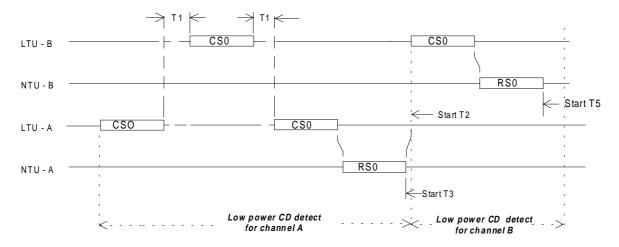

| B.5.6           | Start-up procedure                                                              | 141 |

| B.5.6.          | * *                                                                             |     |

| B.5.6.          | .1.1 Start-up                                                                   | 141 |

| B.5.6.          | 1                                                                               | 141 |

| B.5.6.          | 1 7                                                                             | 141 |

| B.5.6.          | .1.4 Signal quality (SQ)                                                        | 141 |

| B.5.6.          | $\epsilon$                                                                      |     |

| B.5.6.          | $\epsilon$                                                                      | 142 |

| B.5.6.          |                                                                                 |     |

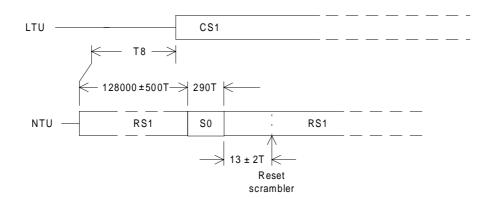

| B.5.6.          | .3.2 S0 signal                                                                  | 142 |

| B.5.6.3.3                  | S1 signal                                              |     |

|----------------------------|--------------------------------------------------------|-----|

| B.5.6.3.4                  | S2 signal                                              |     |

| B.5.6.3.5                  | S3 signal                                              | 142 |

| B.5.6.4                    | Timers                                                 | 143 |

| B.5.6.4.1                  | T1                                                     | 143 |

| B.5.6.4.2                  | T2                                                     | 143 |

| B.5.6.4.3                  | T3                                                     | 143 |

| B.5.6.4.4                  | T4                                                     | 143 |

| B.5.6.4.5                  | T5                                                     |     |

| B.5.6.4.6                  | T6                                                     |     |

| B.5.6.4.7                  | T7                                                     |     |

| B.5.6.4.8                  | T8                                                     |     |

| B.5.6.4.9                  | T9                                                     |     |

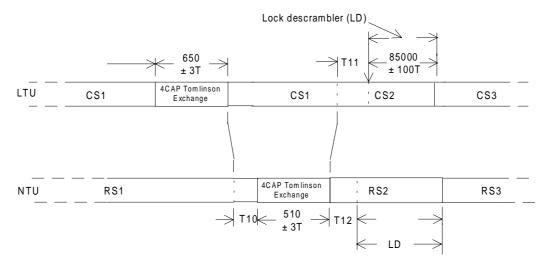

| B.5.6.4.10                 | T10                                                    |     |

| B.5.6.4.11                 | T11                                                    |     |

| B.5.6.4.12                 | T12                                                    |     |

| B.5.6.4.13                 | T-Act                                                  |     |

| B.5.6.4.14                 | Timer values                                           |     |

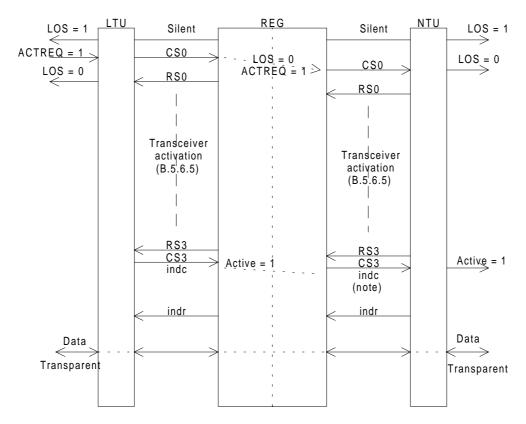

| B.5.6.5                    | HDSL transceiver activation                            |     |

| B.5.6.5.1                  | Alerting                                               |     |

| В.5.6.5.1.1                |                                                        |     |

| B.5.6.5.1.1<br>B.5.6.5.1.2 | Two pair system alerting sequence                      |     |

|                            | One pair transceiver alerting sequence                 |     |

| B.5.6.5.2                  | Transmit power mode selection                          |     |

| B.5.6.5.3                  | Front-end training                                     |     |

| B.5.6.5.4                  | Timing recovery, echo canceller and equalizer training |     |

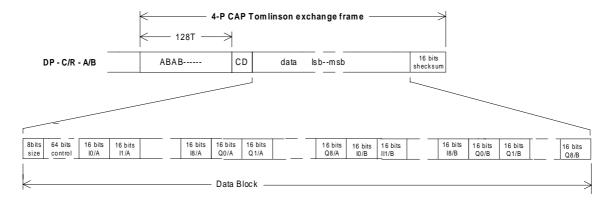

| B.5.6.5.5                  | Tomlinson coefficient exchange                         |     |

| B.5.6.5.6                  | Control field bit assignments                          |     |

| B.5.6.5.7                  | Transition to data mode                                |     |

| B.5.6.6                    | Retrain procedure                                      |     |

| B.5.6.7                    | Loop activation state diagrams                         |     |

| B.5.6.7.1                  | HDSL transceiver states at the NTU                     |     |

| B.5.6.7.1.1                | Inactive State                                         |     |

| B.5.6.7.1.2                | Activating State                                       |     |

| B.5.6.7.1.3                | Active-Rx State                                        |     |

| B.5.6.7.1.4                | Active-Tx State                                        |     |

| B.5.6.7.1.5                | Active-Tx/Rx State                                     |     |

| B.5.6.7.1.6                | Pending Deactivation State                             |     |

| B.5.6.7.1.7                | Deactivated State                                      |     |

| B.5.6.7.2                  | HDSL transceiver states at LTU                         | 154 |

| B.5.6.7.2.1                | Inactive State                                         | 154 |

| B.5.6.7.2.2                | Activating State                                       | 154 |

| B.5.6.7.2.3                | Active-Rx State                                        | 154 |

| B.5.6.7.2.4                | Active-Tx State                                        | 155 |

| B.5.6.7.2.5                | Active State                                           | 155 |

| B.5.6.7.2.6                | Pending Deactivation State                             | 155 |

| B.5.6.7.2.7                | Deactivated State                                      | 155 |

| B.5.6.7.3                  | The HDSL synchronization state machine                 | 155 |

| B.5.6.8                    | Regenerator related procedures                         | 155 |

| B.5.6.9                    | The pair identification mechanism for two pair system  | 156 |

| B.5.7 O                    | peration and Maintenance (O&M)                         |     |

| B.5.7.1                    | Regenerator behaviour                                  |     |

| B.5.7.1.1                  | Response to LOS/LFA                                    |     |

| B.5.7.1.2                  | Operation of loopback 1A                               |     |

|                            | lectrical characteristics of CAP-based transceivers    |     |

| B.5.8.1                    | General                                                |     |

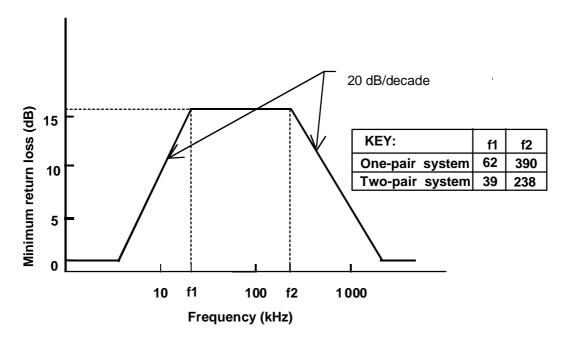

| B.5.8.2                    | Transmitter/receiver impedance and return loss         |     |

| B.5.8.3                    | Transceiver reference clock                            |     |

| B.5.8.3.1                  | One pair system clock                                  |     |

| B.5.8.3.2                  | Two pair system clock                                  |     |

| B.5.8.4                    | Transmitter output characteristics                     |     |

|                            | 1                                                      |     |

| B.5.8.4.1 Total power                                                                     |     |

|-------------------------------------------------------------------------------------------|-----|

| B.5.8.4.1.1 Two pair system total power                                                   |     |

| B.5.8.4.1.2 One pair system total power                                                   |     |

| B.5.8.4.2 PSD                                                                             |     |

| B.5.8.5 Unbalance about earth                                                             |     |

| B.5.8.5.1 Longitudinal Conversion Loss (LCL)                                              |     |

| B.5.8.5.2 Longitudinal output voltage                                                     |     |

| B.5.9 Performance of individual HDSL transceivers                                         | 161 |

| B.5.9.1 Performance requirements                                                          |     |

| B.5.9.2 DLL physical models for laboratory testing                                        |     |

| B.5.9.3 Jitter and wander                                                                 | 161 |

| B.5.9.3.1 General                                                                         |     |

| B.5.9.3.2 Input jitter tolerance at the HDSL transceiver at the NTU                       |     |

| B.5.9.3.3 Output jitter limitations of an HDSL transceiver in an NTU                      |     |

| B.5.9.3.4 Input jitter tolerance at the HDSL transceiver at the LTU                       | 163 |

| B.5.9.3.5 Output jitter limitation of the HDSL transceiver at the LTU                     | 163 |

| B.6 Common circuitry specification                                                        | 164 |

| B.6.1 Delay difference buffer                                                             | 164 |

| B.6.2 Laboratory performance measurement tests                                            | 164 |

| B.6.2.1 General                                                                           | 164 |

| B.6.2.2 Test configuration                                                                | 164 |

| B.6.2.3 Test procedure with random noise source                                           | 166 |

| B.6.2.3.1 Low crest factor noise                                                          | 166 |

| B.6.2.3.2 Truncated Gaussian noise                                                        | 166 |

| B.6.2.4 Test procedure for impulse noise                                                  | 166 |

| B.6.2.4.1 Impulse noise test waveform                                                     | 166 |

| B.6.2.4.2 Impulse noise test measurement                                                  | 166 |

| B.6.2.4.3 Impulse noise test performance requirements                                     | 166 |

| B.6.2.5 Common mode rejection test                                                        | 167 |

| B.6.2.6 Micro-interruption test                                                           |     |

| B.7 Application specific requirements                                                     | 168 |

| B.7.1 Application specific requirements for ISDN PRA                                      |     |

| B.7.1.1 Mapping of 2 048 kbit/s to HDSL                                                   |     |

| B.7.1.2 Mapping of HDSL maintenance functions to the interfaces                           |     |

| B.7.1.3 Performance                                                                       |     |

| B.7.1.3.1 Performance specification                                                       |     |

| B.7.1.3.2 Signal transfer delay                                                           |     |

| B.7.1.3.3 Clock specification for external interfaces                                     |     |

| B.7.2 Additional application specific requirements                                        |     |

| B.8 Power feeding                                                                         | 169 |

|                                                                                           |     |

| •                                                                                         |     |

| Annex C (informative): Transmission system for 1 544 kbit/s two pair system application . | 170 |

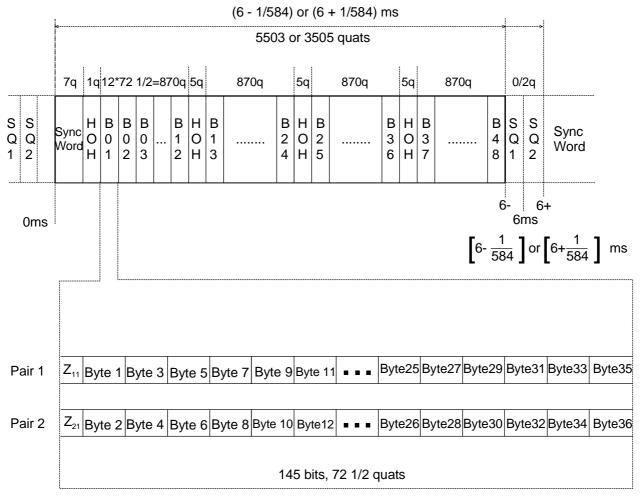

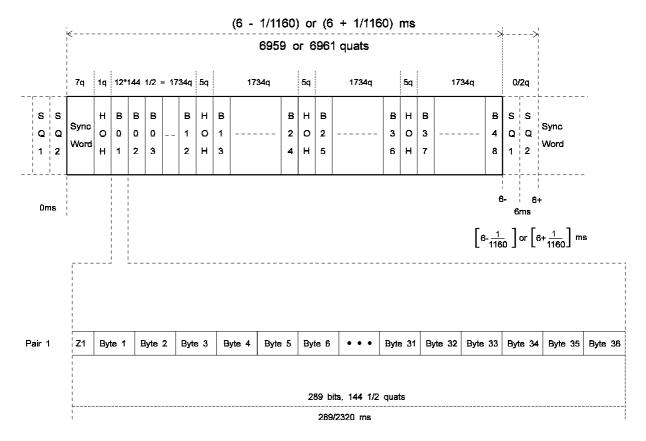

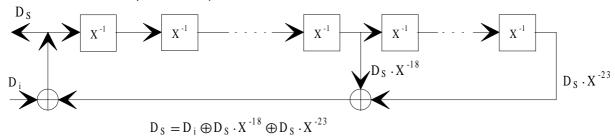

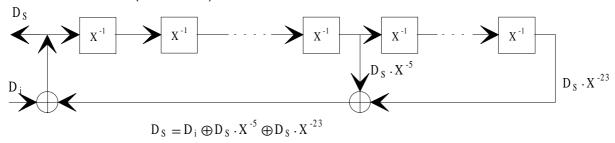

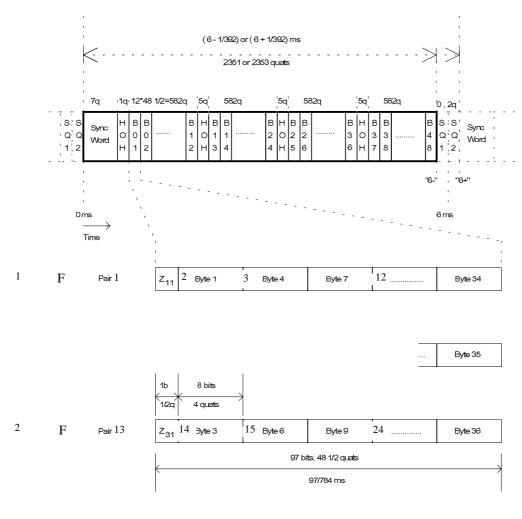

| C.1 Frame structure of the two pair system for 784 kbit/s                                 | 170 |

| History                                                                                   | 173 |

# Intellectual Property Rights

IPRs essential or potentially essential to the present document may have been declared to ETSI. The information pertaining to these essential IPRs, if any, is publicly available for **ETSI members and non-members**, and can be found in SR 000 314: "Intellectual Property Rights (IPRs); Essential, or potentially Essential, IPRs notified to ETSI in respect of ETSI standards", which is available **free of charge** from the ETSI Secretariat. Latest updates are available on the ETSI Web server (http://www.etsi.org/ipr).

Pursuant to the ETSI IPR Policy, no investigation, including IPR searches, has been carried out by ETSI. No guarantee can be given as to the existence of other IPRs not referenced in SR 000 314 (or the updates on the ETSI Web server) which are, or may be, or may become, essential to the present document.

# **Foreword**

This ETSI Technical Specification (TS) has been produced by ETSI Technical Committee Transmission and Multiplexing (TM).

The previous three versions have been published by ETSI as ETR 152 Editions 1, 2 and 3, while version 4 was published as TS 101 135 V1.4.1.

# 1 Scope

The present document describes a transmission technique called High bit-rate Digital Subscriber Line (HDSL), as a means for the transportation of several types of applications. The present document defines the requirements for the individual HDSL transmission system, the transmission performance, the HDSL maintenance requirements and procedures and the mapping of information from the dedicated applications.

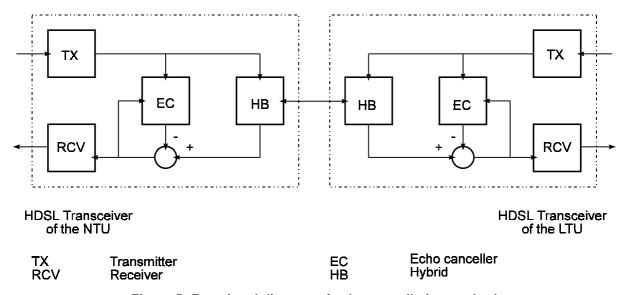

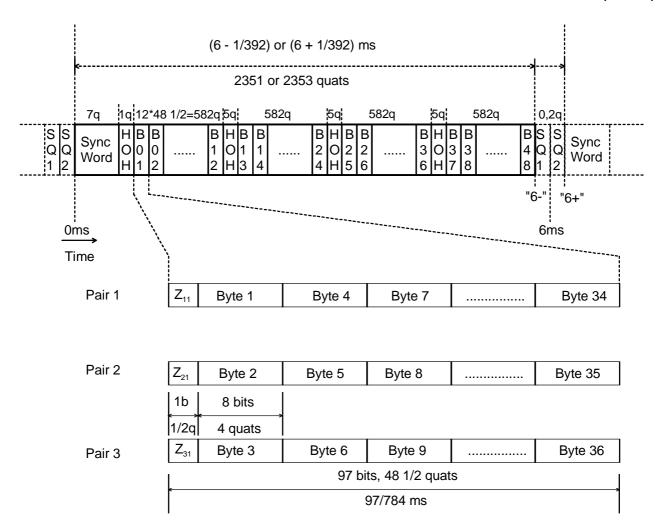

An individual HDSL transceiver system is a two wire bi-directional transceiver for metallic wires using the echo cancellation method. Three systems may be utilized, one transporting a bit rate of 784 kbit/s over each of three pairs used in parallel, a second with an increased bit rate of 1 168 kbit/s and two pairs in parallel only and a third with a more increased bit rate of 2 320 kbit/s on one pair only.

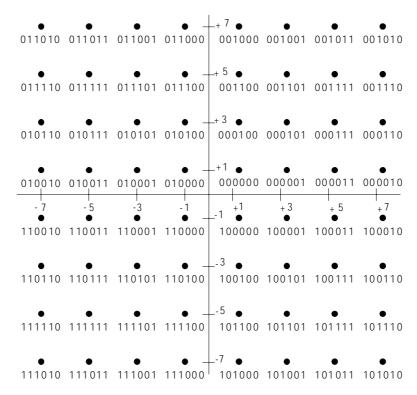

The line codes of systems specified in the present document are 2B1Q (2 Binary 1 Quaternary) and CAP (Carrierless Amplitude Phase modulation). Systems using a CAP line code are covered in annex B. Annex C summarizes the Committee T1 recommendation for the frame structure of 1 544 kbit/s applications. Only one of the line codes has to be realized in a transmission system.

The present document defines the common circuitry for combining and controlling one, two or three HDSL transceiver systems, depending on the bit rate of the transceiver system used, for the support of applications with a 2 048 kbit/s hierarchy. The common circuitry and the necessary number of HDSL transceiver systems form the HDSL core, which is independent from the different applications defined in the present document.

The applications of HDSL are determined by the functionality of the mapping and interface part, some of which are defined as follows:

- ISDN primary rate access digital section in accordance with ETS 300 233 [1];

- ONP leased line access D2048U based on ETS 300 246 [2] and ETS 300 247 [3];

- ONP leased line access D2048S based on ETS 300 418 [4] and ETS 300 419 [5];

- 2 Mbit/s access to the Synchronous Digital Hierarchy (SDH) via a TU-12.

The HDSL core may be used for applications that are not restrictive to the access portion of the network but this is outside the scope of the present document.

NOTE: If further applications are identified in future the present document may be enhanced to define the relevant interface and mapping requirements as far as these do not violate the specification of the HDSL core.

Special applications of the HDSL core or part of the HDSL core can be:

- fractional installation, which provides reduced access capability only by a reduced number of HDSL transceivers, to cater for an inexpensive system if the total capacity of 30 × 64 kbit/s is not needed;

- partial operation, which is the persistent operation of the operable HDSL transceiver systems when others become inoperable;

- fractional payload, e.g. H<sub>0</sub>-channel.

The bit-rate at the application interface will also be 2 048 kbit/s in these applications, but not all the time slots in the G.704 frame may be used, or there may be network specific interfaces used for these applications, the definition of which is outside the scope of the present document.

The present document does not specify all the requirements for the implementation of NTU, LTU or REG. It serves only to describe the functionality needed.

#### 2 References

The following documents contain provisions which, through reference in this text, constitute provisions of the present document.

- References are either specific (identified by date of publication, edition number, version number, etc.) or non-specific.

- For a specific reference, subsequent revisions do not apply.

- For a non-specific reference, the latest version applies.

- A non-specific reference to an ETS shall also be taken to refer to later versions published as an EN with the same

- number. ETS 300 233: "Integrated Services Digital Network (ISDN); Access digital section for ISDN [1] primary rate". [2] ETS 300 246 (1993): "Business Telecommunications (BT); Open Network Provision (ONP) technical requirements; 2 048 kbit/s digital unstructured leased line (D2048U) Network interface presentation". [3] ETS 300 247 (1993): "Business Telecommunications (BT); Open Network Provision (ONP) technical requirements; 2 048 kbit/s digital unstructured leased line (D2048U) Connection characteristics". [4] ETS 300 418 (1995): "Business Telecommunications (BTC); 2 048 kbit/s digital unstructured and structured leased lines (D2048U and D2048S); Network interface presentation". [5] ETS 300 419 (1995): "Business Telecommunications (BTC); 2 048 kbit/s digital structured leased lines (D2048S); Connection characteristics". [6] ETR 080 (1993): "Transmission and Multiplexing (TM); Integrated Services Digital Network (ISDN) basic rate access; Digital transmission system on metallic local lines". [7] ETS 300 011 (1992): "Integrated Services Digital Network (ISDN); Primary rate user-network interface; Layer 1 specification and test principles".

- [8] CCITT Fascicle I.3: "Definitions".

- [9] ITU-T Recommendation G.823: "The control of jitter and wander within digital networks which are based on the 2 048 kbit/s hierarchy".

- [10] ITU-T Recommendation G.826 (1993): "Error performance parameters and objectives for international, constant bit rate digital paths at or above the primary rate".

- ETS 300 019 (1992): "Equipment Engineering (EE); Environmental conditions and environmental [11] tests for telecommunications equipment".

- [12] ITU-T Recommendation 0.151: "Error performance measuring equipment operating at the primary rate and above".

- [13] EN 60950: "Safety of information technology equipment, including electrical business equipment".

- ITU-T Recommendation K.17: "Tests on power-fed repeaters using solid-state devices in order to [14] check the arrangement for protection from external interference".

- [15] ITU-T Recommendation K.20: "Resistibility of telecommunication switching equipment to overvoltages and overcurrents".

- [16] ITU-T Recommendation K.21: "Resistibility of subscriber's terminal to overvoltages and overcurrents".

| [17] | ETS 300 386-2: "Electromagnetic compatibility and Radio spectrum Matters (ERM); Telecommunication network equipment; ElectroMagnetic Compatibility (EMC) requirements; Part 2: Product family standard".                             |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [18] | ETS 300 386-1: "Equipment Engineering (EE); Telecommunication network equipment; Electro-Magnetic Compatibility (EMC) requirements; Part 1: Product family overview, compliance criteria and test levels".                           |

| [19] | ETS 300 166 (1993): "Transmission and Multiplexing (TM); Physical and electrical characteristics of hierarchical digital interfaces for equipment using the 2 048 kbit/s - based plesiochronous or synchronous digital hierarchies". |

| [20] | ETS 300 167 (1993): "Transmission and Multiplexing (TM); Functional characteristics of 2 048 kbit/s interfaces".                                                                                                                     |

| [21] | ISO 2110 (1991): "Information Technology - Data communication - 25-pole DTE/DCE interface connector and connect number assignments".                                                                                                 |

| [22] | ITU-T Recommendation G.707 (1995): "General Aspects of Digital Transmission Systems; Network Node Interface for the Synchronous Digital Hierarchy (SDH)".                                                                            |

| [23] | IEEE Transactions on Information Theory, Volume IT-33 (July 1984): "Rotationally Invariant Convolutional Coding with Expanded Signal Space - Part II: Nonlinear Codes" (Lee-Fang Wei).                                               |

| [24] | IEEE Journal on Selected Areas in Communication, Volume 9, No. 6 (August 1991): "Combined Trellis Coding and DFE Through Tomlinson Precoding" (R. L. Cupo et al).                                                                    |

| [25] | ANSI Committee T1 Technical Report No. 28 (February 1994): "A Technical Report on High Bit-Rate Digital Subscriber Lines (HDSL)".                                                                                                    |

| [26] | IEEE Transactions on Circuits and Systems Volume CAS-33 No. 10 (October 1986): "Multitone Signals with Low Crest Factor" (Stephen Boyd).                                                                                             |

| [27] | ETS 300 012: "Integrated Services Digital Network (ISDN); Basic user-network interface; Layer 1 specification and test principles".                                                                                                  |

| [28] | ETS 300 297: "Integrated Services Digital Network (ISDN); Access digital section for ISDN basic access".                                                                                                                             |

| [29] | ITU-T Recommendation Q.552: "Transmission characteristics at 2-wire analogue interfaces of digital exchanges".                                                                                                                       |

| [30] | ITU-T Recommendation G.711: "Pulse code modulation (PCM) of voice frequencies".                                                                                                                                                      |

| [31] | ITU-T Recommendation G.821: "Error performance of an international digital connection operating at a bit rate below the primary rate and forming part of an integrated services digital network".                                    |

# 3 Abbreviations

For the purposes of the present document, the following abbreviations apply:

| AIS   | Alarm Indication Signal                                                    |

|-------|----------------------------------------------------------------------------|

| BER   | Bit Error Ratio                                                            |

| BERTS | Bit Error Ratio Test Set                                                   |

| BT    | Bridged Tap (an unterminated twisted pair section bridged across the line) |

| CAP   | Carrierless Amplitude Phase modulation                                     |

| CRC   | Cyclic Redundancy Check                                                    |

| DC    | Direct Current                                                             |

| DLL   | Digital Local Line                                                         |

| eoc   | embedded operations channel                                                |

| EMC   | ElectroMagnetic Compatibility                                              |

HDSL High bit rate Digital Subscriber Line

HOH HDSL OverHead

ISDN-BA Integrated Services Digital Network Basic Access

ISDN-PRA Integrated Services Digital Network Primary Rate Access

IUT Implementation Under Test

LCL Longitudinal Conversion Loss

LFA Loss of Frame Alignment

LOS Loss of Signal

lsb least significant bit

LTU Line Termination Unit

msb most significant bit

MTIE Maximum Time Interval Error

NEXT Near End crosstalk

NNI Network Node Interface

NTU Network Termination Unit

ONP Open Network Provision

O&M Operation and Maintenance

ppm parts per million

PRBS Pseudo-Random Bit Sequence PSD Power Spectral Density

PSL Power Sum Loss REG REGenerator

REG-C NTU side of the regenerator REG-R LTU side of the regenerator

rms root mean square

SDH Synchronous Digital Hierarchy

TMN Telecommunications Management Network

TS Time slot

TU-12 Tributary Unit-12 UI Unit Interval

UNI User Network Interface UTC Unable To Comply VC-12 Virtual Container-12

2B1Q 2 Binary 1 Quaternary (line code)

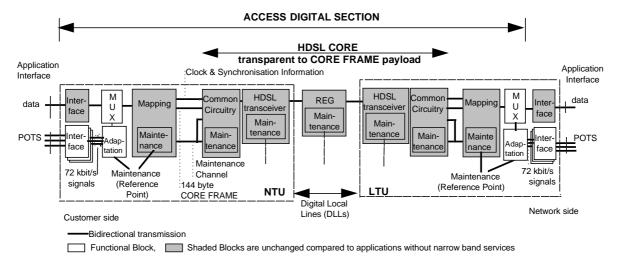

# 4 Reference configuration and functional description

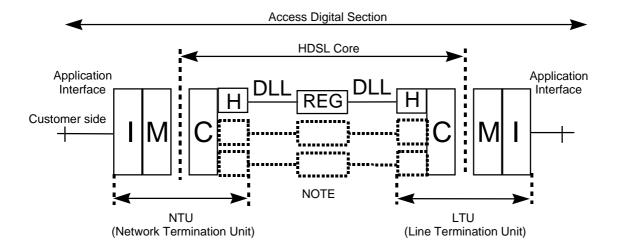

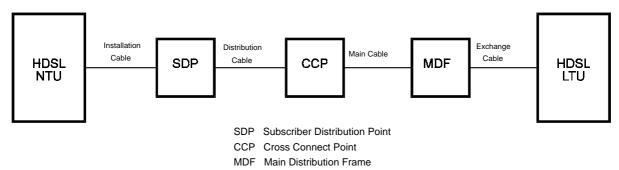

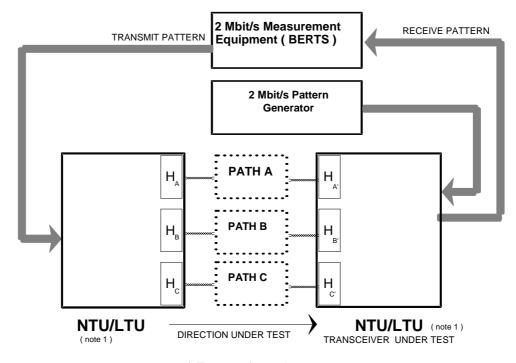

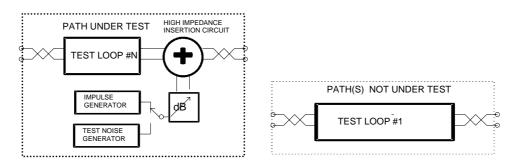

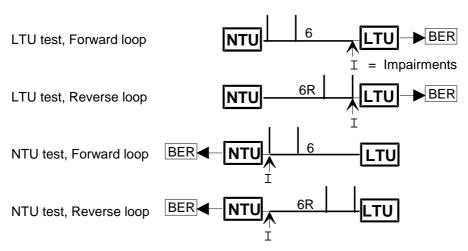

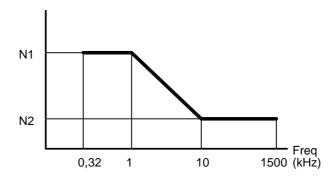

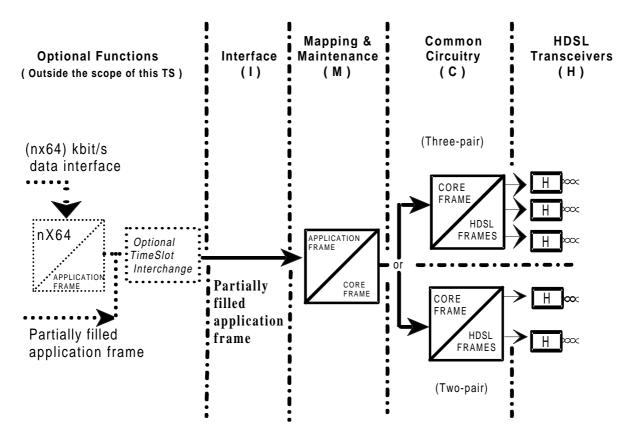

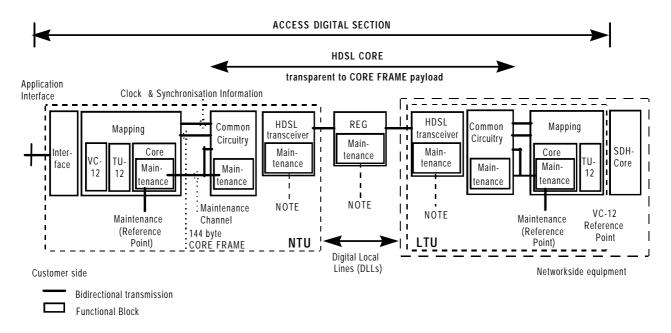

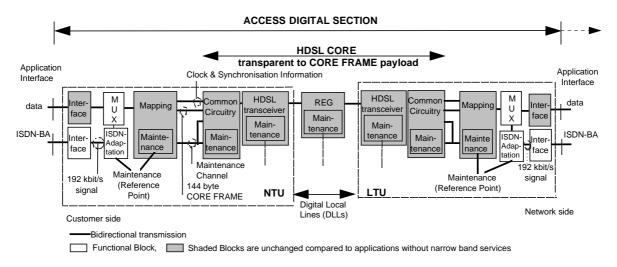

An access digital section which uses HDSL technology can be considered as a number of functional blocks, (see figure 1). Depending upon the HDSL transceiver (H) transmission rate, a fully equipped HDSL core consists of one 2 320 kbit/s, two 1 168 kbit/s or three 784 kbit/s HDSL transceiver pairs connected by Digital Local Lines (DLLs) (which are linked by some common circuitry (C). The HDSL core is application independent. Operation with a non-fully equipped HDSL core is also permitted.

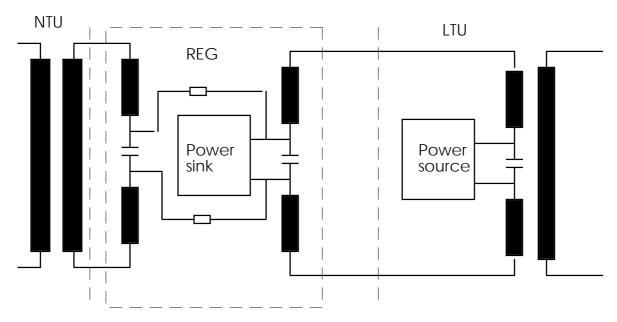

If enhanced transmission range is required the HDSL core may contain optional regenerators (REGs). The overall insertion loss of the HDSL core with regenerator shall be less than 1,8 times the value Y of the non-regenerated HDSL core. The regenerator may be inserted at any convenient intermediate point in the HDSL core with the limitation that the insertion loss of each part-DLL shall be less than 0,9 times Y. In addition there may be further restrictions in line length due to power feeding.

An application is defined by the interface (I) and mapping & maintenance (M) functionalities.

The functionalities at the exchange side constitute the Line Termination Unit (LTU) and act as master to the (slave) customer side functionalities, which collectively form the Network Termination Unit (NTU) and the REGs where applicable.

Description of functional blocks:

C = Common circuitry

I = Interface

DLL = Digital Local Line

H = HDSL transceiver

REG = Regenerator

NOTE: A fully equipped HDSL core consists of one, two or three H, REG and DLL combinations depending on HDSL transceiver data transmission rate. REGs are optional.

Figure 1: Access Digital Section employing HDSL technology (simplified configuration)

Throughout the present document, reference is made to the terms REG-C, REG-R and individual HDSL transmission systems. REG-R identifies functionalities located at the LTU side of the regenerator, REG-C identifies functionalities located at the NTU side of the regenerator.

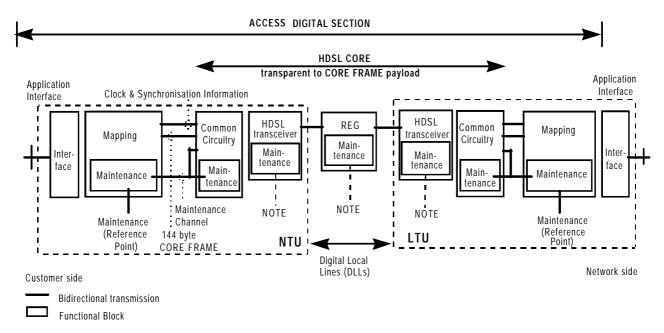

Figure 2 describes the maintenance and other communication functionalities more clearly.

NOTE: A fully equipped HDSL CORE consists of one, two or three H, REG, DLL combinations depending on HDSL transceiver data transmission rate. REGs are optional.

Figure 2: Access Digital Section employing HDSL technology (detailed configuration)

The information transmitted between the NTU side (slave side) and LTU side (master side) is handled as follows:

At the application interface (I), the data flow is grouped in **application frames** (e.g. 32 time slot ISDN primary rate frames, as specified in ETS 300 011 [7]).

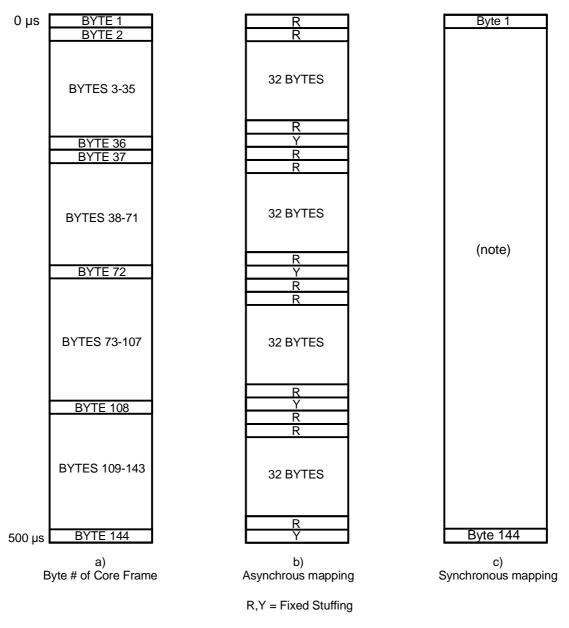

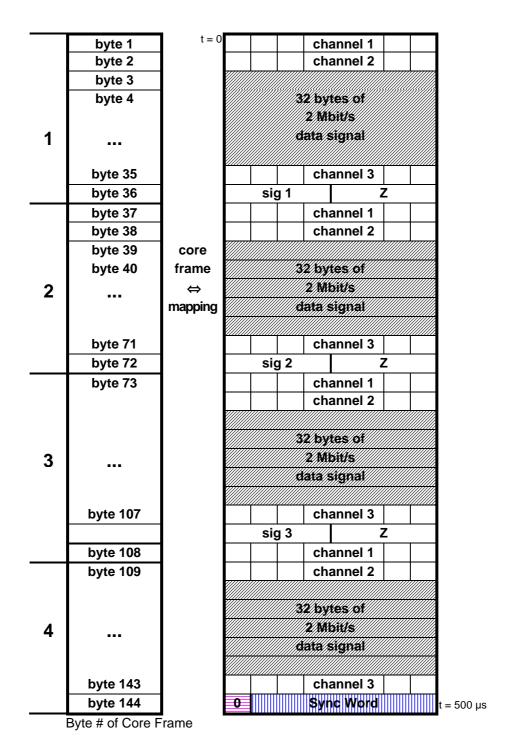

The mapping function (part of the M functional block) then takes the application frame and inserts it into a 144 byte **core frame**. (In some applications not all data bytes will contain valid information and may be set to idle patterns).

The core frame is then given to the common circuitry (C) where it is combined with any necessary alignment bits, maintenance bits and overhead bits, in order to be sent transparently in **HDSL frames** over the DLLs. The use of REGs is optional.

At the receiving side, data within the HDSL frames is multiplexed by the common circuitry to again form the core frame which is passed to the mapping function where it is mapped into the application frame and transmitted over the application interface (I).

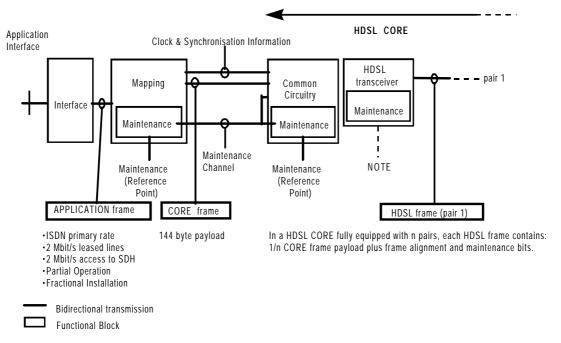

An overview of the different framing procedures can be found in figure 3.

NOTE: A fully equipped HDSL CORE consists of one, two or three H, REG, DLL combinations depending on HDSL transceiver data transmission rate. REGs are optional.

Figure 3: An overview of framing procedures

In addition, there may be maintenance and/or power feeding functions associated with the HDSL core for the support of failure identification, localization and HDSL start-up control, however the presentation of this information at the maintenance reference point is outside the scope of the present document.

The specification of the HDSL core is aimed at interoperability of two equipments from different vendors.

# 5 HDSL core specification

### 5.1 Functions

The functions listed below are necessary for the correct operation of the HDSL core.

| Functions related to the HDSL core                     | LTU NTU/<br>REG |  |

|--------------------------------------------------------|-----------------|--|

| Transparent transport of core frames (144 bytes)       | <>              |  |

| Stuffing and destuffing                                | <>              |  |

| CRC-6 procedures and transmission error detection      | <>              |  |

| Error reporting                                        | <>              |  |

| Failure detection                                      | <>              |  |

| Failure reporting                                      | <>              |  |

| Bit timing                                             | <>              |  |

| Frame alignment                                        | <>              |  |

| HDSL transceiver autonomous start-up control           | >               |  |

| Loopback control and co-ordination                     | >               |  |

| Mapping of core frames into HDSL frames                | <>              |  |

| Control of maintenance channel                         | <>              |  |

| Synchronization and co-ordination of HDSL transceivers | >               |  |

| Identification of pairs                                | <>              |  |

| Correction of pair identification                      | (see note)      |  |

NOTE: Correction of pairs is a function of the NTU.

| Functions related to power feeding | LTU NTU/ |

|------------------------------------|----------|

|                                    | REG      |

| Remote power feeding (optional)    | >        |

| Wetting current (optional)         | >        |

# 5.1.1 Transparent transport of core frames

This function provides for the bi-directional transmission of the core frames with 144 bytes over one, two or three parallel HDSL transceiver systems connected by separate pairs.

# 5.1.2 Stuffing and destuffing

This function provides for the synchronization of the application data clock to the HDSL transceiver system clock, by means of adding zero or two stuffing quats per HDSL frame.

# 5.1.3 CRC-6 procedures and transmission error detection

This function provides for error performance monitoring of the HDSL transceiver systems in each HDSL frame.

# 5.1.4 Error reporting

This function provides for the reporting of errors detected by means of CRC-6 procedure.

#### 5.1.5 Failure detection

This function provides for the detection of failures in the HDSL transceiver system.

# 5.1.6 Failure reporting

This function provides for the reporting of failures detected in the HDSL transceiver systems by means of messages in the maintenance channel realized i.e. by HDSL frame overhead bits.

### 5.1.7 Bit timing

This function provides bit (signal element) timing to enable the HDSL transceiver systems to recover information from the aggregate bit stream.

### 5.1.8 Frame alignment

This function provides information to enable the HDSL transceiver systems to recover the HDSL frame and the HDSL frame overhead.

# 5.1.9 HDSL transceiver autonomous start-up control

This function provides for the recovering of the operational state after first powering or break down of the HDSL transceiver systems.

# 5.1.10 Loopback control and co-ordination

This function provides for the activation and release of loopbacks in the LTU, the REG and the NTU.

# 5.1.11 Mapping between core frames and HDSL frames

This function provides for the mapping between the 144 bytes core frame and the HDSL frame(s).

### 5.1.12 Control of the maintenance channel

This function provides for the control of the maintenance channel formed by the HDSL frame overhead bits.

# 5.1.13 Synchronization and co-ordination of HDSL transceivers

This function provides for the synchronization of the HDSL transceiver systems, the equalization of different signal delays on the pairs and the correct sequence of the signals coming from the separate pairs.

# 5.1.14 Identification of pairs

This function provides for the marking of the pairs at the LTU/NTU by means of two or three Z bits per pair to enable the correct identification of the pairs.

# 5.1.15 Correction of pair identification

This function provides for the realignment of the identification of pairs if an unintentional interchange of pairs has occurred and was detected by the NTU.

# 5.1.16 Remote power feeding

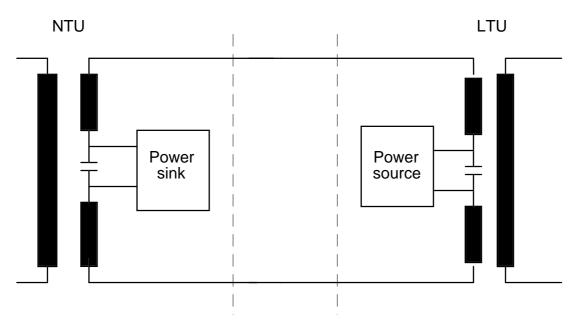

This optional function provides for remote power feeding of either the NTU (if no REG is provided) or the REG from the LTU via the pairs.

# 5.1.17 Wetting current

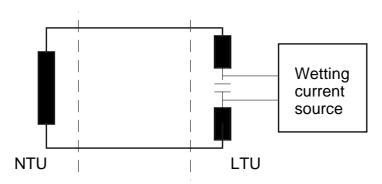

This optional function provides for feeding of a low current on the pairs to mitigate the effect of corrosion of contacts.

### 5.2 Transmission medium

# 5.2.1 Description

The transmission medium over which the digital transmission system is expected to operate is the local line distribution network.

A local line distribution network employs cables of pairs to provide services to customers.

In a local line distribution network, customers are connected to the local exchange via local lines.

A metallic local line is able to simultaneously carry bi-directional digital information in the appropriate HDSL format.

To simplify the provision of HDSL, a digital transmission system shall be capable of satisfactory operation over the majority of metallic local lines without requirement of any special conditioning. In order to permit the use of HDSL transmission systems on the maximum possible number of local lines, the restrictions imposed by HDSL requirements are kept to the minimum necessary to guarantee acceptable operation.

# 5.2.2 Minimum Digital Local Line (DLL) requirements for HDSL applications

- No loading coils;

- Only twisted pair or quad cable;

- No additional shielding necessary;

- When bridged taps are present, the maximum number shall be limited to 2 and the length of each to 500 m.

# 5.2.3 DLL physical characteristics

A DLL is constructed of one or more cable sections that are spliced or interconnected together.

The distribution or main cable is structured as follows:

- cascade of cable sections of different diameters and lengths;

- up to two bridged taps (BTs) may exist at various points in installation and distribution cables.

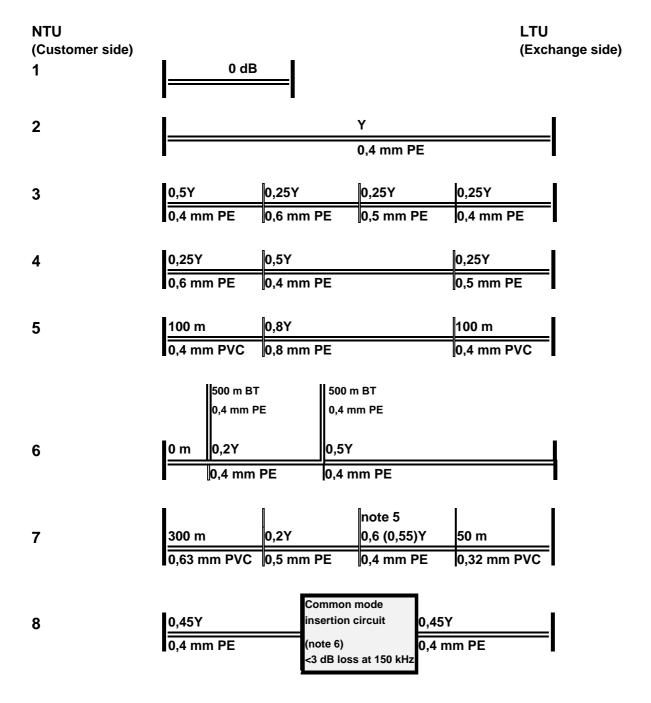

A general description of the DLL physical model is shown in figure 4 and typical examples of cable characteristics based on ETR 080 [6] are given in table 1.

Figure 4: DLL physical model

Table 1: Cable characteristics

|             |                                                  | Exchange cable         | Main cal       | ole   | Dis                      | stribution cable    | Installation cable     |  |

|-------------|--------------------------------------------------|------------------------|----------------|-------|--------------------------|---------------------|------------------------|--|

| Wi          | re diameter                                      | 0,5; 0,6;              | 0,3 to 1       | ,4    |                          | 0,3 to 1,4          | 0,4; 0,5;              |  |

|             | (mm)                                             | 0,32; 0,4              |                |       |                          |                     | 0,6; 0,8;              |  |

| , ,         |                                                  |                        |                |       |                          |                     | 0,9; 0,63              |  |

|             | Structure                                        | SQ (B) or TP (L)       | SQ (B) or T    | P (L) | S                        | Q (B) or TP (L)     | SQ or TP or UP         |  |

| N           | Maximum                                          | 1 200                  | 2 400 (0,4     | mm)   |                          | 600 (0,4 mm)        | 2 (aerial)             |  |

| nun         | nber of pairs                                    |                        | 4 800 (0,32    | mm)   |                          |                     | 600 (in house)         |  |

| Ir          | nstallation                                      |                        | undergro       | und   |                          | underground         | aerial (drop)          |  |

|             |                                                  |                        | in ducts       |       |                          | or aerial           | in ducts (in house)    |  |

| Capacitance |                                                  | 55 to 120              | 25 to 60       |       |                          | 25 to 60            | 35 to 120              |  |

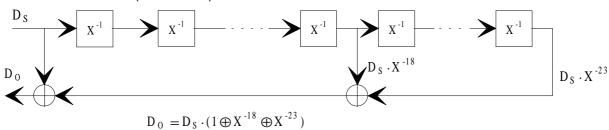

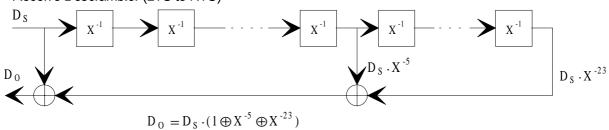

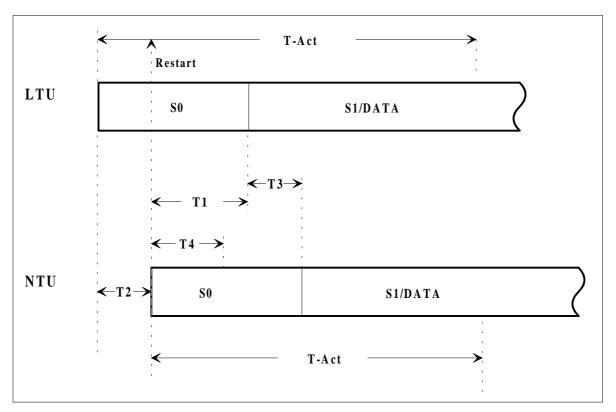

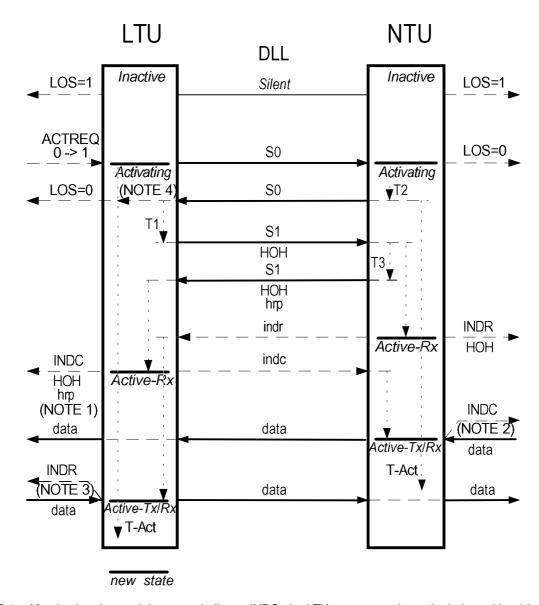

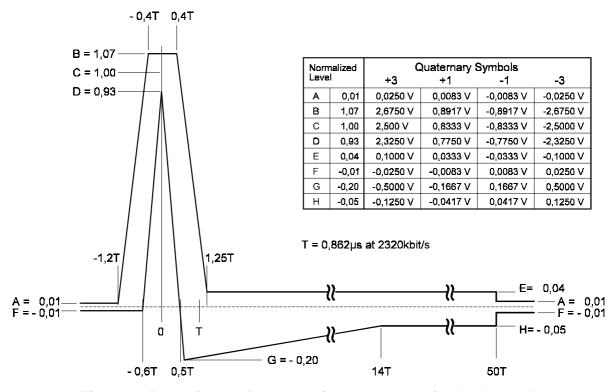

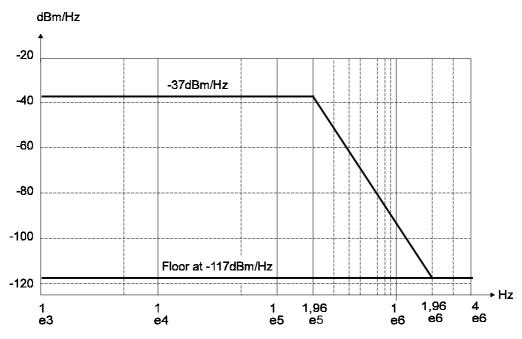

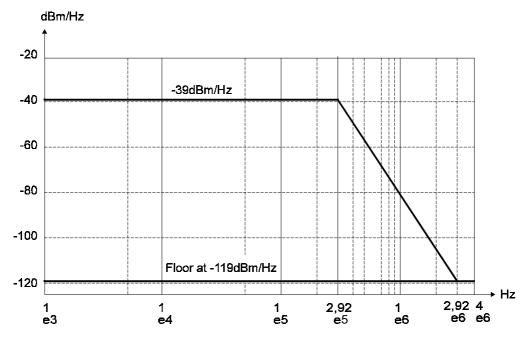

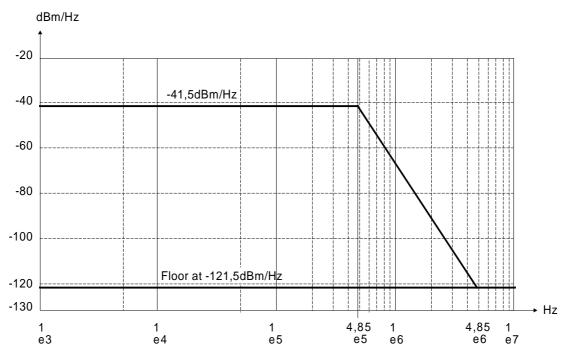

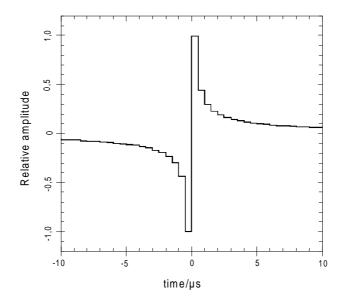

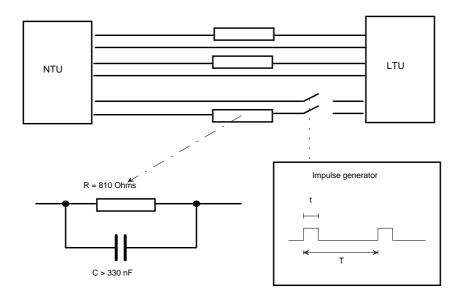

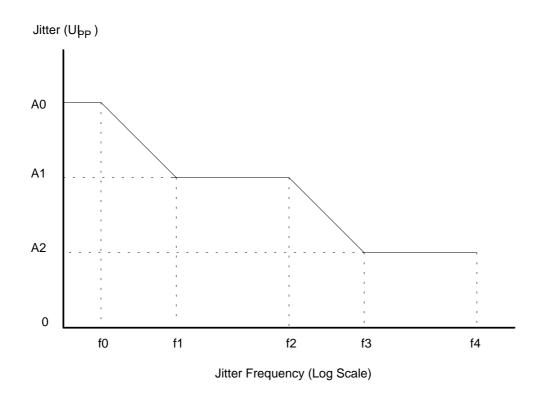

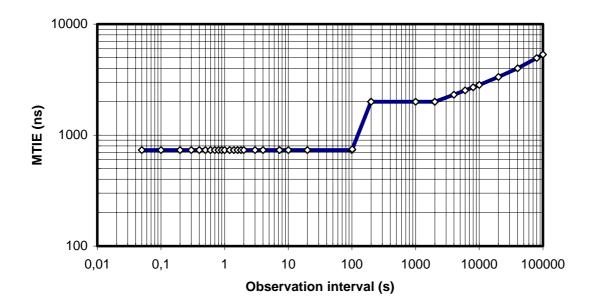

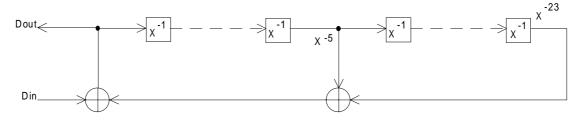

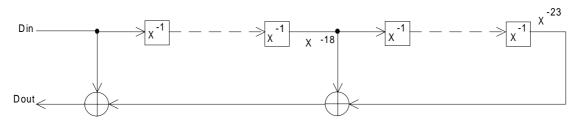

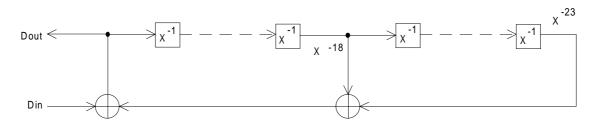

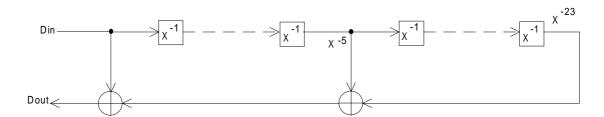

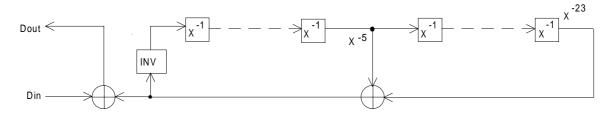

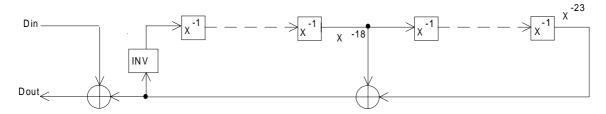

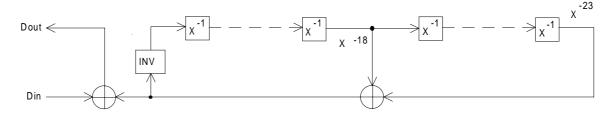

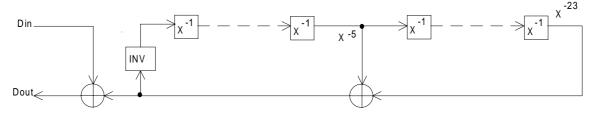

| (nF/k       | km at 800 Hz                                     | )                      |                |       |                          |                     |                        |  |