# Final draft ETSI EN 300 462-2-1 V1.2.1 (2002-01)

European Standard (Telecommunications series)

Transmission and Multiplexing (TM);

Generic requirements for synchronization networks;

Part 2-1: Synchronization network architecture

based on SDH networks

#### Reference

#### REN/TM-01092

#### Keywords

architecture, SDH, synchronization, transmission

#### **ETSI**

650 Route des Lucioles F-06921 Sophia Antipolis Cedex - FRANCE

Tel.: +33 4 92 94 42 00 Fax: +33 4 93 65 47 16

Siret N° 348 623 562 00017 - NAF 742 C Association à but non lucratif enregistrée à la Sous-Préfecture de Grasse (06) N° 7803/88

#### Important notice

Individual copies of the present document can be downloaded from: <u>http://www.etsi.org</u>

The present document may be made available in more than one electronic version or in print. In any case of existing or perceived difference in contents between such versions, the reference version is the Portable Document Format (PDF). In case of dispute, the reference shall be the printing on ETSI printers of the PDF version kept on a specific network drive within ETSI Secretariat.

Users of the present document should be aware that the document may be subject to revision or change of status.

Information on the current status of this and other ETSI documents is available at

<a href="http://portal.etsi.org/tb/status/status.asp">http://portal.etsi.org/tb/status/status.asp</a></a>

If you find errors in the present document, send your comment to: editor@etsi.fr

#### Copyright Notification

No part may be reproduced except as authorized by written permission. The copyright and the foregoing restriction extend to reproduction in all media.

© European Telecommunications Standards Institute 2002. All rights reserved.

# Contents

| Intell                     | ectual Property Rights                                                                                                             | 4        |  |  |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|

| Forev                      | word                                                                                                                               | 4        |  |  |

| 1                          | Scope                                                                                                                              | 5        |  |  |

| 2                          | References                                                                                                                         | 5        |  |  |

| 3<br>3.1<br>3.2            | Definitions and abbreviations                                                                                                      |          |  |  |

| 4                          | Synchronization methods                                                                                                            | 6        |  |  |

| 5<br>5.1<br>5.2<br>5.3     | Functional description of clock types  Primary Reference Clock (PRC)  Synchronization Supply Unit (SSU)  SDH Equipment Clock (SEC) | 7<br>7   |  |  |

| 6                          | Synchronization network architecture                                                                                               | 9        |  |  |

| 7                          | Synchronization modes                                                                                                              | 10       |  |  |

| 8                          | Synchronization network reference chain                                                                                            | 11       |  |  |

| 9<br>9.1<br>9.2            | Synchronization network evolution                                                                                                  | 13       |  |  |

| 10<br>10.1<br>10.2<br>10.3 | Synchronization network robustness  General  Trail redundancy  Synchronization status message                                      | 13<br>13 |  |  |

| 10.4                       | Management                                                                                                                         |          |  |  |

|                            | ex A (informative): Bibliography                                                                                                   |          |  |  |

## Intellectual Property Rights

IPRs essential or potentially essential to the present document may have been declared to ETSI. The information pertaining to these essential IPRs, if any, is publicly available for **ETSI members and non-members**, and can be found in ETSI SR 000 314: "Intellectual Property Rights (IPRs); Essential, or potentially Essential, IPRs notified to ETSI in respect of ETSI standards", which is available from the ETSI Secretariat. Latest updates are available on the ETSI Web server (http://webapp.etsi.org/IPR/home.asp).

Pursuant to the ETSI IPR Policy, no investigation, including IPR searches, has been carried out by ETSI. No guarantee can be given as to the existence of other IPRs not referenced in SR 000 314 (or the updates on the ETSI Web server) which are, or may be, or may become, essential to the present document.

#### **Foreword**

This European Standard (Telecommunications series) has been produced by ETSI Technical Committee Transmission and Multiplexing (TM), and is now submitted for the ETSI standards One-step Approval Procedure.

The present document has been produced to provide requirements for synchronization networks that are compatible with the performance requirements of digital networks. It is one of a family of documents covering various aspects of synchronization networks.

The present document is part 2-1 of a multi-part deliverable covering generic requirements for synchronization networks, as identified below:

- Part 1-1: "Definitions and terminology for synchronization networks";

- Part 2-1: "Synchronization network architecture based on SDH networks";

- Part 3-1: "The control of jitter and wander within synchronization networks";

- Part 4-1: "Timing characteristics of slave clocks suitable for synchronization supply to Synchronous Digital Hierarchy (SDH) and Plesiochronous Digital Hierarchy (PDH) equipment";

- Part 4-2: "Timing characteristics of slave clocks suitable for synchronization supply to Synchronous Digital Hierarchy (SDH) and Plesiochronous Digital Hierarchy (PDH) equipment; Implementation Conformance Statement (ICS) proforma specification";

- Part 5-1: "Timing characteristics of slave clocks suitable for operation in Synchronous Digital Hierarchy (SDH) equipment";

- Part 6-1: "Timing characteristics of primary reference clocks";

- Part 6-2: "Timing characteristics of primary reference clocks; Implementation Conformance Statement (ICS) proforma specification";

- Part 7-1: "Timing characteristics of slave clocks suitable for synchronization supply to equipment in local node applications".

Part 2-1 has been revised in several sections with regard to the work done in EG 201 793 [7] and to reflect the present status of synchronization networks.

| Proposed national transposition dates                                                  |                                 |  |  |

|----------------------------------------------------------------------------------------|---------------------------------|--|--|

| Date of latest announcement of this EN (doa):                                          | 3 months after ETSI publication |  |  |

| Date of latest publication of new National Standard or endorsement of this EN (dop/e): | 6 months after doa              |  |  |

| Date of withdrawal of any conflicting National Standard (dow):                         | 6 months after doa              |  |  |

## 1 Scope

The present document specifies the architectural principles that should be applied for the design of synchronization networks that are suitable for the synchronization of Synchronous Digital Hierarchy (SDH) and Plesiochronous Digital Hierarchy (PDH) networks. It supports the construction of synchronization networks that support both the short term stability requirements of SDH networks and the long term stability requirements of digital switching networks (e.g. PSTN) connected to the SDH network. It applies to the design of new synchronization networks. It does not characterize existing synchronization networks based on PDH networks.

The present document specifies the rules and architectural principles the implementation of synchronization networks shall follow. This information is supplemented by EG 201 793 [7]. It gives guidance and examples how these rules and architectural principles can be used to set up a synchronization scheme for various network configurations.

#### 2 References

The following documents contain provisions which, through reference in this text, constitute provisions of the present document.

- References are either specific (identified by date of publication and/or edition number or version number) or non-specific.

- For a specific reference, subsequent revisions do not apply.

- For a non-specific reference, the latest version applies.

- [1] ETSI EN 300 462-1-1: "Transmission and Multiplexing (TM); Generic requirements for synchronization networks; Part 1-1: Definitions and terminology for synchronization networks".

- [2] ETSI EN 300 462-3-1: "Transmission and Multiplexing (TM); Generic requirements for synchronization networks; Part 3-1: The control of jitter and wander within synchronization networks".

- [3] ETSI EN 300 147: "Transmission and Multiplexing (TM); Synchronous Digital Hierarchy (SDH); Multiplexing structure".

- [4] ETSI EN 300 462-5-1: "Transmission and Multiplexing (TM); Generic requirements for synchronization networks; Part 5-1: Timing characteristics of slave clocks suitable for operation in Synchronous Digital Hierarchy (SDH) equipment".

- [5] ETSI EN 300 462-6-1: "Transmission and Multiplexing (TM); Generic requirements for synchronization networks; Part 6-1: Timing characteristics of primary reference clocks".

- [6] ETSI EN 300 462-4-1: "Transmission and Multiplexing (TM); Generic requirements for synchronization networks; Part 4-1: Timing characteristics of slave clocks suitable for synchronization supply to Synchronous Digital Hierarchy (SDH) and Plesiochronous Digital Hierarchy (PDH) equipment".

- [7] ETSI EG 201 793: "Transmission and Multiplexing (TM); Synchronization network engineering".

- [8] ETSI EN 300 462-7-1: "Transmission and Multiplexing (TM); Generic requirements for synchronization networks; Part 7-1: Timing characteristics of slave clocks suitable for synchronization supply to equipment in local node applications".

- [9] ETSI EN 300 417-6-1: "Transmission and Multiplexing (TM); Generic requirements of transport functionality of equipment; Part 6-1: Synchronization layer functions".

#### 3 Definitions and abbreviations

#### 3.1 Definitions

For the purposes of the present document, the terms and definitions given in EN 300 462-1-1 [1] apply.

#### 3.2 Abbreviations

For the purposes of the present document, the abbreviations given in EN 300 462-1-1 [1] and the following apply:

ADM Add Drop Multiplexer

AIS Alarm Indication Signal

NE Network Element

OTN Optical Transport Network

PDH Plesiochronous Digital Hierarchy

ppm parts per million

PRC Primary Reference Clock

PSTN Public Switched Telephone Network SASE Stand-Alone Synchronization Equipment

SDH Synchronous Digital Hierarchy

SEC SDH Equipment Clock

SETG SDH Equipment Timing Generator

SETS SDH Equipment Timing Source

SSU Synchronization Supply Unit

SSM Synchronization Status Message

STM-N Synchronous Transport Module N

## 4 Synchronization methods

Master-slave synchronization is appropriate for synchronizing SDH networks and the following material offers guidance on using this method.

Master-slave synchronization uses a hierarchy of clocks in which each level of the hierarchy is synchronized with reference to a higher level. There are four qualities of clock in the synchronization hierarchy shown below:

Primary Reference Clock (PRC): see EN 300 462-6-1 [5];

slave clock (transit node): see EN 300 462-4-1 [6];

slave clock (local node): see EN 300 462-7-1 [8];

SDH Equipment Clock (SEC): see EN 300 462-5-1 [4].

The PRC is the highest quality hierarchical clock and the SEC is the lowest quality clock. Higher quality clocks shall not be synchronized by lower quality clocks in holdover mode, but clocks in holdover mode can be used to synchronize clocks of the same quality. There are limits on the number of clocks, which can be connected in a synchronization distribution trail (see clause 8). Clock reference signals are distributed between levels of the hierarchy via a distribution network, which may use the facilities of the transport network. The transport network may contain SECs. The distribution of timing between hierarchical node clocks shall be performed using a method, which avoids intermediate pointer processing. Two possible methods are as follows:

- a) recover timing from a received Synchronous Transport Module N (STM-N) signal (this avoids the unpredictable effect of a pointer adjustment on the downstream slave clock);

- b) derive timing from a synchronization trail that is not supported by a SDH network.

The master-slave method uses a single-ended synchronization technique with the slave clock selecting the synchronization trail to be used as its reference and changing to an alternative if the original trail fails. This is a unilateral control scheme.

## 5 Functional description of clock types

#### 5.1 Primary Reference Clock (PRC)

The PRC is a logical function conforming to the requirements of EN 300 462-6-1 [5]. It generates the master clock for a network or part of a network.

The PRC equipment may either:

- implement its own free running oscillator (e.g. Caesium tube oscillator); or

- be a slave clock being synchronized to a high accuracy free running clock by terrestrial or satellite radio signals (e.g. GPS).

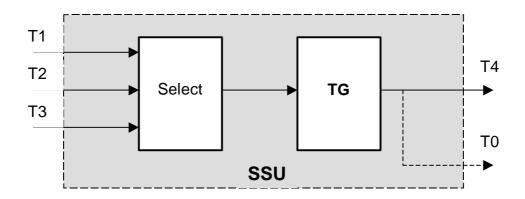

## 5.2 Synchronization Supply Unit (SSU)

A SSU is a logical function conforming to the requirements of EN 300 462-4-1 [6] or EN 300 462-7-1 [8]. It:

- accepts synchronization inputs from a number of sources;

- selects one of these inputs;

- filters this sources clock removing jitter and short term wander;

- distributes the resultant clock to other elements within a node.

In the event of failure or degradation of all synchronization reference inputs, the SSU will use a high quality internal oscillator to maintain the stability and accuracy of the frequency of its output signals (holdover mode).

A functional diagram of the SSU is shown in figure 1.

The physical implementation of this function may be integrated within a SDH network element, integrated within Public Switched Telephone Network (PSTN) switch, or as a stand-alone unit (a Stand-Alone Synchronization Equipment, (SASE)).

Key:

T0: Internal system clock.

T1: Timing reference signal derived from STM-N input.

T2: Timing reference signal derived from 2 048 kbit/s input.

T3: Timing reference signal derived from 2 048 kHz or 2 048 kbit/s with SSM. External reference timing signal (2 048 kHz or 2 048 kbit/s with SSM).

TG: Timing Generator.

NOTE 1: Where the SSU is integrated within a SDH Network Element (NE), T0 should be provided.

NOTE 2: It may be possible to force the SSU into a free-running condition.

Figure 1: The SSU clock function

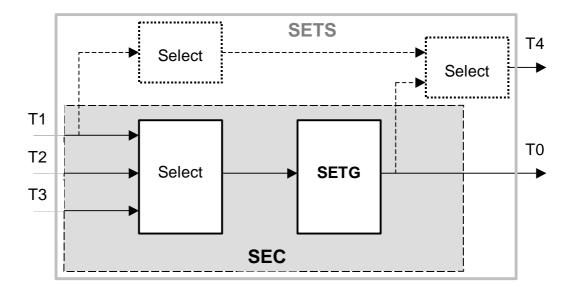

## 5.3 SDH Equipment Clock (SEC)

The SEC is a logical function of input signal selection and clock filtering. The selection function conforms to the requirements of EN 300 417-6-1 [5] and the filtering function conforms to the requirements of EN 300 462-5-1 [4]. The SEC:

- accepts synchronization inputs from a number of sources within that element;

- selects one of these inputs;

- filters this source's clock.

In the event of failure of all synchronization reference inputs the SEC shall use its own internal clock as the active clock source (holdover mode).

The SEC is specified to be used in SDH equipment as the timing source for the outgoing SDH STM-N interfaces of the NE. A functional diagram of the SEC is shown in figure 2.

Key:

T0: Internal system clock.

T1: Timing reference signal derived from STM-N input.

T2: Timing reference signal derived from 2 048 kbit/s input.

T3: Timing reference signal derived from 2 048 kHz or 2 048 kbit/s with SSM. T4: External reference timing signal (2 048 kHz or 2 048 kbit/s with SSM).

SETG: SDH Equipment Timing Generator.

NOTE 1: The SEC is a functional subset of the SETS as described in EG 201 793 [7].

NOTE 2: It may be possible to force the SEC into a free running condition.

Figure 2: The SEC clock function

## 6 Synchronization network architecture

The architecture employed in SDH requires the timing of all network element clocks to be traceable to a PRC. This clause details the target architecture for SDH network synchronization. Evolutionary aspects are discussed in clause 10.

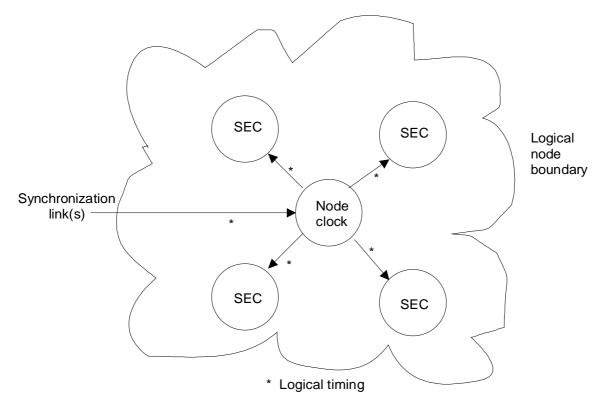

The distribution of synchronization can be categorized into intra-node within nodes containing a SSU and inter-node as follows:

- a) Intra-node distribution within nodes containing a SSU conforms to a logical star topology. All lower level network element clocks within a node boundary derive timing from the highest hierarchical clock level in the node. An exception may be made for the network element clock that carries the synchronization trail to the SSU. An example illustrating this exception is given in the following:

- Assume that network timing has to be distributed along a ring structure where each node, in addition to the ring ADM, contains an SSU. By considering the ring ADMs to belong to a synchronization trail rather than to the nodes where they are located, excessive cascading of SSUs can be prevented. All other outputs from each node may be timed from the local SSU.

- Apart from these network elements, only the clock of the highest hierarchical level in the node will recover timing from synchronization links from other nodes.

- The synchronization signals between the SSU and SECs will normally be 2 048 kHz or 2 048 kbit/s signals as described in EG 201 793 [7].

- Timing is distributed from network elements within the boundary to network elements beyond the boundary via the SDH transmission medium. The relationship between clocks within a node is shown in figure 3.

NOTE 1: Network nodes can be configured without an SSU. Examples are given in EG 201 793 [7].

NOTE 2: Any interface used for synchronization of SDH NE should comply with the requirements given in EN 300 462-3-1 [2].

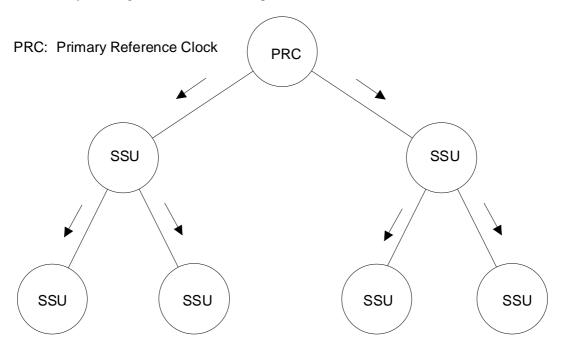

Figure 3: Synchronization network architecture for intra-node distribution

b) Inter-node distribution conforms to a tree-like topology and enables all the nodes in the SDH network to be synchronized. The hierarchical relationship between clocks is shown in figure 4. With this architecture, it is important for the correct operation of the synchronization network that clocks of lower hierarchical level only accept timing from clocks of the same or higher hierarchical level and that timing loops are avoided. To ensure that this relationship is preserved, the distribution network shall be designed such that, even under fault conditions, only valid higher level references are presented to hierarchical clocks.

Figure 4: Synchronization network architecture for inter-node distribution

Clocks of a lower hierarchical level shall have a pull-in range which ensures that they can automatically acquire and lock to the timing signal generated by the same or higher level clock that they are using as a reference.

Phase reference information is transferred between synchronization nodes by means of a synchronization trail. When a trail becomes disabled then the node clock shall select another reference from a set of valid alternatives. When none exist, the node clock shall enter holdover mode.

The synchronization trail is provided by one or more synchronization link connections each supported by a synchronized PDH trail or a SDH multiplex section trail or each synchronization trail derived directly from a PRC. When the distribution network is based on SDH, one or more link connections each supported by a multiplex section trail are recommended to conform to the requirement given in clause 4. The sub-network connections (switches) in the synchronization trail need to be set to maintain only valid hierarchical relationships between clocks.

## 7 Synchronization modes

Four synchronization modes can be identified. These are:

- synchronous;

- pseudo-synchronous;

- plesiochronous;

- asynchronous.

In synchronous mode, all clocks in the network will be traceable to a single PRC. Pointer adjustments will only occur randomly. This is the normal mode of operation within a single operator's domain or within a sub-network of a single operator's domain.

In pseudo-synchronous mode (see note), not all clocks in the network will have timing traceable to the same PRC. However, each PRC will comply with EN 300 462-6-1 [5] and, therefore, pointer adjustments will be generated in the network elements at the boundary between equipment synchronized to different PRC. This is the normal mode of operation for the international and inter-operator network.

NOTE: In a large single operator domain where more than one PRC is used, this mode of operation may be employed.

In plesiochronous mode, the synchronization trail and the fallback alternatives to one or more clocks in the network will have been disabled. The clock will enter holdover or free-run mode. If synchronization is lost to a gateway SDH network element performing asynchronous mapping, the frequency offset and drift of the clock will cause pointer adjustments at the next SDH network element in the SDH network connection, these pointer adjustments will propagate to the end of the network connection. If synchronization is lost to the last network element in the SDH network connection (or the penultimate network element in the case where the last one is slaved, e.g. consists of a loop-timed multiplexer), there will also be pointer adjustments to cater for at the SDH network output. However, if the synchronization failure occurs at an intermediate network element, this will not result in a net pointer movement at the final output gateway network element provided the input gateway network element remains synchronized to the same PRC. Pointer movement at the intermediate network element will be corrected by the next network element in the connection, which is still synchronized.

Asynchronous mode corresponds to the situation where large frequency offsets occur. The SDH network is not required to maintain traffic when the clock accuracy is less than that of a SEC. A clock accuracy of  $\pm 20$  ppm is required to send an Alarm Indication Signal (AIS) (applicable for regenerators and any other SDH equipment where loss of all synchronization inputs implies loss of all traffic).

## 8 Synchronization network reference chain

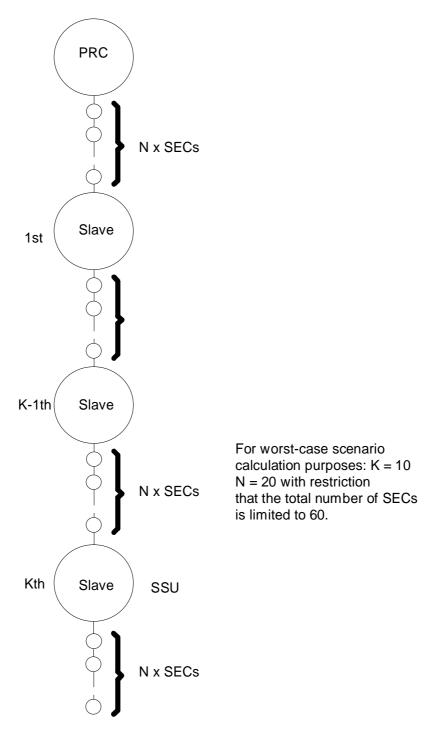

The synchronization network reference chain is shown in figure 5. Timing is distributed via master-slave synchronization from the PRC to all clocks in the chain. The longest chain should not exceed K SSUs with up to N SECs interconnecting any two SSUs.

In general, the quality of timing will deteriorate as the number of synchronized clocks in tandem increases and hence for practical synchronization network design, the number of network elements in tandem should be minimized. However to determine synchronization clock requirements, the values for the worst case synchronization reference chain are K=10, N=20 with the total number of SECs limited to 60. The value of N is limited by the quality of timing required by the last network element in the chain and ensures the short-term stability mask of EN 300 462-3-1 [2] is met.

The values of K and N have been derived from theoretical calculations and practical measurements are required for their verification.

NOTE: It is possible for the PRC to be connected directly to an SSU without an intervening SEC.

Figure 5: Synchronization network reference chain

## 9 Synchronization network evolution

#### 9.1 SDH networks

The SDH is designed to operate in pseudo-synchronous mode. The network elements can be integrated into existing synchronization hierarchies.

During the evolution of the network to SDH, the network synchronization plan will have to be altered to accommodate the SDH network elements. This requires careful planning to ensure that network synchronization is not jeopardized.

When SDH equipment is initially introduced, the gateway network element shall be timed from either the PRC or an existing SSU. Timing within the SDH network should follow the master-slave approach.

If the SDH network introduction results in PDH islands, steps shall be taken so that synchronization links supported by primary rate PDH trails do not transit the SDH network. This requires a reconfiguration of the synchronization architecture since all synchronization links transiting the SDH network shall be supported on SDH multiplex section trails.

Where a network is completely SDH based, the synchronization distribution will be determined solely by the synchronization network reference chain.

Interworking between SASEs and SDH NEs is described in annex B of EG 201 793 [7].

#### 9.2 Optical Transport Networks

The payload transport performance in the Optical Transport Networks (OTN) is timing transparent in the sense, that wander added to the payload does not exceed the limits as defined in EN 300 462 -3-1 [2]. Thus the basic STM-N synchronization trails and the STM-N synchronization trails over OTUk trails are of equivalent synchronization performance.

## 10 Synchronization network robustness

#### 10.1 General

Synchronization network robustness can be achieved through different and complementary methods:

- by careful design of the synchronization network, utilizing redundant synchronization trails where possible;

- by automatic reconfiguration capability in SDH sub-networks using the SSM protocol;

- by synchronization network management supporting reconfiguration at the overall network level.

#### 10.2 Trail redundancy

It is preferable that all SSUs and SECs are able to recover timing from at least two synchronization trails. The slave clock shall reconfigure to recover timing from an alternative trail if the original trail fails. Where possible synchronization trails should be provided over diversely routed paths.

In the event of a failure of synchronization distribution, all network elements will seek to recover timing from the highest hierarchical level clock source available. To effect this, both SSUs and SECs may have to reconfigure and recover timing from one of their alternate synchronization trails. This will ensure that a SEC rarely enters holdover or free-run mode. However, it may have to recover timing from a SSU, which is itself in holdover if this is the highest hierarchical level source available to it. In order to indicate faults in the synchronization distribution network across non-SDH interfaces, the use of a squelching function or AIS may be required.

## 10.3 Synchronization status message

Within SDH sub-networks, timing is distributed between network nodes via a number of network elements with clocks of lower hierarchical level. A timing quality marking scheme, the Synchronization Status Message (SSM) is provided to allow selection and confirmation of the highest quality synchronization trail available to SECs (in normal operation and during synchronization failure conditions) through a priority/quality level algorithm described in EN 300 417-6-1 [9].

The quality marking scheme provides an indication of the quality of the timing using a status messaging approach The SSM is transported in the section overhead (S1 byte) as described in EN 300 147 [3] and EN 300 417-6-1 [9]. For outputs used for timing distribution using SSM, the status message shall reflect the selected reference.

Where timing quality markers are used in a meshed network, potential problems have been identified. It shall therefore be possible to restrict the links used for synchronization. Network synchronization planners are reminded that careful consideration is needed when using timing quality markers.

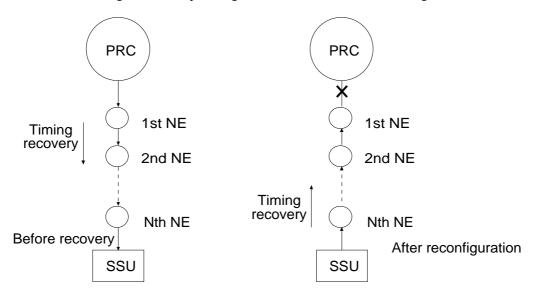

To provide an example of a reconfiguration, if the first network element from the PRC loses its synchronization trail from the PRC, it should reconfigure and accept timing from the SSU. This is shown in figure 6.

Figure 6: Reconfiguration example

#### 10.4 Management

The management system is an important component in ensuring the robustness of the synchronization network utilizing its ability to actively monitor the actual working state of the synchronization network and of its different components. Such a management system covers configuration of equipment, network topology, fault detection, troubleshooting, Synchronization management can be restricted to PRC and SSU in an independent system or integrated in the SDH network management system. If it is extended to SECs, then it needs to have the capability to communicate to the SDH NEs either directly or by means of the SDH network management system.

Synchronization management may allow remote actions on synchronization equipment and network topology, So consequences of change to the network or an equipment configuration, should be carefully considered to avoid any degradation of synchronization distribution such as timing loops. As far as possible, no disturbance of the normal timing distribution should be introduced.

It is also important that access to synchronization network management should be secured by different enabling levels from the mere reading of event logs to network and equipment configuration.

# Annex A (informative): Bibliography

ITU-T Recommendation G.783: "Characteristics of synchronous digital hierarchy (SDH) equipment functional blocks".

# History

| Document history |              |                             |                                        |  |  |

|------------------|--------------|-----------------------------|----------------------------------------|--|--|

| V1.1.1           | May 1998     | Publication                 |                                        |  |  |

| V1.1.2           | August 1999  | Publication                 |                                        |  |  |

| V1.2.1           | January 2002 | One-step Approval Procedure | OAP 20020531: 2002-01-30 to 2002-05-31 |  |  |

|                  |              |                             |                                        |  |  |

|                  |              |                             |                                        |  |  |