## ETSI EN 300 396-2 V1.2.0 (2002-03)

European Standard (Telecommunications series)

Terrestrial Trunked Radio (TETRA); Technical requirements for Direct Mode Operation (DMO); Part 2: Radio aspects

# Reference REN/TETRA-08063 Keywords air interface, radio, tetra

#### **ETSI**

650 Route des Lucioles F-06921 Sophia Antipolis Cedex - FRANCE

Tel.: +33 4 92 94 42 00 Fax: +33 4 93 65 47 16

Siret N° 348 623 562 00017 - NAF 742 C Association à but non lucratif enregistrée à la Sous-Préfecture de Grasse (06) N° 7803/88

#### Important notice

Individual copies of the present document can be downloaded from: <u>http://www.etsi.org</u>

The present document may be made available in more than one electronic version or in print. In any case of existing or perceived difference in contents between such versions, the reference version is the Portable Document Format (PDF). In case of dispute, the reference shall be the printing on ETSI printers of the PDF version kept on a specific network drive within ETSI Secretariat.

Users of the present document should be aware that the document may be subject to revision or change of status.

Information on the current status of this and other ETSI documents is available at

<a href="http://portal.etsi.org/tb/status/status.asp">http://portal.etsi.org/tb/status/status.asp</a></a>

If you find errors in the present document, send your comment to:  $\underline{\text{editor} @\, \text{etsi.fr}}$

#### **Copyright Notification**

No part may be reproduced except as authorized by written permission. The copyright and the foregoing restriction extend to reproduction in all media.

© European Telecommunications Standards Institute 2002. All rights reserved.

## Contents

| Intelle            | ectual Property Rights                             | t  |

|--------------------|----------------------------------------------------|----|

| Forew              | vord                                               | e  |

| 1                  | Scope                                              | 7  |

| 2                  | References                                         | 7  |

| 3                  | Definitions and abbreviations                      |    |

| 3.1                | Definitions                                        |    |

| 3.2                | Abbreviations                                      | 8  |

| 4                  | Radio aspects                                      | 9  |

| 4.1                | Introduction                                       |    |

| 4.2                | Set of logical channels                            |    |

| 4.3                | Reference configuration                            |    |

| 4.4                | Error control schemes                              |    |

| 4.5                | Timeslot structure                                 |    |

| 4.5.1              | Framing structure                                  |    |

| 4.5.2              | Timeslots and bursts                               |    |

| 4.5.3              | Mapping of logical channels onto physical channels |    |

| 4.6                | Coding, interleaving and scrambling                |    |

| 4.7                | Modulation                                         |    |

| 4.8                | Transmission and reception                         |    |

| 4.9                | Other radio-related functions                      |    |

| 4.10               | Performance                                        | 11 |

| 5                  | Modulation                                         | 12 |

| 5.1                | Introduction                                       |    |

| 5.2                | Modulation type                                    |    |

| 5.3                | Modulation rate                                    | 12 |

| 5.4                | Modulation symbol definition                       |    |

| 5.5                | Modulated signal definition                        |    |

| 5.6                | Modulation filter definition                       |    |

| 5.7                | Modulation block diagram                           | 14 |

| 6                  | Radio transmission and reception.                  |    |

| 6.1                | Introduction                                       |    |

| 6.2                | Frequency bands and channel arrangement            |    |

| 6.3                | Reference test planes                              |    |

| 6.4                | Transmitter characteristics                        |    |

| 6.4.1              | Output power                                       |    |

| 6.4.2              | Power classes                                      |    |

| 6.4.3              | Unwanted conducted emissions                       |    |

| 6.4.3.1<br>6.4.3.2 |                                                    |    |

| 6.4.3.2            |                                                    |    |

| 6.4.3.2            | 6 · · · · · · · · · · · · · · · · · · ·            |    |

| 6.4.3.3            |                                                    |    |

| 6.4.3.3            |                                                    |    |

| 6.4.3.3            |                                                    |    |

| 6.4.3.4            |                                                    |    |

| 6.4.3.5            |                                                    |    |

| 6.4.4              | Unwanted radiated emissions                        |    |

| 6.4.5              | Radio frequency tolerance                          |    |

| 6.4.6              | RF output power time mask                          |    |

| 6.4.7              | Transmitter intermodulation attenuation            |    |

| 6.4.7.1            |                                                    |    |

| 6.4.7.2            |                                                    |    |

| 6.5                | Receiver characteristics                           |    |

| 6.5.1     | Blocking characteristics                                                                        | 20 |

|-----------|-------------------------------------------------------------------------------------------------|----|

| 6.5.1.1   | Definition                                                                                      | 20 |

| 6.5.1.2   | Specification                                                                                   | 20 |

| 6.5.2     | Spurious response rejection                                                                     | 20 |

| 6.5.2.1   | Definition                                                                                      | 20 |

| 6.5.2.2   | Specification                                                                                   | 20 |

| 6.5.3     | Intermodulation response rejection                                                              |    |

| 6.5.3.1   | Definition                                                                                      |    |

| 6.5.3.2   | Specification                                                                                   |    |

| 6.5.4     | Unwanted conducted emissions                                                                    |    |

| 6.5.4.1   | Definition                                                                                      |    |

| 6.5.4.2   | Specification                                                                                   |    |

| 6.5.5     | Unwanted radiated emissions                                                                     |    |

| 6.6       | Transmitter/receiver performance                                                                |    |

| 6.6.1     | Modulation accuracy                                                                             |    |

| 6.6.1.1   | Ideal case                                                                                      |    |

|           |                                                                                                 |    |

| 6.6.1.2   | Vector error magnitude requirement at symbol time                                               |    |

| 6.6.2     | Receiver performance                                                                            |    |

| 6.6.2.1   | Nominal error rates                                                                             |    |

| 6.6.2.2   | Dynamic reference sensitivity                                                                   |    |

| 6.6.2.3   | Receiver performance at reference interference ratios                                           |    |

| 6.6.2.4   | Static reference sensitivity                                                                    |    |

| 6.6.2.5   | MS receiver performance for acquisition of synchronization burst                                |    |

| 6.6.3     | Propagation conditions                                                                          |    |

| 6.6.3.1   | Tap-gain process types                                                                          |    |

| 6.6.3.2   | DM propagation models                                                                           | 26 |

| 7 R       | adio sub-system synchronization                                                                 | 27 |

|           |                                                                                                 |    |

| 7.1       | Introduction                                                                                    |    |

| 7.2       | Definitions and general requirements for synchronization of DM-MSs                              |    |

| 7.3       | Timebase counters                                                                               |    |

| 7.3.1     | Definition of counters                                                                          |    |

| 7.3.2     | Relationship between the counters                                                               |    |

| 7.4       | Requirements for the frequency reference source of DM mobiles                                   |    |

| 7.5       | Requirements for the synchronization of a slave DM mobile                                       |    |

| 7.6       | Synchronization requirements for a master MS operating on channel B in frequency efficient mode | 29 |

| 8 C1      | hannel coding and scrambling                                                                    | 20 |

| 8.1       | Introduction                                                                                    |    |

| 8.2       | General                                                                                         |    |

|           | Interfaces in the error control structure                                                       |    |

| 8.2.1     |                                                                                                 |    |

| 8.2.2     | Notation                                                                                        |    |

| 8.2.3     | Definition of error control codes                                                               |    |

| 8.2.3.1   | 16-state Rate-Compatible Punctured Convolutional (RCPC) codes                                   |    |

| 8.2.3.1.1 | Encoding by the 16-state mother code of rate 1/4                                                |    |

| 8.2.3.1.2 | Puncturing of the mother code                                                                   |    |

| 8.2.3.1.3 | Puncturing scheme of the RCPC code of rate 2/3                                                  |    |

| 8.2.3.1.4 | Puncturing scheme of the RCPC code of rate 292/432                                              |    |

| 8.2.3.1.5 | Puncturing scheme of the RCPC code of rate 148/432                                              |    |

| 8.2.3.2   | (K <sub>1</sub> + 16, K <sub>1</sub> ) block code                                               | 33 |

| 8.2.4     | Definition of interleaving schemes                                                              | 33 |

| 8.2.4.1   | Block interleaving                                                                              |    |

| 8.2.4.2   | Interleaving over N blocks                                                                      |    |

| 8.2.5     | Definition of scrambling                                                                        |    |

| 8.2.5.1   | Scrambling method                                                                               |    |

| 8.2.5.2   | Scrambling sequence                                                                             |    |

| 8.3       | Error control schemes                                                                           |    |

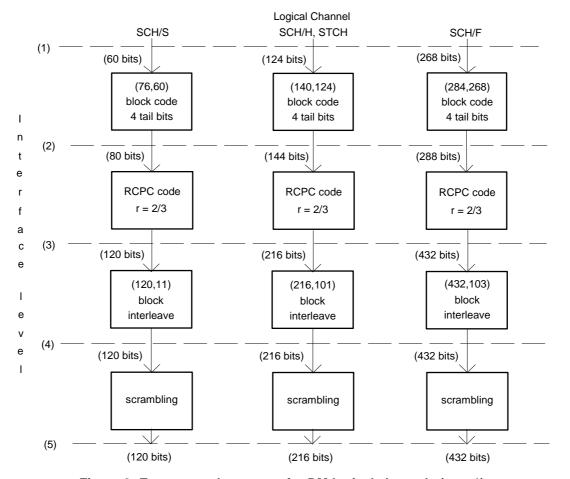

| 8.3.1     | Signalling channels                                                                             |    |

| 8.3.1.1   |                                                                                                 |    |

|           | Synchronization Signalling CHannel (SCH/S)                                                      |    |

| 8.3.1.2   | Half-slot Signalling CHannel (SCH/H) and Stealing CHannel (STCH)                                |    |

| 8.3.1.3   | Full-slot Signalling CHannel (SCH/F)                                                            |    |

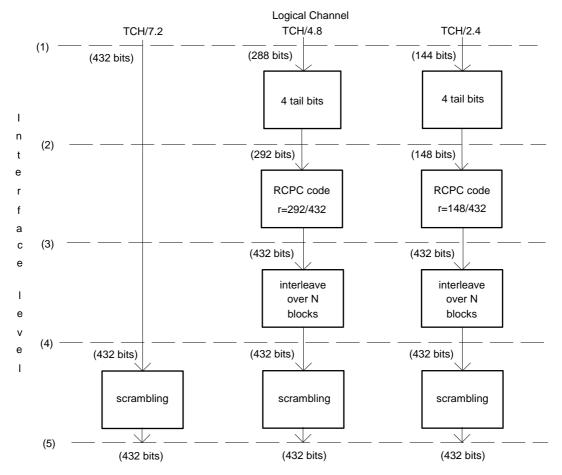

| 8.3.2     | Traffic channels in circuit switched mode                                                       | 37 |

| 8.3.2.1  | Traffic channel, net rate = 7,2 kbit/s (TCH/7,2) | 37 |

|----------|--------------------------------------------------|----|

| 8.3.2.2  | Traffic channel, net rate = 4,8 kbit/s (TCH/4,8) | 38 |

| 8.3.2.3  | Traffic channel, net rate = 2,4 kbit/s (TCH/2,4) | 39 |

| 8.3.2.4  | Speech Traffic Channel, full slot (TCH/S)        | 39 |

| 8.3.2.5  | Speech Traffic Channel, half slot (TCH/S)        | 40 |

| 9 (      | Channel multiplexing for DM                      | 40 |

| 9.1      | Introduction                                     |    |

| 9.2      | Logical channels                                 |    |

| 9.2.1    | Logical channels hierarchy                       |    |

| 9.2.2    | Traffic channels                                 |    |

| 9.2.3    | Control channels                                 |    |

| 9.2.3.1  | General                                          |    |

| 9.2.3.2  | Linearization CHannel (LCH)                      |    |

| 9.2.3.3  | Signalling CHannel (SCH)                         |    |

| 9.2.3.4  | STealing CHannel (STCH)                          |    |

| 9.3      | The physical resource                            |    |

| 9.3.1    | General                                          |    |

| 9.3.2    | Timeslots                                        | 42 |

| 9.3.3    | DM frame                                         |    |

| 9.3.4    | Multiframe                                       | 42 |

| 9.4      | Physical channels                                | 42 |

| 9.4.1    | General                                          | 42 |

| 9.4.2    | Bursts                                           | 42 |

| 9.4.2.1  | General                                          | 42 |

| 9.4.2.2  | Modulation symbol numbering                      | 42 |

| 9.4.2.3  | Modulation bit numbering                         | 42 |

| 9.4.2.4  | Burst timing                                     | 43 |

| 9.4.3    | Type of bursts                                   |    |

| 9.4.3.1  | General                                          |    |

| 9.4.3.2  | Modulation bits allocation                       |    |

| 9.4.3.2. | ,                                                |    |

| 9.4.3.2. | ,                                                |    |

| 9.4.3.2. |                                                  |    |

| 9.4.3.3  | Burst fields                                     |    |

| 9.4.3.3. | 1                                                |    |

| 9.4.3.3. | 1 2                                              |    |

| 9.4.3.3. |                                                  |    |

| 9.4.3.3. | $\mathcal{C}$                                    |    |

| 9.4.3.3. | 3                                                |    |

| 9.4.3.3. |                                                  |    |

| 9.4.4    | DM-MS multiple slot transmission                 |    |

| 9.4.5    | General mapping of logical channels              | 47 |

| 10       | Radio subsystem link control                     | 47 |

| 10.1     | Introduction                                     | 47 |

| 10.2     | RF power control                                 | 47 |

| 10.3     | Radio link measurements                          | 47 |

| 10.3.1   | Signal strength                                  |    |

| 10.3.2   | Signal quality                                   | 47 |

| Histor   | y                                                | ЛQ |

| THOUT    | y                                                | 40 |

## Intellectual Property Rights

IPRs essential or potentially essential to the present document may have been declared to ETSI. The information pertaining to these essential IPRs, if any, is publicly available for **ETSI members and non-members**, and can be found in ETSI SR 000 314: "Intellectual Property Rights (IPRs); Essential, or potentially Essential, IPRs notified to ETSI in respect of ETSI standards", which is available from the ETSI Secretariat. Latest updates are available on the ETSI Web server (http://webapp.etsi.org/IPR/home.asp).

Pursuant to the ETSI IPR Policy, no investigation, including IPR searches, has been carried out by ETSI. No guarantee can be given as to the existence of other IPRs not referenced in ETSI SR 000 314 (or the updates on the ETSI Web server) which are, or may be, or may become, essential to the present document.

#### **Foreword**

Part 10:

This European Standard (Telecommunications series) has been produced by ETSI Project Terrestrial Trunked Radio (TETRA), and is now submitted for the ETSI standards One-step Approval Procedure.

The present document is part 2 of a multi-part deliverable covering the Terrestrial Trunked Radio (TETRA); Technical requirements for Direct Mode Operation (DMO), as identified below:

Part 1: "General network design"; Part 2: "Radio aspects"; Part 3: "Mobile Station to Mobile Station (MS-MS) Air Interface (AI) protocol"; Part 4: "Type 1 repeater air interface"; Part 5: "Gateway air interface"; Part 6: "Security"; Part 7: "Type 2 repeater air interface"; Part 8: "Protocol Implementation Conformance Statement (PICS) proforma specification"; Part 9: "Service and Description Language (SDL) model";

"Managed Direct Mode Operation (M-DMO)".

| Proposed national transposition dates                                                  |                                 |  |

|----------------------------------------------------------------------------------------|---------------------------------|--|

| Date of latest announcement of this EN (doa):                                          | 3 months after ETSI publication |  |

| Date of latest publication of new National Standard or endorsement of this EN (dop/e): | 6 months after doa              |  |

| Date of withdrawal of any conflicting National Standard (dow):                         | 6 months after doa              |  |

## 1 Scope

EN 300 396 defines the TErrestrial Trunked RAdio system (TETRA) Direct Mode Operation (DMO). It specifies the basic air interface, the interworking between Direct Mode (DM) groups via repeaters, and interworking with the TETRA Voice plus Data (V+D) system via gateways. It also specifies the security aspects in TETRA DMO, and the intrinsic services that are supported in addition to the basic bearer and teleservices.

The present document applies to the TETRA DMO Mobile Station - Mobile Station (MS - MS) air interface and contains the specifications of the physical layer according to the OSI seven layer reference model.

It establishes the TETRA DM radio aspects (layer 1 and lower MAC):

- it defines and specifies the modulation;

- it defines and specifies the radio transmission and reception;

- it defines and specifies the synchronization;

- it defines and specifies the channel coding;

- it defines and specifies the channel multiplexing;

- it defines and specifies the control over the radio link.

## 2 References

The following documents contain provisions which, through reference in this text, constitute provisions of the present document.

- References are either specific (identified by date of publication and/or edition number or version number) or non-specific.

- For a specific reference, subsequent revisions do not apply.

- For a non-specific reference, the latest version applies.

- [1] ETSI ETS 300 113 (all parts): "Radio Equipment and Systems (RES); Land mobile service; Technical characteristics and test conditions for radio equipment intended for the transmission of data (and speech) and having an antenna connector".

- [2] ETSI ETS 300 396-3: "Terrestrial Trunked Radio (TETRA); Technical requirements for Direct Mode Operation (DMO); Part 3: Mobile Station to Mobile Station (MS-MS) Air Interface (AI) protocol".

- [3] ETSI ETS 300 395-2: "Terrestrial Trunked Radio (TETRA); Speech codec for full-rate traffic channel; Part 2: TETRA codec".

## 3 Definitions and abbreviations

## 3.1 Definitions

For the purposes of the present document, the following terms and definitions apply:

Bit Error Ratio (BER): ratio of the bits wrongly received to all bits received in a given logical channel

call transaction: all of the functions associated with a complete unidirectional transmission of information during a call

NOTE: A call is made up of one or more call transactions. In a simplex call these call transactions are sequential.

**Direct Mode Operation (DMO):** mode of simplex operation where mobile subscriber radio units may communicate using radio frequencies which may be monitored by, but which are outside the control of, the TETRA V+D network

NOTE: Direct Mode Operation is performed without intervention of any base station.

**Direct Mode Mobile Station (DM-MS):** physical grouping that contains all of the mobile equipment that is used to obtain TETRA DM services

NOTE: For synchronization purposes, Direct Mode Mobile Stations can have one of two status levels:

- **master:** if the DM-MS is either active in a call transaction transmitting traffic or control data, or is reserving the channel by means of channel reservation signalling and hence is **providing** synchronization information to the channel;

- **slave:** if the DM-MS is receiving traffic and/or signalling and hence is **deriving** synchronization information from the channel.

**DM channel:** specific grouping of timeslots in the DM multiplex structure related to a particular DM RF carrier (i.e. DM frequency)

NOTE: The grouping may not always be fixed, but in DMO when operating in frequency efficient mode as an example, there are two DM channels, identified by the letters A and B.

**frequency efficient mode:** mode of operation where two independent DM communications are supported on a single RF carrier

NOTE: In frequency efficient mode the two DM channels are identified as channel A and channel B.

logical channel: generic term for any distinct data path

NOTE: Logical channels are considered to operate between logical endpoints.

**Message Erasure Rate (MER):** ratio of the messages detected as wrong by the receiver to all messages received in a given logical channel

normal mode: mode of operation where only one DM communication is supported on an RF carrier

**Probability of Undetected Erroneous Message (PUEM):** limit ratio of the erroneous messages detected as right by the receiver to all messages received in a given logical channel

quarter symbol number: timing of quarter symbol duration 125/9 µs within a burst

simplex: mode of working in which information can be transferred in both directions but not at the same time

timebase: device which determines the timing state of signals transmitted by a Direct Mode Mobile Station

timeslot number: counter indicating the timing of timeslots within a DMO frame

useful part of a burst: part of the burst between and including the symbol time of SN0 and the symbol time of SNmax, with SN0 and SNmax as defined in clause 9 of EN 300 396-2

#### 3.2 Abbreviations

For the purposes of the present document, the following abbreviations apply:

AI Air Interface

BER Bit Error Ratio

BN Bit Number

DLB Direct mode Linearization Burst

DLL Data Link Layer

DM-MS Direct Mode Mobile Station

DMO Direct Mode Operation

DNB Direct mode Normal Burst

DQPSK Differential Quaternary Phase Shift Keying

DSB Direct mode Synchronization Burst

FN Frame Number

LCH Linearization CHannel

MER Message Erasure Rate

mod modulo (base for counting)

MS Mobile Station

PACQ Probability of synchronization burst ACQuisition PUEM Probability of Undetected Erroneous Message

QN Quarter symbol Number

RCPC Rate-Compatible Punctured Convolutional

RF Radio Frequency **RMS** Root Mean Square **SCH** Signalling CHannel Symbol Number SN STCH STealing CHannel Traffic CHannel TCH Timeslot Number TN V+DVoice plus Data

## 4 Radio aspects

#### 4.1 Introduction

This clause is an introduction to the radio aspects of the TETRA DMO standard. It consists of a general description of the organization of the radio-related functions with reference to the clauses where each part is specified in detail. Furthermore, it introduces the reference configuration that will be used throughout the present document.

## 4.2 Set of logical channels

The radio subsystem provides a certain number of logical channels as defined in clause 9. The logical channels represent the interface between the protocol and the radio.

## 4.3 Reference configuration

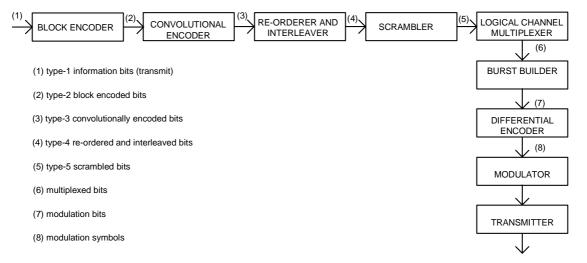

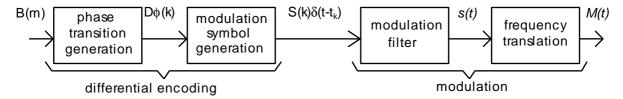

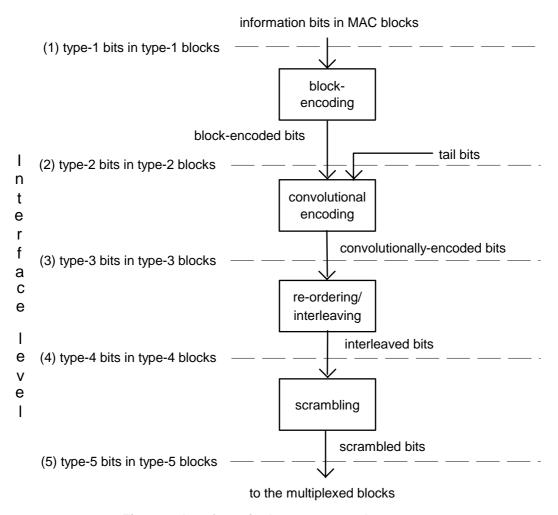

For the purpose of elaborating the specification of the radio-related functions, a reference configuration of the transmission chain is used, as shown in figure 1. Only the transmission part is specified, the receiver being specified only via the overall performance requirements. With reference to this configuration, the clauses address the following functional units:

- clause 5: differential encoding and modulation;

- clause 6: characteristics of transmitter and receiver;

- clause 8: coding, reordering and interleaving, and scrambling;

- clause 9: burst building and logical channel multiplexing;

- clause 10: radio link measurements.

This reference configuration also defines a number of points of vocabulary in relation to the names of bits at different levels in the configuration.

Figure 1: Reference configuration

#### 4.4 Error control schemes

The different error control schemes are described in detail in clause 8.

#### 4.5 Timeslot structure

The carrier separation is 25 kHz.

The basic radio resource is a timeslot lasting 14,167 ms (85/6 ms) and transmitting information at a modulation rate of 36 kbit/s. This means that the timeslot duration, including guard and ramping times, is 510 bit (255 symbol) durations.

The following clauses briefly introduce the structures of multiframes, frames, timeslots and bursts, as well as the mapping of the logical channels onto the physical channels. The appropriate specifications are found in clause 9.

## 4.5.1 Framing structure

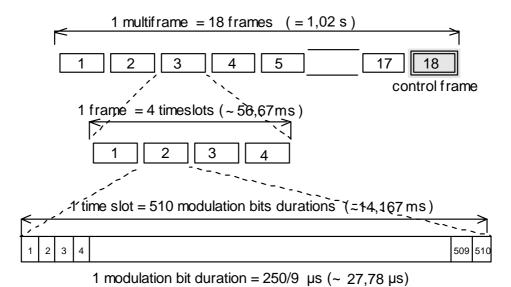

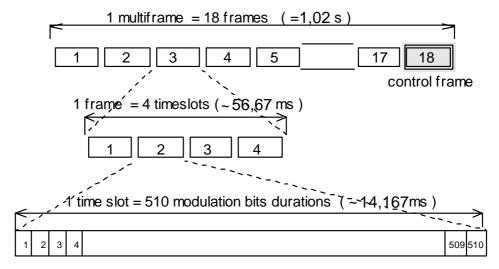

A diagrammatic representation of the framing structure is shown in figure 2.

Figure 2: DM framing structure

One multiframe is subdivided into 18 frames, and has a duration of 1,02 s. The eighteenth frame in a multiframe is a control frame.

One frame is subdivided into 4 timeslots, and has a duration of  $170/3 \approx 56,67$  ms.

#### 4.5.2 Timeslots and bursts

The timeslot is a time interval of  $85/6 \approx 14,167$  ms, which corresponds to 255 symbol durations.

The physical contents of a timeslot is carried by a burst. There are three different types of bursts, as defined in clause 9.

#### 4.5.3 Mapping of logical channels onto physical channels

The mapping of the logical channels onto the physical channels, according to the mode of operation, is defined in clause 9.

## 4.6 Coding, interleaving and scrambling

The coding, interleaving and scrambling schemes associated with each logical channel are specified in clause 8.

#### 4.7 Modulation

The modulation scheme is  $\pi/4$ -DQPSK (Differential Quaternary Phase-Shift Keying) with root-raised cosine modulation filter and a roll-off factor of 0,35. The modulation rate is 36 kbit/s. This scheme is specified in detail in clause 5.

## 4.8 Transmission and reception

The modulated stream is transmitted on a radio frequency carrier.

The specific RF channels, together with the requirements on the transmitter and the receiver characteristics are specified in clause 6.

DM-MS power classes are defined in clause 6.

## 4.9 Other radio-related functions

Transmission involves other functions. These functions, which may necessitate the handling of specific protocols, are the radio subsystem synchronization, and the radio subsystem link control.

The synchronization incorporates:

- frequency and time acquisition by the receiver;

- adjustment of the timebase in the DM-MS.

The requirements on synchronization are specified in clause 7.

#### 4.10 Performance

Under typical urban fading conditions the quality threshold for full-rate speech is reached at a  $\text{C/I}_{c}$  (co-channel interference) value of 19 dB, and the dynamic reference sensitivity level is -103 dBm for mobile equipment. Details of performance requirements in various channel conditions are given in clause 6.

## 5 Modulation

#### 5.1 Introduction

The following specifications apply to the baseband part of the transmitter.

## 5.2 Modulation type

The modulation used shall be  $\pi/4$ -shifted Differential Quaternary Phase Shift Keying ( $\pi/4$ -DQPSK).

#### 5.3 Modulation rate

The modulation rate shall be 36 kbit/s.

## 5.4 Modulation symbol definition

B(m) denotes the modulation bit of a sequence to be transmitted, where m is the bit number. The sequence of modulation bits shall be mapped onto a sequence of modulation symbols S(k), where k is the corresponding symbol number.

The modulation symbol S(k) shall result from a differential encoding. This means that S(k) shall be obtained by applying a phase transition  $D\phi(k)$  to the previous modulation symbol S(k-1), hence, in complex notation:

$$S(k) = S(k-1)\exp(jD\phi(k))$$

$$S(0) = 1$$

(1)

The above expression for S(k) corresponds to the continuous transmission of modulation symbols carried by an arbitrary number of bursts. The symbol S(0) is the symbol before the first symbol of the first burst and shall be transmitted as a phase reference.

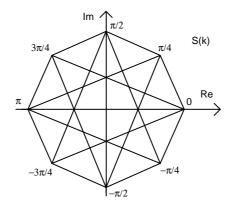

The phase transition  $D\phi(k)$  shall be related to the modulation bits as shown in table 1 and figure 3.

**Table 1: Phase transitions**

| B(2k-1) | B(2k) | Dφ(k) |

|---------|-------|-------|

| 1       | 1     | -3π/4 |

| 0       | 1     | +3π/4 |

| 0       | 0     | +π/4  |

| 1       | 0     | -π/4  |

Figure 3: Modulation symbol constellation and possible transitions

The complex modulation symbol S(k) shall take one of the eight values  $\exp(j n\pi/4)$ , where n=2,4,6,8 for even k and n=1,3,5,7 for odd k. The constellation of the modulation symbols and the possible transitions between them are as shown in figure 3.

## 5.5 Modulated signal definition

The modulated signal, at carrier frequency  $f_c$ , shall be given by:

$$M(t) = \operatorname{Re}\left\{s(t) \exp\left(j(2\pi f_c t + \phi_0)\right)\right\}$$

(2)

where:

- $\phi_0$  is an arbitrary phase;

- s(t) is the complex envelope of the modulated signal defined as:

$$s(t) = \sum_{k=0}^{K} S(k)g(t - t_k)$$

(3)

where:

- K is the maximum number of symbols;

- T is the symbol duration;

- $t_k = kT$  is the symbol time corresponding to modulation symbol S(k);

- g(t) is the ideal symbol waveform, obtained by the inverse Fourier transform of a square root raised cosine spectrum G(f), defined as follows:

$$G(f) = 1 \qquad \text{for} \qquad |f| \le (1-\alpha)/2T$$

$$G(f) = \sqrt{0.5(1-\sin(\pi(2|f|T-1)/2\alpha))} \qquad \text{for} \qquad (1-\alpha)/2T \le |f| \le (1+\alpha)/2T$$

$$G(f) = 0 \qquad \text{for} \qquad |f| \ge (1+\alpha)/2T \qquad (4)$$

where  $\alpha$  is the roll-off factor, which determines the width of the transmission band at a given symbol rate. The value of  $\alpha$  shall be 0,35. For practical implementation, a time limited windowed version of g(t), designed under the constraints given by the specified modulation accuracy and adjacent channel attenuation may be applied.

#### 5.6 Modulation filter definition

The modulation filter shall be a linear phase filter which is defined by the magnitude of its frequency response |H(f)| = G(f).

## 5.7 Modulation block diagram

A block diagram of the modulation process is shown on figure 4. This diagram is for explanatory purposes and does not prescribe a specific implementation. The modulation filter excited by the complex Dirac impulse function  $S(k)\delta(t-t_k)$  ideally has an impulse response g(t).

Figure 4: Block diagram of the modulation process

## 6 Radio transmission and reception

#### 6.1 Introduction

This clause defines the requirements for the MS transceiver of the TETRA DMO system. This clause is applicable to TETRA systems operating at radio frequencies of 300 MHz to 1 GHz.

## 6.2 Frequency bands and channel arrangement

DM-MSs may only transmit and receive in those channels allocated for TETRA DMO.

Dual Watch Mobile Stations (DW-MSs) and Dual Mode Mobile Stations (DU-MSs) shall also be able to transmit and receive within TETRA Voice plus Data (V+D) channels.

The TETRA DM RF carrier separation shall be 25 kHz.

## 6.3 Reference test planes

For the purpose of testing, all DM-MSs shall have at least one antenna connector. Measurements shall be carried out at the appropriate antenna connector of the equipment as specified by the manufacturer.

#### 6.4 Transmitter characteristics

## 6.4.1 Output power

In the following, power is defined as the average power, measured through the square root raised cosine filter defined in clause 5 over the useful part of the burst as defined in clause 9.

A DM-MS may be switched to operate in more than one power class.

#### 6.4.2 Power classes

The DM-MS nominal power shall be, according to its class, as defined in table 2.

**Power class Nominal power** 1 (30 W) 45 dBm (not defined for DM-MS) 1L (17,5 W) 42,5 dBm (not defined for DM-MS) 2 (10 W) 40 dBm 2L (5,6 W) 37,5 dBm 3 (3 W) 35 dBm 3L (1,8 W) 32,5 dBm 4 (1 W) 30 dBm 4L (0,56 W) 27,5 dBm 5 (0,3 W) 25 dBm 5L (0,18 W) 22,5 dBm

**Table 2: Nominal power of MS transmitters**

#### 6.4.3 Unwanted conducted emissions

#### 6.4.3.1 Definitions

Unwanted conducted emissions are defined as conducted emissions at frequencies or time intervals outside the nominal operating channel. The specified limits shall be met under realistic conditions, for instance under varying antenna mismatch.

Unless otherwise stated, unwanted emissions are specified for an equipment in the active transmit state.

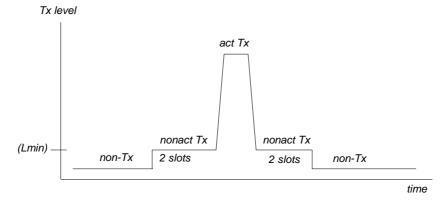

A DM-MS is in the active transmit state whenever it transmits bursts or whenever it ramps-up/linearizes or ramps-down.

The non-active transmit state is a state occurring during two timeslot durations (approximately 28 ms) before and after any active transmit state.

An equipment is said to be in the non-transmit state whenever it is not in the active or non-active transmit state (refer to figure 5).

Figure 5: Schematic presentation of transmitter states

#### 6.4.3.2 Unwanted emissions close to the carrier

Unwanted emissions close to the carrier shall be measured through the square root raised cosine filter with a roll-off factor of 0.35 as defined in clause 5.

Measurements shall be carried out at the actual centre frequency and at frequency offsets specified in the following clauses. When applicable, relative measurements (dBc) shall refer to the level measured at the actual centre frequency.

#### 6.4.3.2.1 Emissions during the useful part of the burst

The levels given in tables 3a and 3b, at the listed frequency offsets from the actual carrier frequency, shall not be exceeded.

Table 3a: Maximum adjacent power levels for frequencies below 700 MHz

| Frequency offset | Max. level for MS<br>power classes 4, 4L,<br>5 and 5L | Max. level for other power classes |

|------------------|-------------------------------------------------------|------------------------------------|

| 25 kHz           | -55 dBc                                               | -60 dBc                            |

| 50 kHz           | -70 dBc                                               | -70 dBc                            |

| 75 kHz           | -70 dBc                                               | -70 dBc                            |

In any case, no requirement in excess of -36 dBm shall apply.

Table 3b: Maximum adjacent power levels for frequencies above 700 MHz

| Free  | quency offset                         | Max. level         |  |

|-------|---------------------------------------|--------------------|--|

|       | 25 kHz                                | -55 dBc            |  |

|       | 50 kHz                                | -65 dBc            |  |

|       | 75 kHz                                | -65 dBc (see note) |  |

| NOTE: | A level of -70 dBc shall apply for MS |                    |  |

|       | Power Classes 1 and 1L.               |                    |  |

Frequency offset is defined as the difference of the centre measurement frequency from the actual carrier frequency. The measured values shall be averaged over the useful part of the burst (see clause 9). The scrambled bits shall have a pseudo-random distribution from burst to burst.

#### 6.4.3.2.2 Emissions during the switching transients

At the frequency offset from the actual carrier frequency given below, peak power measurements shall be carried out, covering at least the ramp-up period and the ramp-down period (see figure 7, periods  $t_1$  and  $t_3$  and clause 6.4.5 for definition of  $t_1$  and  $t_3$ ).

The maximum hold level of -45 dBc for MS power classes 4, 4L, 5 and 5L and -50 dBc for other power classes at a frequency offset of 25 kHz shall not be exceeded. This requirement does not apply to linearization channels.

In any case no requirement in excess of -36 dBm shall apply.

#### 6.4.3.3 Unwanted emissions far from the carrier

These unwanted emissions are emissions (discrete, wideband noise, modulated or un-modulated) occurring at offsets equal to, or greater than, 100 kHz from the carrier frequency, measured in the frequency range 9 kHz to 4 GHz.

#### 6.4.3.3.1 Discrete spurious

The maximum allowed power for each spurious emission shall be less than -36 dBm measured in 100 kHz bandwidth in the frequency range 9 kHz to 1 GHz and -30 dBm measured in 1 MHz bandwidth in the frequency range 1 GHz to 4 GHz (1 GHz to 12,75 GHz for equipment capable of operating at frequencies above 470 MHz). Specific measurement method are required both when measuring within  $\pm f_x$  of carrier frequency, due to the presence of wideband noise, and in the lower part of the spectrum.

#### 6.4.3.3.2 Wideband noise

The following wideband noise levels, measured through the modulation filter defined in clause 5.6 should not exceed the limits shown in tables 4a and 4b for the nominal power levels as stated and at the listed offsets from the actual carrier frequency.

Table 4a: DM wideband noise limits for frequencies below 700 MHz

| Frequency offset (kHz) | Maximum wideband noise level (dBc)        |                 |                                |

|------------------------|-------------------------------------------|-----------------|--------------------------------|

|                        | MS nominal power<br>level ≤ 1 W (class 4) |                 | MS nominal power level ≥ 5,6 W |

|                        | (0.000 1)                                 | (class 3 or 3L) | (class 2L)                     |

| 100 kHz - 250 kHz      | -75 dBc                                   | -78 dBc         | -80 dBc                        |

| 250 kHz - 500 kHz      | -80 dBc                                   | -83 dBc         | -85 dBc                        |

| > 500 kHz              | -80 dBc                                   | -85 dBc         | -90 dBc                        |

Table 4b: DM wideband noise limits for frequencies above 700MHz

| Frequency offset  | Maximum wideband noise level              |                                                  |                                              |  |

|-------------------|-------------------------------------------|--------------------------------------------------|----------------------------------------------|--|

|                   | MS Nominal power<br>level ≤ 1 W (class 4) | MS Nominal power levels<br>from 1,8 W to<br>10 W | MS Nominal power levels<br>from 15 W to 30 W |  |

| 100 kHz - 250 kHz | -74 dBc                                   | -74 dBc                                          | -80 dBc                                      |  |

| 250 kHz - 500 kHz | -80 dBc                                   | -80 dBc                                          | -85 dBc                                      |  |

| > 500 kHz         | -80 dBc                                   | -85 dBc                                          | -90 dBc                                      |  |

All levels are expressed in dBc relative to the actual transmitted power level.

In the case where a DM-MS transmits on a DM channel frequency which is within its normal V+D MS Tx band, then the limits in table 5 shall apply symmetrically to both sides of its V+D MS Tx band.

Table 5: DM wideband noise limits (continued)

| Frequency offset (kHz) | Maximum level all classes (dBc) |

|------------------------|---------------------------------|

| > f <sub>rb</sub>      | -100 dBc                        |

Where  $f_{rb}$  denotes the frequency offset corresponding to the near edge of its V+D MS receive band with  $f_{rb} \ge 5$  MHz (10 MHz for frequencies above 520 MHz).

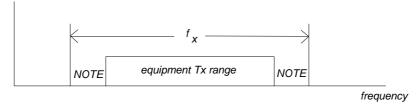

In other cases, the -100 dBc requirement shall apply outside of the frequency range  $f_x$  which comprises the range of frequencies over which the equipment is able to transmit (as declared by the equipment manufacturer), plus a guard band of 5 MHz (10 MHz for frequencies above 520 MHz) on either side as shown in figure 6.

NOTE: 5 MHz (10 MHz for frequencies above 520 MHz).

Figure 6: Definition of f<sub>x</sub>

In any case no limit tighter than -55 dBm for offsets <  $f_{rb}$  or -70 dBm for offsets >  $f_{rb}$  shall apply.

#### 6.4.3.4 Unwanted emissions during the Linearization CHannel (LCH)

The sum of the time periods during which the peak power, at a frequency offset of  $\pm 25$  kHz during the LCH, is above -45 dBc shall not exceed 1 ms. This peak power shall never exceed -30 dBc.

NOTE: 0 dBc refers to the transmit power during normal operation after the LCH.

#### 6.4.3.5 Unwanted emissions in the non-transmit state

The specifications of clause 6.5.4.2 apply.

#### 6.4.4 Unwanted radiated emissions

Unwanted radiated emissions are emissions (whether modulated or un-modulated) radiated by the cabinet and structure of the equipment. This is also known as cabinet radiation.

The limits given in clause 6.4.3.3 shall apply.

#### 6.4.5 Radio frequency tolerance

The radio frequency tolerance for DM-MSs is defined in clause 7.

#### 6.4.6 RF output power time mask

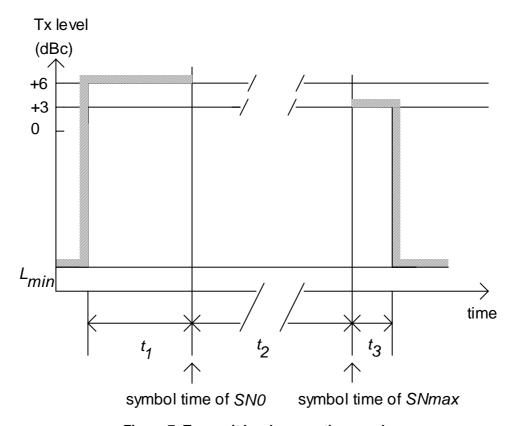

The transmit level versus time mask for DM-MS transmissions is shown in figure 7. For the time mask the power level of 0 dBc refers to the output power level of the TETRA station under consideration

Figure 7: Transmit level versus time mask

Table 6: Transmit level versus time mask symbol durations (refer to figure 7)

| Burst Type                                      | t <sub>1</sub> | t <sub>2</sub> | t <sub>3</sub> |

|-------------------------------------------------|----------------|----------------|----------------|

| Synchronization                                 | 16             | 235 (see note) | 15             |

| Linearization                                   | 251            | -              | 15             |

| Normal                                          | 16             | 235            | 15             |

| NOTE: Applies to single slot transmission only. |                |                |                |

Whenever bursts are consecutively transmitted by the same DM-MS on the same frequency, the transmit level versus time mask applies at the beginning of the transmission of the first burst and at the end of the transmission of the last burst.

The symbol numbers referred to as SN0 and SNmax are defined in clause 9. The timing of the transmitted bursts is specified in clause 7. The time periods  $t_1$ ,  $t_2$  and  $t_3$ , whose durations are stated in table 6, are defined in the following way:

- the time t<sub>1</sub> starts at the beginning of the ramp-up of the first burst, and expires just before the symbol time of SN0;

- the time t<sub>2</sub> starts at the symbol time of SN0 of the first burst and finishes at the symbol time of SNmax of the last burst;

- the time t<sub>3</sub> starts just after the symbol time of SNmax of the last burst and finishes at the end of the ramp-down.

In this clause, the specifications of clauses 6.4.1 and 6.6.1 shall apply during the time  $t_2$ . The output power shall be measured through the square root raised cosine filter with a roll off factor of 0.35 as defined in clause 5.

During the non-active transmit state the specification  $L_{min} = -70$  dBc or  $L_{min} = -36$  dBm, whichever is greater, shall apply.

A DM-MS may be required to receive in slots on the transmit frequency during the non-active transmit state. In this situation the equipment shall meet the receiver sensitivity specifications.

#### 6.4.7 Transmitter intermodulation attenuation

Intermodulation may be caused when a DM-MS transmits in the close vicinity of the antenna of another DM-MS.

#### 6.4.7.1 Definition

Transmitter intermodulation attenuation is the ratio of the power level of the wanted signal to the power level of an intermodulation component. It is a measure of the capability of the transmitter to inhibit the generation of signals in its non-linear elements caused by the presence of the useful carrier and an interfering signal reaching the transmitter via its antenna.

#### 6.4.7.2 Specification

For a transmitting MS operating at the nominal power defined by its class, the intermodulation attenuation shall be at least 60 dB for any intermodulation component when measured in 30 kHz bandwidth. The interfering signal shall be unmodulated and have a frequency offset of at least 500 kHz from the carrier frequency. The power level of the interfering signal shall be 50 dB below the power level of the modulated output signal from the transmitter under test.

#### 6.5 Receiver characteristics

In this clause, the levels of the test signals are given in terms of power levels (dBm) at the antenna connector of the receiver.

Sources of test signals shall be connected in such a way that the impedance presented to the receiver input is a 50  $\Omega$  non-reactive impedance.

Static propagation conditions are assumed in all cases, for both wanted and unwanted signals.

#### 6.5.1 Blocking characteristics

#### 6.5.1.1 Definition

Blocking is a measure of the capability of the receiver to receive a modulated wanted input signal in the presence of an unwanted un-modulated input signal on frequencies other than those of the spurious responses or the adjacent channels, without this unwanted input signal causing a degradation of the performance of the receiver beyond a specified limit.

#### 6.5.1.2 Specification

The blocking performance specification shall apply at all frequencies except those at which spurious responses occur (see clause 6.5.2).

The static reference sensitivity performance as specified in clause 6.6.2.4 shall be met when the following signals are simultaneously input to the receiver:

- a wanted signal at the nominal receive frequency f<sub>o</sub>, 3 dB above the static reference sensitivity level as specified in clause 6.6.2.4;

- a continuous sine wave signal at a frequency offset from  $f_0$  and level as defined in table 7.

> 500 kHz

Offset from nominal Rx frequency

Level of interfering signal

50 kHz to 100 kHz

-40 dBm

100 kHz to 200 kHz

-35 dBm

200 kHz to 500 kHz

-30 dBm

-25 dBm

Table 7: Blocking levels of the receiver

## 6.5.2 Spurious response rejection

#### 6.5.2.1 Definition

Spurious response rejection is a measure of the capability of a receiver to receive a wanted modulated signal without exceeding a given degradation due to the presence of an unwanted un-modulated signal at any other frequency at which a response is obtained, i.e. for which the blocking limit is not met.

#### 6.5.2.2 Specification

The static reference sensitivity performance as specified in clause 6.6.2.4 shall be met when the following signals are simultaneously applied to the receiver:

- a wanted signal at nominal receive frequency f<sub>o</sub>, 3 dB above the static reference sensitivity level as specified in clause 6.6.2.4;

- a continuous sine wave signal with any offset from nominal Rx frequency ≥ 50 kHz at a level of -45 dBm.

The number of frequencies within a limited frequency range, defined below, at which the blocking specification of clause 6.5.1.2 is not met shall not exceed 0.05 x (number of frequency channels in the limited frequency range).

The limited frequency range is defined as the frequency of the local oscillator signal  $f_{lo}$  applied to the first mixer of the receiver plus or minus the sum of the intermediate frequencies  $(f_{i1},.....f_{in})$  and a half of the switching range (sr) of the receiver.

Hence the frequency  $f_1$  of the limited frequency range is:

$$f_{lo} - \sum_{j=1}^{n} f_{ij} - \frac{sr}{2} \le f_l \le f_{lo} + \sum_{j=1}^{n} f_{ij} + \frac{sr}{2}$$

(5)

where receiver switching range (sr) is the maximum frequency range over which the receiver can be operated without reprogramming or realignment as declared by the manufacturer.

#### 6.5.3 Intermodulation response rejection

#### 6.5.3.1 Definition

Intermodulation response rejection is a measure of the capability of the receiver to receive a wanted modulated signal without exceeding a given degradation due to the presence of two or more unwanted signals with a specific frequency relationship to the wanted signal frequency as defined in ETS 300 113 [1].

#### 6.5.3.2 Specification

The static reference sensitivity performance as specified in clause 6.6.2.4 shall be met when the following signals are simultaneously input to the receiver:

- a wanted signal at the nominal receive frequency f<sub>o</sub>, 3 dB above the static reference sensitivity level;

- a continuous sine wave signal at frequency f<sub>1</sub> and with a level of -47 dBm;

- a pseudo-random sequence TETRA modulating a signal at frequency  $f_2$ , with a level of -47 dBm, such that  $f_0 = 2f_1 f_2$  and  $|f_2 f_1| = 200$  kHz.

#### 6.5.4 Unwanted conducted emissions

#### 6.5.4.1 Definition

Unwanted emissions from the equipment when in reception are defined as conducted emissions at any frequency, when the equipment is in the non-transmit state.

#### 6.5.4.2 Specification

The power emitted by the equipment shall not exceed -57 dBm at frequencies between 9 kHz and 1 GHz and -47 dBm at frequencies from 1 GHz to 4 GHz (1 GHz to 12,75 GHz for equipment capable of operating at frequencies above 470 MHz), as measured in the bandwidth of 100 kHz.

#### 6.5.5 Unwanted radiated emissions

Unwanted radiated emissions are emissions radiated by the cabinet and structure of the equipment in the non-Tx state. This is also known as cabinet radiation.

The limits given in clause 6.5.4.2 shall apply.

## 6.6 Transmitter/receiver performance

Clause 6.6.1 specifies the modulation accuracy requirement, by setting limits on the Root Mean Square (RMS) error between the actual transmitted signal waveform and the ideal signal waveform. Clause 6.6.2 specifies the receiver performance, assuming that transmit errors do not occur. Clause 6.6.3 specifies all the propagation models that are defined in the present document.

#### 6.6.1 Modulation accuracy

The specified requirement is vector error magnitude; this does not only take into account modulation filtering linear distortion (amplitude and phase) or modulator impairments (quadrature offset, phase and linear amplitude errors in the modulation symbol constellation) but is a measure of the whole transmitter quality. It also takes into account local oscillator phase noise, filter distortion, and non-linearity of amplifiers. Vector error magnitude shall be specified at symbol time (see clause 6.6.1.2).

#### 6.6.1.1 Ideal case

The modulation symbol s(t) transmitted by an ideal transmitter having a filter impulse response g(t) is defined in clause 5.

Let Z(k) denote the output of an ideal receive filter with impulse response  $g^*(-t)\big|_{t=t_k}$ . The ideal transmit and receive filters in cascade form a raised cosine Nyquist filter, having a symbol waveform going through zero at symbol duration intervals, so there is no inter-symbol interference at any instant  $t=t_k$ , where  $t_k$  is the symbol time corresponding to the k-th symbol (as defined in clause 5).

In this case, the output of an ideal receive filter at any instant  $t_k$ , stimulated by an ideal transmitter, will be equal to the k-th modulation symbol S(k):

$$Z(k) = s(t) * g(-t) \Big|_{t=t_k} = S(k)$$

(6)

In this clause, the numbering of the modulation symbols used is the one defined in clause 9.

#### 6.6.1.2 Vector error magnitude requirement at symbol time

Let Z(k) be the output produced by observing the real transmitter through the ideal receive filter at symbol time  $t_k$ . Z(k) is modelled as:

$$Z(k) = \left\{ C_0 + \left[ S(k) + E(k) \right] \right\} C_1 W(k) \tag{7}$$

where:

- E(k) is the vector error of modulation symbol S(k);

- $W(k) = \exp(jk\Theta)$  accounts for a frequency offset giving  $\Theta$  radians per symbol phase rotation due to transmitter frequency inaccuracy (see clause 7). The possible amplitude variations shall be integrated in the vector error;

- C<sub>0</sub> is a complex constant characterizing the residual carrier;

- $C_1$  is a complex constant representing the output amplitude and initial phase of the transmitter.

The magnitude of  $C_0$  shall be less than 5 % of the magnitude of S(k). The task of the test receiver is then to:

- estimate the symbol time for processing the receive part;

- estimate the values of  $C_0$ ,  $C_1$  and  $\Theta$ . The resulting estimates shall be denoted by  $C_0'$ ,  $C_1'$  and  $\Theta'$  respectively;

- perform a normalization of the modulation symbol Z(k) accordingly. The modulation symbol that results from this normalization shall be denoted by Z'(k):

$$Z'(k) = \left[ Z(k) \exp(-jk\Theta') / C_1' \right] - C_0'$$

(8)

With the above notations, the Sum Square Vector Error (SSVE) is defined as:

$$SSVE = \sum_{k=0}^{SN \max} |Z'(k) - S(k)|$$

(9)

where SNmax is the number of symbols in the burst.

The RMS vector error is then computed as the square root of the SSVE divided by the number of symbols in the burst:

$$RMSVE = \sqrt{\frac{SSVE}{SN \text{ max} + 1}}$$

(10)

The RMS vector error in any burst shall be less than 0,1.

The peak vector error magnitude |Z'(k)-S(k)| shall be less than 0,3 for any symbol.

#### 6.6.2 Receiver performance

This clause specifies the minimum required receiver performance in terms of BER, Message Erasure Rate (MER) or Probability of Undetected Erroneous Message (PUEM) (whichever is appropriate), taking into account that transmitter errors do not occur, and that the transmitter shall be tested separately (see clause 6.6.1).

In this clause, the levels of the test signals are given in terms of power levels (dBm) at the antenna connector of the receiver. For the definition of power level refer to clause 6.4.1.

#### 6.6.2.1 Nominal error rates

This clause describes the transmission requirements in terms of error rates in nominal conditions i.e. without interference and with an input level of -85 dBm. The relevant propagation conditions are given in clause 6.6.3.

Under the following propagation conditions, the BER of the non-protected bits, equivalent to the TCH/7,2 shall have the limits given in table 8.

**Table 8: Nominal error rates**

| Propagation model | BER    |

|-------------------|--------|

| STATIC            | 0,01 % |

| DR50              | 0,40 % |

| DU50              | 0,60 % |

This performance shall be maintained up to -40 dBm input level for the static conditions, and multipath conditions. Furthermore, for static conditions, a BER of < 0.1 % shall be maintained up to -20 dBm.

#### 6.6.2.2 Dynamic reference sensitivity

The minimum required dynamic reference sensitivity is specified according to the logical channel, and the propagation condition at the dynamic reference sensitivity level. The dynamic reference sensitivity level for DM-MSs shall be -103 dBm.

Table 9 gives the maximum permissible DM-MS receiver MER or BER at the dynamic reference sensitivity level for DU50 and DR50 propagation models.

For Signalling CHannel SCH/S, SCH/H and SCH/F, a PUEM < 0,001 % shall be achieved at the dynamic reference sensitivity level.

Table 9: Maximum permissible DM-MS receiver MER or BER at dynamic reference sensitivity level

| Logical channel                                               | Criterion | Propagation Model |        |  |

|---------------------------------------------------------------|-----------|-------------------|--------|--|

|                                                               |           | DU50              | DR50   |  |

| SCH/S                                                         | MER       | 5,60 %            | 8,00 % |  |

| SCH/H                                                         | MER       | 6,40 %            | 8,00 % |  |

| SCH/F                                                         | MER       | 5,40 %            | 8,00 % |  |

| TCH/7,2                                                       | BER       | 1,70 %            | 2,20 % |  |

| TCH/4,8 N = 1                                                 | BER       | 1,50 %            | 2,00 % |  |

| TCH/4,8 N = 4                                                 | BER       | 0,45 %            | 0,40 % |  |

| TCH/4,8 N = 8                                                 | BER       | 0,15 %            | 0,06 % |  |

| TCH/2,4 N = 1                                                 | BER       | 0,37 %            | 0,35 % |  |

| TCH/2,4 N = 4                                                 | BER       | 0,01 %            | 0,01 % |  |

| TCH/2,4 N = 8                                                 | BER       | 0,01 %            | 0,01 % |  |

| STCH                                                          | MER       | 6,40 %            | 8,00 % |  |

| NOTE: N gives the interleaving depth in number of blocks (see |           |                   |        |  |

| clause 8).                                                    |           |                   |        |  |

#### 6.6.2.3 Receiver performance at reference interference ratios

The minimum required reference interference ratios are specified according to the logical channel and the propagation condition at the reference interference ratio (for co-channel,  $C/I_c$ , or adjacent channel,  $C/I_a$ ). The reference interference ratio shall be:

- for co-channel interference:  $C/I_c = 19 \text{ dB};$

for adjacent channel interference:  $C/I_a = -40 \text{ dB}$ .

In the case of co-channel interference, these specifications apply for a wanted input signal level of -85 dBm, and in the case of adjacent channel interference for a wanted input signal level 3 dB above the dynamic reference sensitivity level. In any case the interference shall be a continuous TETRA random modulated signal subjected to an independent realization of the same propagation condition as the wanted signal.

Table 10 specifies the maximum permissible DM-MS receiver MER or BER at the reference interference level for DU50 and DR50 propagation conditions.

For SCH/S, SCH/H and SCH/F, a PUEM < 0,001 % shall be achieved at the reference interference level.

Table 10: Maximum permissible DM-MS receiver MER or BER at reference interference level

| Logical channel                                          | Criterion | Propagation Model |        |  |

|----------------------------------------------------------|-----------|-------------------|--------|--|

|                                                          |           | DU50              | DR50   |  |

| SCH/S                                                    | MER       | 4,90 %            | 6,00 % |  |

| SCH/H                                                    | MER       | 5,60 %            | 7,00 % |  |

| SCH/F                                                    | MER       | 4,80 %            | 6,50 % |  |

| TCH/7,2                                                  | BER       | 1,70 %            | 2,00 % |  |

| TCH/4,8 N = 1                                            | BER       | 1,60 %            | 2,00 % |  |

| TCH/4,8 N = 4                                            | BER       | 0,47 %            | 0,40 % |  |

| TCH/4,8 N = 8                                            | BER       | 0,18 %            | 0,06 % |  |

| TCH/2,4 N = 1                                            | BER       | 0,45 %            | 0,35 % |  |

| TCH/2,4 N = 4                                            | BER       | 0,01 %            | 0,01 % |  |

| TCH/2,4 N = 8                                            | BER       | 0,01 %            | 0,01 % |  |

| STCH                                                     | MER       | 5,60 %            | 7,00 % |  |

| NOTE: N gives the interleaving depth in number of blocks |           |                   |        |  |

| (see clause                                              | 8).       |                   |        |  |

#### 6.6.2.4 Static reference sensitivity

The minimum required static reference sensitivity is specified according to the logical channel and the receiver class at the static reference sensitivity level. For DM-MSs the static reference sensitivity level shall be -112 dBm.

Table 11 gives the maximum permissible DM-MS receiver MER or BER at the static reference sensitivity level.

For SCH/S, SCH/H and SCH/F, a PUEM < 0,001 % shall be achieved at the static reference sensitivity level.

Table 11: Maximum permissible DM-MS receiver MER or BER at static reference sensitivity level

| Logical channel                                          | Criterion | Propagation model |  |

|----------------------------------------------------------|-----------|-------------------|--|

|                                                          |           | STATIC            |  |

| SCH/S                                                    | MER       | 3,00 %            |  |

| SCH/H                                                    | MER       | 5,00 %            |  |

| SCH/F                                                    | MER       | 9,00 %            |  |

| TCH/7,2                                                  | BER       | 4,00 %            |  |

| TCH/4,8 N = 1                                            | BER       | 0,30 %            |  |

| TCH/4,8 N = 4                                            | BER       | 0,20 %            |  |

| TCH/4,8 N = 8                                            | BER       | 0,15 %            |  |

| TCH/2,4 N = 1                                            | BER       | 0,01 %            |  |

| TCH/2,4 N = 4                                            | BER       | 0,01 %            |  |

| TCH/2,4 N = 8                                            | BER       | 0,01 %            |  |

| STCH                                                     | MER       | 5,00 %            |  |

| NOTE: N gives the interleaving depth in number of blocks |           |                   |  |

| (see clause 8).                                          |           |                   |  |

#### 6.6.2.5 MS receiver performance for acquisition of synchronization burst

This clause specifies reference sensitivity performance of a MS receiver for the acquisition of the Direct mode Synchronization Burst (DSB). The performance is defined in terms of the Probability of synchronization burst ACQuisition (PACQ) of detecting a DSB and correctly decoding the SCH information for the condition where the MS is listening on the frequency while the DSB is transmitted.

Table 12: MS receiver performance requirement (probability of correct detection and decoding) for synchronization burst acquisition

| Propagation condition | DR50 |  |

|-----------------------|------|--|

| PACQ                  | 0,8  |  |

#### 6.6.3 Propagation conditions

The following contains all necessary information on the propagation models that are referred to in the present document.

#### 6.6.3.1 Tap-gain process types

This clause defines the statistical properties of the stationary complex tap-gain processes, to be applied for the propagation models, in terms of a Probability Density Function (PDF) and a Power Density Spectrum (PDS) which models the Doppler spectrum. The complex tap-gain processes, denoted by a(t) and defined hereunder, are normalized to unity power.

CLASS is the tap-gain process having a PDS equal to the classical Doppler spectrum. The real and imaginary parts of a(t) exhibit an identical gaussian PDF, an identical PDS and are mutually statistically independent. Hence |a(t)| is Rayleigh distributed. The PDS of a(t) is defined by:

$$S(f) = S_{CLASS}(f, f_d) = \frac{1}{\pi f_d \sqrt{1 - (f/f_d)^2}}, \quad \text{for } -f_d < f < f_d; \text{ and}$$

$$S(f) = 0 \qquad \text{elsewhere}$$

$$(11)$$

where the parameter  $f_d$  represents the maximum Doppler shift (in Hz), defined as  $f_d = v/\lambda$  with the vehicle speed v (in m/s) and the wavelength  $\lambda$  (in m).

$STATIC(f_s)$  is a tap-gain process with a constant magnitude |a(t)| = 1. The PDS of a(t) is defined by:

$$S(f) = S_{STATIC}(f, f_s) = \delta(f - f_s)$$

(12)

where  $\delta(.)$  represents the Dirac delta function and  $f_s$  the Doppler shift (in Hz).

RICE is a tap-gain process which is the sum process of the two processes CLASS and STATIC( $f_s$ ), with  $f_s = 0.7 f_d$ , each contributing half of the total power. Hence |a(t)| is Rician distributed and the PDS is:

$$S(f) = S_{RICE}(f, f_d) = 0.5S_{CIASS}(f, f_d) + 0.5S_{STATIC}(f, 0.7f_d)$$

(13)

#### 6.6.3.2 DM propagation models

In this clause, the propagation models that are referred to in the present document are defined. Two models are used, DU50 and DR50. The vehicle speed x (in km/h), which affects  $f_d$  (see clause 6.6.3.1), is attributed to the model designation in the frequency range 380 MHz to 520 MHz (e.g. DU50 means Urban Area for 50 km/h in the 380 MHz to 520 MHz frequency range).

For frequencies outside the 380 MHz to 520 MHz range, for testing purposes only, the vehicle speed in the model is adjusted according the formula:

$$v = 20 \text{ [Hz] } x \lambda \text{ [m]},$$

when DU50 or DR50 is specified to keep the Doppler shift constant relative to 430 MHz.

Table 13: Propagation models

| Propagation model | Tap number | Relative delay (µs) | Average relative power (dB) | Tap-gain<br>process |

|-------------------|------------|---------------------|-----------------------------|---------------------|

| Static            | 1          | 0                   | 0                           | STATIC              |

| Urban Area (DUx)  | 1          | 0                   | 0                           | RICE                |

| Rural Area (DRx)  | 1          | 0                   | 0                           | CLASS               |

## 7 Radio sub-system synchronization

#### 7.1 Introduction

This clause defines the requirements for synchronization in TETRA DM Operation, for carrier frequencies of between 300 MHz and 1 GHz.

## 7.2 Definitions and general requirements for synchronization of DM-MSs

The DM-MS which provides the synchronization reference is defined as the "master" DM-MS. A DM-MS which initiates a call becomes the master for the duration of that transaction. Any DM-MS which synchronizes on a "master" DM-MS is defined as a "slave" DM-MS.

At the beginning of a call, during a call transaction or during channel reservation, the master DM-MS shall transmit synchronization bursts to enable any receiving DM-MS on the same channel to synchronize itself in terms of frequency and time, or to maintain synchronization.

In any case the slave DM-MS shall align its burst transmission to the timeslots and carrier frequency dictated by the transmission of the master DM-MS.

The timebase of a DM-MS shall continuously count quarter symbols, symbols, timeslots and frames, independently of whether the DM-MS is transmitting or not (see clause 7.3). A slave DM-MS is said to be fully time synchronized if all of its timebase counters run synchronously, within a specified tolerance to those of the master DM-MS.

The timing information contained in the SCH/S transmitted by the master DM-MS in the synchronization burst shall refer to the slot and frame number at which the synchronization burst is transmitted. Upon reception of an SCH/S, the slave DM-MS shall use this timing information to set its slot and frame counters.

In normal cases (see note 1) a slave DM-MS which becomes the new master DM-MS after a changeover or pre-emption has been carried out successfully shall adopt the state of the timing counters indicated by the old master DM-MS. The transition point at which changeover occurs shall be at a timeslot boundary.

NOTE 1: An exception may be the case where a timing change request has been included within the changeover or pre-emption request.

A master DM-MS which makes a new call on a free DM channel shall begin transmission at the RF carrier frequency resulting from its own frequency reference source.

A DM-MS taking over the master role after changeover or pre-emption shall either:

- begin transmission at the RF carrier frequency resulting from its own frequency reference source; or

- begin transmission at the RF carrier frequency resulting from its synchronization to the previous master and subsequently increment or decrement this transmission frequency in steps of between 25 Hz and 100 Hz until the transmission frequency resulting from its own frequency reference source is reached or until it stops being master. The frequency steps shall be made at a rate of once per frame during occupation and once every 6th frame during reservation. The frequency steps shall not occur during a transmitted burst.

NOTE 2: In occupation, the frequency steps begin with the start of transmission of traffic or, in the case of short data, the transmission of SCH/F frames.

#### 7.3 Timebase counters

#### 7.3.1 Definition of counters

The timing state of the signals transmitted by a DM-MS shall be defined by the following counters:

- Quarter symbol Number (QN) (1 4);

- Symbol Number (SN) (1 255);

- Timeslot Number (TN) (1 4);

- Frame Number (FN) (1 18).

#### 7.3.2 Relationship between the counters

The relationship between these counters shall be as follows:

QN increments every 125/9 µs (unless otherwise required by the slave DM-MS timebase adjustment) as follows:

$$QN := QN \bmod (4) + 1; \tag{14}$$

SN increments whenever QN changes from 4 to 1 as follows:

$$SN := SN \mod(255) + 1;$$

(15)

TN increments whenever SN changes from 255 to 1 as follows:

$$TN := TN \bmod (4) + 1; \tag{16}$$

FN increments whenever TN changes from 4 to 1 as follows:

$$FN := FN \mod(18) + 1$$

. (17)

The simultaneous change of state of all counters to 1 defines the timebase reference point.

# 7.4 Requirements for the frequency reference source of DM mobiles

A DM-MS shall use a frequency reference source of sufficient accuracy such that the RF carrier frequency is generated to an accuracy of better than  $\pm 1,0$  kHz.

The timebase shall be clocked to an accuracy of better than  $\pm 2$  ppm.

## 7.5 Requirements for the synchronization of a slave DM mobile

The following requirement for carrier frequency and timebase accuracy shall be met by a slave DM-MS for a transmission period of one multiframe duration following initial synchronization. This requirement shall be achieved at receive signal levels greater than or equal to 3 dB below the reference sensitivity level defined in clause 6. Static or dynamic reference sensitivity levels shall be used depending upon the applied propagation conditions:

- whenever the slave DM-MS transmits its carrier frequency, it shall be accurate to within  $\pm 250$  Hz and its burst timing shall be accurate to within 1/2 symbol period compared to signals received from the master DM-MS.

The following requirement for the carrier frequency and timebase shall be met by a slave DM-MS for the time period following one multiframe duration after initial synchronization until the end of reception of the master's transmission:

- whenever the slave DM-MS transmits its carrier frequency, it shall be accurate to within  $\pm 100$  Hz and its burst timing shall be accurate to within 1/4 symbol period compared to signals received from the master DM-MS.

The signals received from the master DM-MS shall be averaged over sufficient time so that errors due to noise, interference or Doppler spread are minimized.

NOTE:

When the DM-MS equipment is required to transmit in slave mode, it is important that it synchronizes with and transmits back to the master on the master's frequency and timing. This happens, for example, during pre-emption request, changeover request (when the channel is reserved), timing change request, responding to call set-up with presence check and when responding to an acknowledged short data message.

# 7.6 Synchronization requirements for a master MS operating on channel B in frequency efficient mode

In frequency efficient operation a master MS operating on channel B shall periodically monitor the channel A master MS transmissions in order to acquire and maintain timing synchronization. The master MS on channel B shall adjust its internal timebase in line with those signals received from the channel A master MS.

The channel B master MS shall meet the following requirements at receive signal levels of greater than or equal to 3 dB below the reference sensitivity level defined in clause 6. Static or dynamic reference sensitivity levels shall be used depending upon the applied propagation conditions.

a) The channel B master MS shall adjust its internal timebase in line with that of signals received from the channel A master MS. If the channel B master MS determines that the timing difference between its current slot timing and that of channel A exceeds 1/4 symbol duration, it shall adjust its timebase in steps of not greater than 1/4 symbol duration. This adjustment shall be performed at intervals of not less than 4y multiframe durations and not greater than 12y multiframe durations until the timing difference is less than 1/4 symbol duration, where the step size is y symbol duration (with  $y \le 1/4$ ).

NOTE: The channel B master MS may adjust its timebase if it detects a timing difference between its current slot timing and that of channel A of less than 1/4 symbol duration.