#### Recommendation T/CD 01-12 E (Cannes 1983)

# CONCERNING THE SPECIFICATION OF ENGINEERING REQUIREMENTS FOR THREE TYPES OF PLUG-IN DCE'S OPERATING WITH A USER DATA SIGNALLING RATE OF 2,400 BIT/S

Recommendation proposed by Working Group T/GT 10 "Data Communications" (CD)

Text of the Recommendation adopted by the "Telecommunications" Commission:

"The Conference of European Post and Telecommunications Administrations,

#### Considering

- that the CEPT Recommendation T/CD 01-01 contains the text of the specification of the general engineering requirements for Data Circuit-Terminating Equipment for use on voice-band, base-band and group-band circuits;

- that GT/CD has studied the harmonization of DCE's under the auspices of Question CD7.

#### Recommends

that the attached specification of engineering requirements for three types of built-in versions of DCE's as contained in the Annex to this Recommendation should apply when such equipment is being considered by CEPT Administrations for a particular application."

This Recommendation is to be seen as the first step of harmonizing the built-in DCE. This Recommendation includes a number of national requirements, as several networks have already been in operation and changes could not be made to these without considerable penalties in delays and costs.

A harmonization project that will take into account future development of components, software, etc., is to be formed as the second step of this work.

Note 1: It should be noted that this Recommendation may be revised from time to time.

Note 2: The Annex is an integral part of the Recommendation.

### Annex. Index

| l.   | Scope                                                  | • | <br> | ٠ | <br>• |  |

|------|--------------------------------------------------------|---|------|---|-------|--|

| PA   | RT I (Type I) Pages 1 to 31                            |   |      |   |       |  |

| Sec  | tion A. Common requirements                            |   |      |   |       |  |

|      | General                                                |   |      |   |       |  |

| 2.   | Functional requirements for the transmission unit (TU) |   |      |   |       |  |

| 3.   | Functional requirements for the conversion unit (CU)   |   | <br> |   |       |  |

| 4.   | Test loops                                             |   | <br> |   |       |  |

| 5.   | Power consumption                                      |   | <br> |   |       |  |

| 6.   | Construction                                           |   | <br> |   |       |  |

| 7.   | Environmental requirements                             |   | <br> |   |       |  |

|      | tion B. Network dependent requirements                 |   |      |   |       |  |

| 1.   | General                                                |   |      |   |       |  |

| 2.   | Transmission unit base-band (TUB)                      |   |      |   |       |  |

| 3.   | Testing and measuring requirements                     |   |      |   |       |  |

| 4.   | Equalizer to be provided in the TUM                    |   |      |   |       |  |

| 5.   | Line wetting                                           |   |      |   |       |  |

| 6.   | DCE power-OFF signal                                   |   |      |   |       |  |

| 7.   | Character alignment                                    |   |      |   |       |  |

| 8.   | Electrical characteristics and significant levels      |   |      |   |       |  |

| 9.   | Connector (CU to TU)                                   |   |      |   |       |  |

| 10.  | Transmit inhibit function                              | • | <br> | ٠ | <br>• |  |

| Seci | tion C. Optional requirements                          |   |      |   |       |  |

| 1.   | General                                                |   |      |   |       |  |

| 2.   | Optional interchange circuits                          |   |      |   |       |  |

| 3.   | <b>Test points</b>                                     |   |      |   |       |  |

| 4.   | Construction                                           |   | <br> |   | <br>٠ |  |

| PAI  | RT II (Type II) Pages 1 to 6                           |   |      |   |       |  |

| Seci | ion A. Common requirements                             |   |      |   |       |  |

| 1.   | General                                                |   | <br> |   |       |  |

| 2.   | Requirements for Alternative A1                        |   | <br> |   |       |  |

| 3.   | Requirements for Alternative A2                        |   | <br> |   |       |  |

|      | Requirements for Alternative B1                        |   | <br> |   |       |  |

| 5.   | Requirements for Alternative B2                        |   | <br> |   |       |  |

| 6.   | <b>Test loops</b>                                      |   |      |   |       |  |

| 7.   | Power consumption                                      |   | <br> |   |       |  |

| 8.   | Construction                                           |   |      |   |       |  |

| 9.   | Environmental requirements                             |   |      |   |       |  |

| Sect | ion B. Network dependent requirements                  |   |      |   |       |  |

| 1.   | General                                                |   | <br> |   |       |  |

| 2.   | Base-band DCE's                                        |   | <br> |   |       |  |

| 3.   | Testing and measuring requirements                     |   |      |   |       |  |

| Sect | ion C. Optional requirements                           |   |      |   |       |  |

| 1.   | General                                                |   |      |   |       |  |

| 2.   | Optional interchange circuits                          |   |      |   |       |  |

| 3.   | Functional requirements of the interface between DCE a |   |      |   |       |  |

| 4.   | Optional modes of operation                            |   |      |   |       |  |

| 5.   | Test points                                            |   |      |   |       |  |

| 6.   | Construction                                           |   |      |   |       |  |

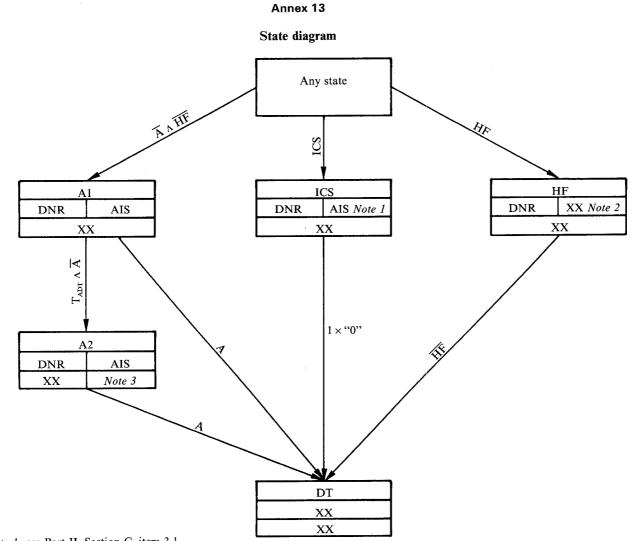

## PART III (Type III) Pages 1 to 24 Section A. Common requirements 4. Requirements for Alternative B1 Section B. Network dependent requirements Section C. Optional requirements Annex 1. Modulation schemes Annex 2. Example of a block diagram of the TUM Annex 3. Example of scrambler and descrambler circuitry Annex 4. Relationship between data and timing Annex 5. Example of a block diagram of the CU Annex 6, sheet 1. State diagram for alarms and consecutive actions Annex 6, sheet 2 Annex 7, sheet 1. Example of fixing Annex 7, sheet 2. Example of fixing Annex 7, sheet 3. Example of fixing Annex 8, sheet 1. Further details of the connector Annex 8, sheet 2 Annex 8, sheet 3 Annex 8, sheet 4 Annex 8, sheet 5 Annex 8, sheet 6 Annex 8, sheet 7 Annex 8, sheet 8 Annex 9. Pin allocation for type I, II and III plug-in DCE's Annex 10, sheet 1. Climatogram for operation Annex 10, sheet 2. Climatogram for warehousing Annex 11. Test call from the DCE Annex 12. Test call from the network Annex 13. State diagram

#### 1. SCOPE

This document specifies 3 versions of a DCE, which is a physical unit intended to be accommodated within a DTE by plug-in means. Where a higher degree of integration is envisaged, offering the same functionality (e.g. total integration of DTE and DCE), those requirements that are not relevant to that degree of integration need not be taken into account (e.g. interfaces, construction).

The specification consists of 3 parts, each of them describing one of the versions of the DCE for different usage:

Type I: Plug-in version of a DCE for user classes 4 and 8 (according to CCITT Recommendation X.1) for

envelope-structured direct access (8+2 or 6+2) to a switched data network (see Part I).

Type II: Plug-in version of a DCE for user classes 4 and 8 for non-envelope-structured direct access to a

switched data network (see Part II).

Type III: Plug-in version of a DCE at 2,400 bit/s for GSTN or access to a data network via GSTN (see Part III).

Annex 1 summarizes the modulation schemes for all 3 types.

All these plug-in DCE's are potentially relevant to terminal equipment in the data field or in Teletex terminals.

The functions of these plug-in DCE's are the same as those offered by separate DCE's. The network equipment must be able to operate without changes with both plug-in and separate DCE's.

Each part of this Recommendation contains 3 sections:

- Section A: Common requirements.

- Section B: Network dependent requirements.

- Section C: Optional requirements.

Section B describes different solutions which have to be taken into account when developing a DCE or DTE for a certain national network. Section C contains possible optional requirements.

In Parts II and III reference will be made to Part I (and in Part II to Part III) in all cases, whenever possible, in order to avoid repetitions.

It is intended that each type of plug-in DCE should be capable of occupying the same space within the Terminal Equipment as the other types. In other words, it is intended that all the 3 types should be physically interchangeable.

#### PART I (TYPE I)

#### Section A

#### 1. GENERAL

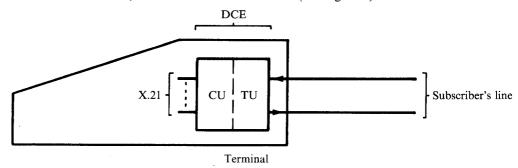

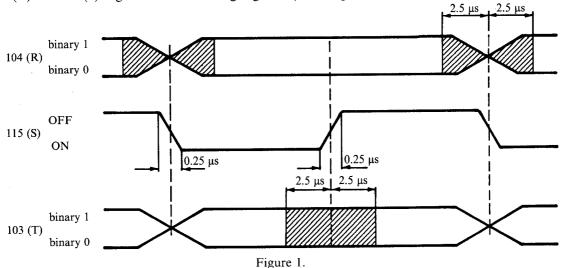

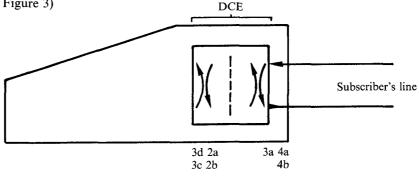

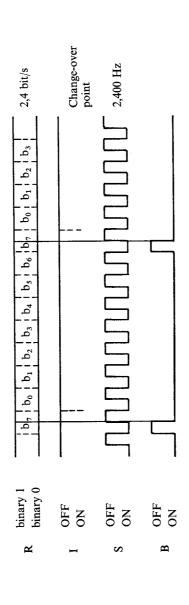

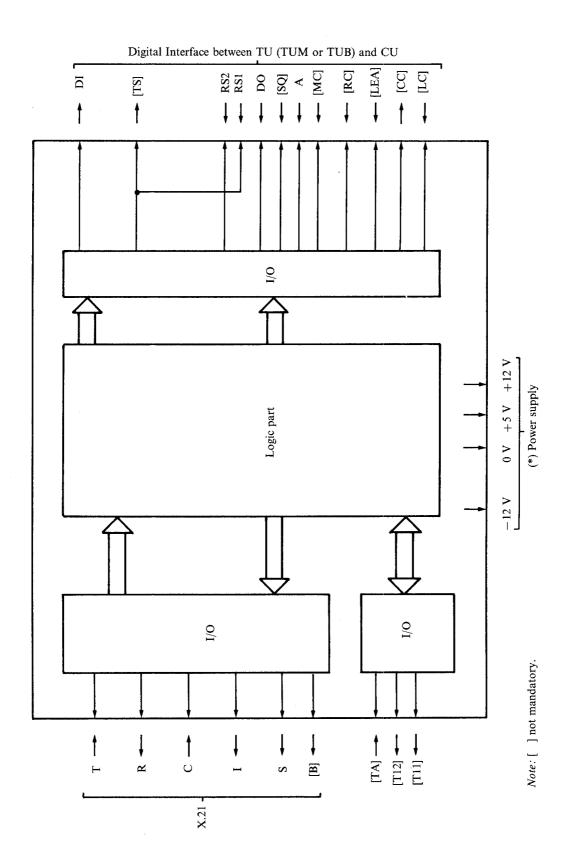

This type I-DCE consists of two functional units, the transmission unit TU (which can be a voice-band modem or a base-band modem) and the conversion unit CU (see Figure 1).

- TU Transmission unit.

- CU Conversion unit.

Figure 1.

The interface between the CU and the terminal fulfils the logical requirements of the CCITT Recommendation X.21.

#### 2. FUNCTIONAL REQUIREMENTS FOR THE TRANSMISSION UNIT (TU)

Depending on e.g. the length of the subscriber's line, a voice-band modem or a base-band modem can be used as a TU.

### 2.1. Transmission unit modem (TUM)

The principal characteristics of the TUM are based on CCITT Recommendations V.26 and V.27 (referred to as Alternative A2 in Annex 1).

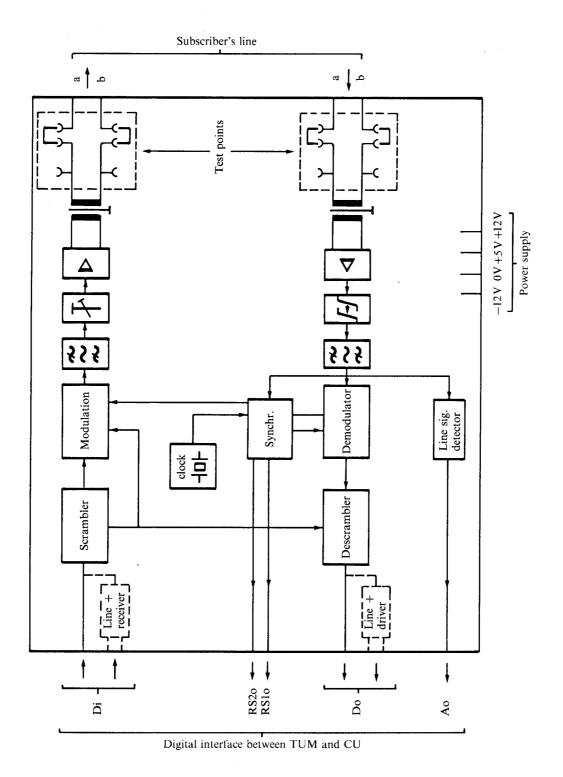

An example of a block diagram of the TUM is given in Annex 2.

#### 2.1.1. Data signalling rates

The data signalling rate for the user shall be 2,400 bit/s  $\pm 0.01\%$ .

Depending on the used envelope structure the addition of the framing (or envelope alignment) bits and the status bits results in a

- 33% (8-bit envelope) or

- 25% (10-bit envelope)

increase in data signalling rate, so that the following rates will be used at the digital interface (see 2.1.2.) and in the subscriber's line:

- 3.2 kbit/s (8-bit envelope structure) or

- 3 kbit/s (10-bit envelope structure).

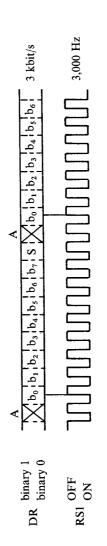

#### 2.1.2. Digital interface

Note: The description of the digital interface given in this section is primarily included as a means for describing the functions of the TU. Additionally certain Administrations will have a requirement for a physically identifiable point of demarcation between CU and TU. Such a requirement may stem from the need to gain access for testing purposes, or to allow different types of TU to be associated with the CU. In this case for the electrical characteristics reference is made to Section B, item 8. For the mechanical characteristics an example is given in Section B, item 9.

#### (a) Interchange circuits

In cases where a physical interface exists between TUM and CU the following Table 1 gives a list of mandatory interchange circuits (see also Annex 2).

| Interchange<br>circuit<br>designation | Interchange circuit name       | Access point designation CU TUM |        |

|---------------------------------------|--------------------------------|---------------------------------|--------|

| G                                     | Signal ground or common return | G                               | G      |

| DT                                    | Transmitted data               | Do -                            | → Di   |

| DR                                    | Receiver data                  | Di ↔                            | – Do   |

| RS1                                   | Received signal element timing | RS1i ←                          | - RS1o |

| RS2                                   | 8× or 6× clock of RS1          | RS2i ↔                          | - RS2o |

| A                                     | Received line signal detector  | Ai ←                            | – Ao   |

Table 1.

In addition, other circuits may be used for the operation between the TUM and CU. Those circuits have to be specified on a national basis. Examples of such circuits are contained in Section C, item 2.

#### (b) Definitions of the interchange circuits

Circuit G-Signal ground or common return

This conductor establishes the signal common return for unbalanced interchange circuits.

Circuit DT - Transmitted data

The data signals to be transmitted via a data channel to the remote data station, or to be passed to the TU for maintenance test purposes under control of the CU or DTE, are transferred on this circuit to the TU.

#### Circuit DR - Received data

The data signals generated by the TU, in response to data channel line signals received from the remote data station, or in response to the CU or DTE maintenance test signals, are transferred on this circuit to the CU.

#### Circuit RS1 - Receiver signal element timing

Signals on this circuit provide the CU with signal element timing information. The condition of this circuit shall be ON and OFF for nominally equal periods of time, and a transition from the On to OFF condition shall nominally indicate the centre of each signal element on circuit DR.

#### Circuit RS2 – $8 \times$ or $6 \times$ clock of RS1

The number of transitions from ON to OFF on this circuit should be  $8 \times$  higher than on circuit RS for a 10-bit envelope structure and  $6 \times$  higher for an 8-bit envelope structure. Each transition from ON to OFF of RS1 corresponds also with an ON to OFF transition of RS2.

### Circuit A – Received line signal detector

Signals on this circuit indicate whether the received data channel line signal is within appropriate limits. The ON condition indicates that the received signal is within appropriate limits. The OFF condition indicates that the received signal is not within appropriate limits.

(c) Electrical characteristics and significant levels (see Section B, item 8).

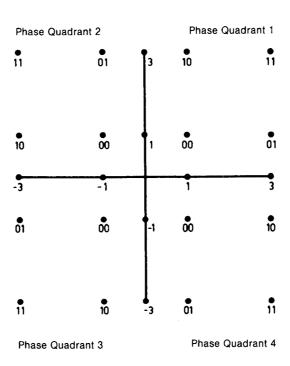

#### 2.1.3. Modulation and coding

The TUM uses a 4-phase differential modulation scheme with main characteristics according to CCITT Recommendation V.26.

- (a) Carrier frequency according to V.26.

- (b) Modulation rate:

- 1,500 bauds (if the 10-bit envelope structure is used)

- 1,600 bauds (if the 8-bit envelope structure is used).

- (c) The data stream to be transmitted is divided into pairs of consecutive bits (dibits). Each dibit is encoded as a phase change relative to the phase of the immediately preceding signal element according to V.26.

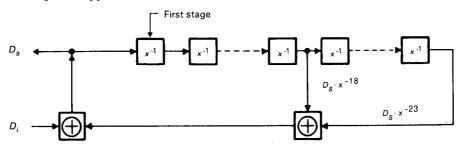

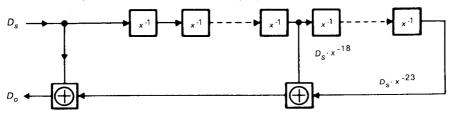

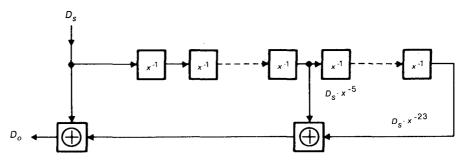

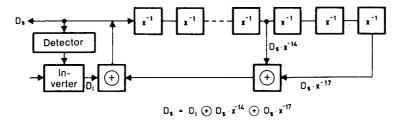

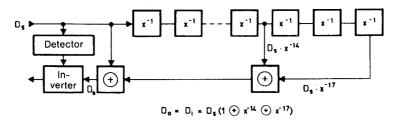

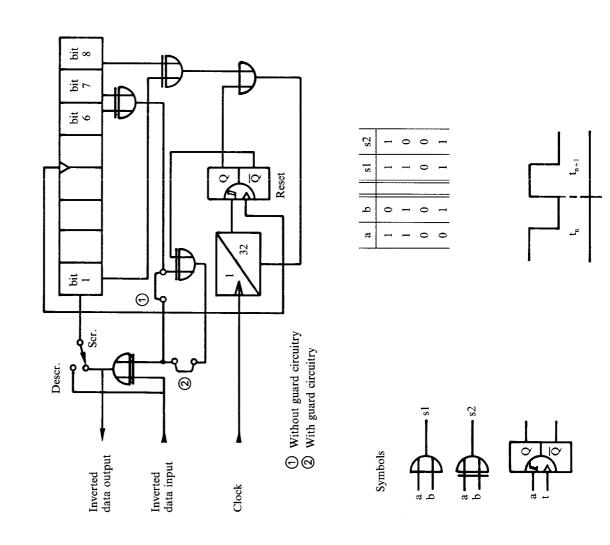

#### 2.1.4. Scrambling

A self-synchronizing scrambler/descrambler is used having the generating polynomial:

$$1 + x^{-6} + x^{-7}$$

.

The coefficients of the quotient of this division, arranged in descending order, represent the bit sequence to be coded and transmitted.

At the discretion of the Administration the scrambler may or may not have a guard circuitry, in which the transmitted bit sequence will be controlled over a range of 23 bits for the occurrence of a bit sequence of the form.

$$p(x) = \sum_{i=0}^{16} a_i x^i$$

where

$$a_i = 1 \text{ or } 0, \text{ and } a_i = a_{i+7}.$$

If such a bit sequence has been detected, the next following bit must be inverted before being transmitted. Annex 3 shows the basic circuit diagram of the scrambler.

The descrambler at the receive side is equivalent to the scrambler at the transmit side.

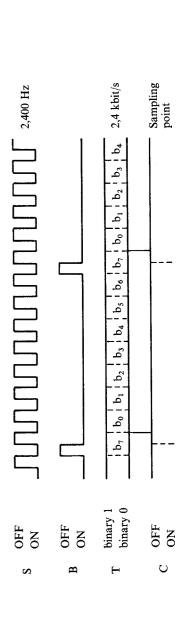

#### 2.1.5. Timing

The TUM has an internal clock source which under normal conditions is synchronized by the received data signal.

The free running accuracy of the internal clock shall be at least  $\pm 0.01\%$ .

The signal which is given to the interchange circuit RS1 (receiver signal element timing) is a square wave signal with a frequency of 3,000 Hz or 3,200 Hz.

A deviation from the nominal value shall not exceed  $\frac{T}{100}$  · 4 where T is the length of one cycle of RS1.

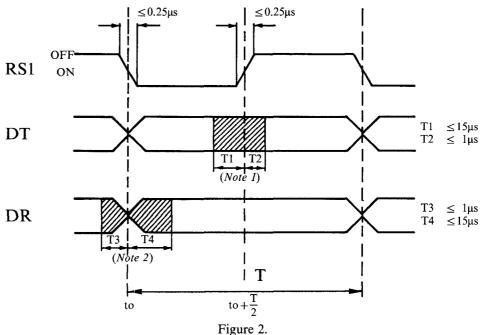

The phase relationship between transmitted and received data (DT, DR) and the signal element timing RS1 is given in Figure 2 (including tolerances) and Annex 4.

Note 1: The state on the interchange circuit DT has to be valid within the range of T1+T2 referring to the centre of the positive timing edge.

Note 2: A change of the state on the interchange circuit DR is only allowed within the range of T3+T4 referring to the centre of the negative timing edge.

Note 3: The phase relationship as specified here is not necessarily applicable in cases where the physical interface is not identifiable.

RS2 ( $8 \times$  or  $6 \times$  clock of RS1) is also a square wave signal with a duty cycle of 50% which corresponds to RS1 in the following way:

The transition from OFF to ON of RS2 shall occur in the range of  $\pm 5~\mu s$  around the transition of RS1.

Note 4: If maintenance loop 3a is activated, the internal transmit clock of the DCE must be switched to "master operation".

### 2.1.6. Line interface

The requirements of Recommendation T/CD 01-01 shall apply.

#### 2.1.6.1. Transmit side

(a) Transmit signal level

The requirements of Recommendation T/CD 01-01 shall apply.

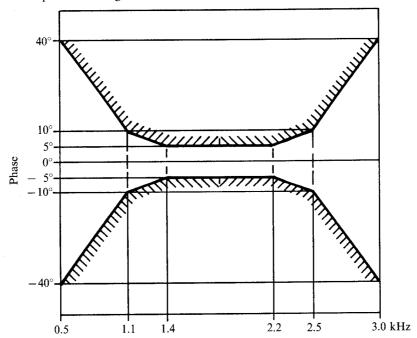

(b) Phase distortion limits

The transmitted line signal spectrum should have linear phase characteristics (to be obtained by means of filters or equalizers or digital means). The deviation of this linear phase characteristic should not exceed the limits specified in Figure 3.

Figure 3. Tolerance limit for phase distortion of the signal transmitted to the line.

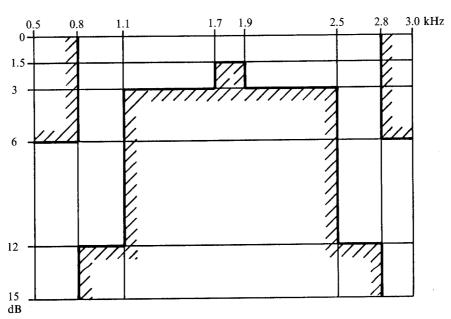

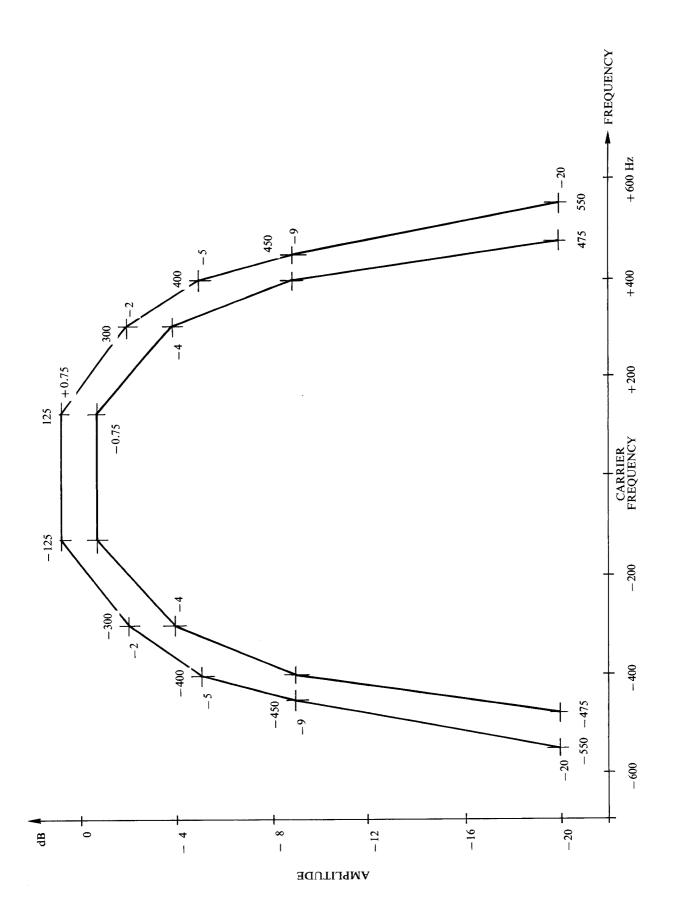

(c) Amplitude distortion limits

Power distribution of the signal spectrum originating when the 511-bit pseudo-random data sequences according to V.52 are applied to the circuit "Data input" (DI), shall be within the limits specified in Figure 4, and shall be of a raised cosine type with a roll-off factor of 50-60% equality divided between transmitter and receiver.

Figure 4. Tolerance limit for power distribution of the signal spectrum transmitted to the line.

#### 2.1.6.2. Receive side

(a) Received signal frequency tolerance

Noting that the carrier frequency tolerance at the transmitter is  $\pm 1$  Hz and assuming a maximum frequency drift of  $\pm 6$  Hz in the connection between the TUMs, then the receiver must be able to accept errors or at least  $\pm 7$  Hz in the received frequencies.

(b) Threshold of received line signal detector

Levels of received line signal:

greater than -26 dBm circuit A "ON"

less than -31 dBm circuit A "OFF".

The condition of circuit A (received line signal detector) for levels between the above levels is not specified except that the signal detector shall exhibit a hysteresis action such that the level at which the OFF-to-ON transition occurs is at least 2 dB greater than that for the ON-to-OFF transition.

(c) Response times of circuit A (received line signal detector)

A fall in level of the incoming line signal to -31 dBm or lower for more than  $10 \pm 5$  ms will cause circuit A to be turned OFF.

An increase in level to -26 dBm or higher will, within  $10 \pm 5$  ms, turn this circuit ON.

(d) Clamping to binary condition 1 of circuit DR (data output, received data)

Circuit DR is held in a marking condition (binary 1), when circuit A is in the OFF condition.

When this condition does not exist, the clamp is removed and circuit DR can respond to the input signals of the TUM.

2.1.7. Protection against higher voltages

The requirements of Recommendation T/CD 01-01 shall apply.

2.1.8. Performance requirements

The requirements of Recommendation T/CD 01-01 shall apply.

#### 2.2. Transmission unit base-band (TUB)

2.2.1. Data signalling rate

Same requirements as for the TUM apply.

2.2.2. Digital interface

Same requirements as for the TUM apply.

2.2.3. *Timing*

Same requirements as for the TUM apply.

2.2.4. Protection against higher voltages 3

The requirements of Recommendation T/CD 01-01 shall apply.

2.2.5. Additional requirements are given in Section B, item 2.

### 3. FUNCTIONAL REQUIREMENTS FOR THE CONVERSION UNIT (CU)

#### 3.1. General

The CU shall contain functions for formatting the terminal data to the network and in some cases (see Section B, item 7) character alignment. The CU shall also contain circuits for line supervision as well as for operation and maintenance (see Section B, item 3). All control signalling to and from the network will normally take place between the terminal itself and the network in accordance with CCITT Recommendation X.21.

This means that all signalling, except during testing and alarm states, takes place between the terminal and network without the participation of the plug-in DCE.

An example of a block diagram is given in Annex 5.

#### 3.2. Interface between the CU and the terminal

#### 3.2.1. General

The interface towards the terminal shall for the CU conform to the CCITT Recommendation X.21 for the functional requirement, X.24 for the definitions and item 3.2.3. for the electrical characteristics of the interchange circuits.

#### 3.2.2. Interchange circuits

The interchange circuits to be provided at the interface are (see Table 2):

| Interchange<br>circuit<br>designation | Interchange circuit name                | Dire<br>from<br>CU | ction<br>to<br>CU |

|---------------------------------------|-----------------------------------------|--------------------|-------------------|

| G                                     | Signal ground or common return (Note 1) |                    |                   |

| Т                                     | Transmit                                |                    | X                 |

| R                                     | Receive                                 | X                  |                   |

| C                                     | Control                                 |                    | X                 |

| I                                     | Indication                              | X                  |                   |

| S                                     | Signal element timing                   | X                  |                   |

Note 1: This interchange circuit is identical with power supply common return.

Table 2.

#### 3.2.3. Electrical characteristics and significant levels

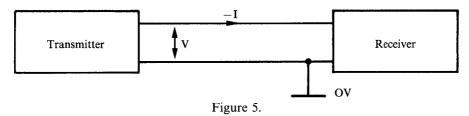

The electrical characteristics shall be as follows (see Figure 5):

#### TRANSMITTER:

"binary 1" or "OFF"  $\geq\!4.0$  V with load current  $-40~\mu A$  "binary 0" or "ON"  $\leq\!0.4$  V with load current 0.4 mA

### RECEIVER:

#### Thresholds

"binary 1" or "OFF"  $\geq +3.6 \text{ V}$ "binary 0" or "ON"  $\leq +0.7 \text{ V}$

"binary 1" or "OFF" -40 μA at 4 V

"binary 0" or "ON" 0.4 mA at 0.4 V

Permissible input voltage range: -0.5 ... + 5.5 V.

#### 3.2.4. Relationship between the interchange circuits

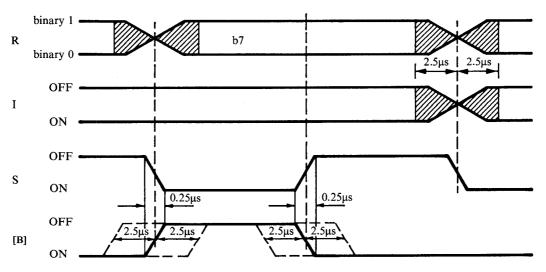

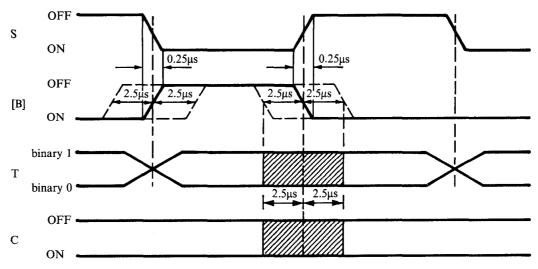

The phase relationship between the interchange circuits is given in Figure 6 (including the max. tolerances) and in Annex 4.

Figure 6.

#### 3.3. Envelope function

In the CU the data to be exchanged across the interchange circuits T and R are grouped/regrouped in envelopes. As for the forming of the envelope see CEPT Recommendation T/CD 02-01 (based on CCITT Recommendation X.50 = 6+2) and CEPT Recommendation T/CD 02-02 (based on CCITT Recommendation X.51 = 8+2).

#### 3.3.1. Status bit

The condition on the circuits C and I are conveyed by means of the status bit of the envelope with the following relation:

Status bit 0 = OFF condition on circuits C and I

1 = ON condition on circuits C and I.

| Transmit<br>side | C = OFF<br>C = ON | S = 0 $S = 1$     |

|------------------|-------------------|-------------------|

| Receive<br>side  | S = 0 $S = 1$     | I = OFF<br>I = ON |

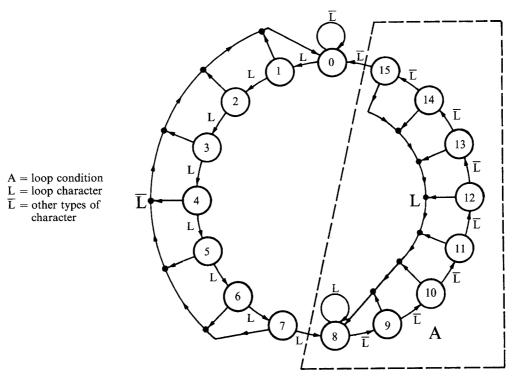

### 3.3.2. Envelope alignment strategy

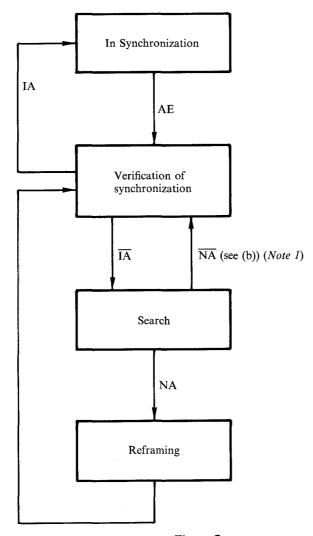

In the envelope alignment strategy four states and three criteria for transfer from one state to another can be recognized.

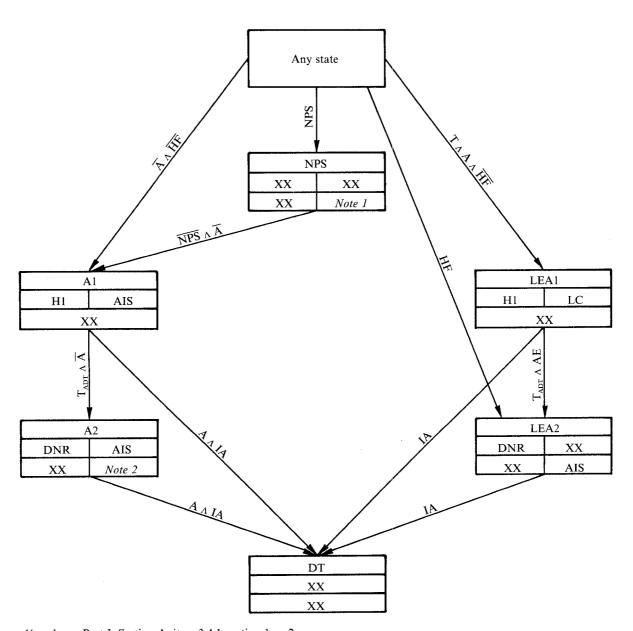

For state diagram see Figure 7.

#### (a) Criteria

Alignment Error (AE):

2, 3 or 4 contiguous envelope alignment bits with the same digital value.

In alignment (IA):

Absence of Alignement Errors in envelope alignment bits for the period of minimal 7 envelopes.

New Alignment (NA):

The identification of one unique bit position carrying the alignment pattern.

#### (b) States

(I) System in synchronization

DCE or the tributary channel is in alignment with network.

(II) Verification of synchronization

The alignment bits are supervised according to the IA criterium. Criterium IA transfers the system to State I. If the criterium IA is not found the system transfers to State III. State II may include the Time-Out for the elimination of the influence of short line breaks.

(III) Search

New Alignment criterium is searched in the received bit stream.

Note 1: Verification of synchronization and search of new alignment may be simultaneous processes. In this case the system returns to State II if NA is not found.

(IV) Reframing

Reframing of the system takes place if the NA criterium is fulfilled. A transfer to State II takes place.

(c) Alarms

The alarm "Loss of envelope alignment" (as used in the part "Fault conditions and consecutive actions" occurs, if T seconds after the criterium AE the criterium IA will not be received.

#### (d) Performance

- 1. The frame-alignment recovery time, after a slip and in absence of bit errors should be less than 50 envelopes, with 95% probability.

- 2. A random error rate of 1 in 10<sup>4</sup> shall not cause any frame-alignment recovery action.

#### State diagram

Figure 7.

#### 3.4. Alarms and consecutive actions

Four groups of possible failures are considered:

- Failures occurring in the terminal (fault condition a)

- Failures on the subscriber's line (fault condition b)

- Failures in another equipment of the network which has an impact on the DCE (fault conditions c, d)

- Failures within the DCE itself (fault condition e).

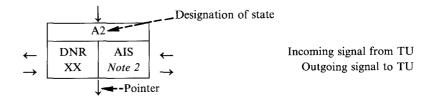

In Annex 6 a state diagram, definitions of signals and abbreviations are given which are mentioned in the following text.

- 3.4.1. Fault condition a: Failure of the power supply or the main power of the terminal

- Option 1: No action will be taken towards the network (Annex 6, state NPS).

- Option 2: Power failure of the DCE will be indicated to the network by a special signal, see Section B, item 6 (Annex 6, state NPS).

#### 3.4.2. Fault condition b: Loss of carrier

At loss of carrier, the TU detects this situation after a time of  $10 \pm 5$  ms and clamps the circuit DR to binary "1" (see 2.1.6.2. (c), (d)).

Depending on the interchange circuit A = OFF (received line signal detector) immediately a "Hold signal 1" (H1) will be sent to the terminal (Annex 6, state A1).

The terminal can transmit within the range of 2-3 s (action delay time). Afterwards two options are possible (Annex 6, state A2):

Option 3: AIS will be sent to the network.

Option 4: The CU will prevent the TU from transmitting an outgoing carrier.

#### 3.4.3. Fault conditions c and d: Loss of envelope alignment

Condition c: If the network loses envelope alignment, an AIS signal will be received by the DCE.

The CU detects this situation after a time T = 1 s (Annex 6, state LEA1).

Condition d: The detection of LEA can also occur, if the incoming data are strongly disturbed (Annex 6, state LEA1).

The consecutive actions towards the terminal in both cases are: 2-3 s action delay time.

"Hold signal 1" will be sent to the terminal.

The terminal can transmit during this range of 2-3 s.

If envelope alignment is not re-established during the action delay time, DNR will be sent to the terminal and AIS to the network (Annex 6, LEA2).

When envelope alignment in the DCE is re-established, through-connection of the DCE takes place (Annex 6, state DT).

#### 3.4.4. Fault condition e: DCE faults

If any hardware failure occurs and can be detected, AIS shall be sent, if possible, and DNR shall be sent towards the terminal, if possible (Annex 6, state LEA2).

#### 4. TEST LOOPS

The definitions of the loops are set out in CCITT Recommendation X.150.

#### 4.1. Local test loop – loop 3

In order to assist the test of the DTE, test loop 3 is provided in the DCE. The precise implementation is network dependent and indicated in Section B, item 3.1.

#### 4.2. Network test loop – loop 2a/2b

For maintenance purpose, a loop 2a/2b is implemented in the DCE. This loop is activated within the test call procedure, see Section B, item 3.2. (alternatives A to D).

If the loop towards the network is activated, the DCE will signal "DCE not ready" towards the terminal.

#### 4.3. Additional loops may be provided, see Section B, item 3.1.

#### 5. **POWER CONSUMPTION**

The power required by the plug-in DCE will be supplied by the terminal (see Annex 2 and Annex 5).

The following voltages and the relevant max. values of current are available:

$+12 \text{ V } \pm 5\% \text{ max.} \quad 150 \text{ mA}$

$-12 \text{ V} \pm 5\% \text{ max.}$  150 mA

$+ 5 \text{ V} \pm 5\% \text{ max. } 1,100 \text{ mA}$

The max. noise voltage to be excepted on these suplies is:

10 mV RMS and 30 mV peak-to-peak for the + & -12 V supplies

10 mV RMS and 100 mV peak-to-peak for the +5 V supply

The total power consumption of the DCE shall not exceed 8 watts.

Note: Power consumption in excess of 5 watts may require special precautions in the terminal equipment.

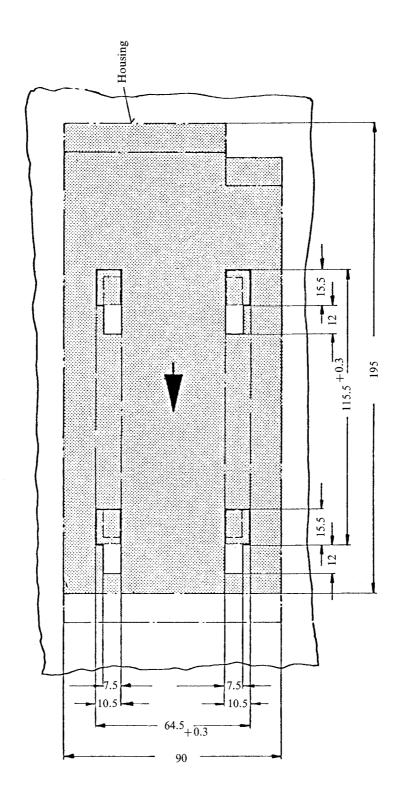

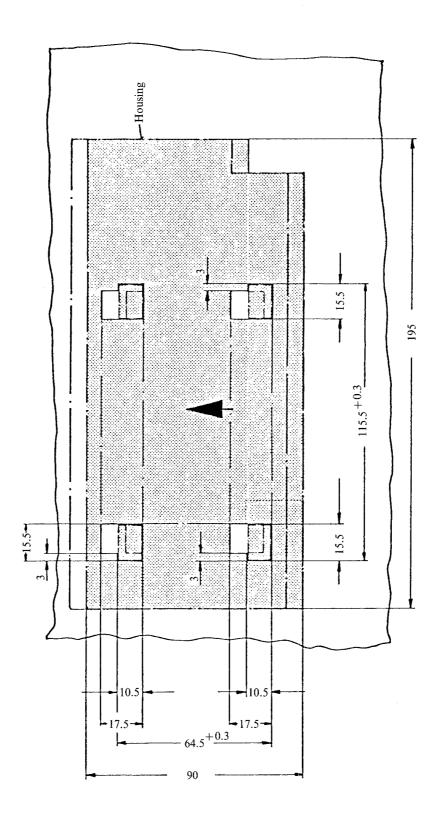

#### 6. **CONSTRUCTION**

For the time being, mechanical arrangements are only specified for typewriter-type terminals.

Taking into account the rapid developments in the field of DCE's, it is not, at the present time, convenient to specify the construction part for other applications. This will be a point for further study when these applications are defined.

Where the DCE is accommodated on a single card, for typewriter-type terminals this card must be accommodated within the dimensions specified in item 6.1.1. and the connector to the DTE must be in accordance with item 6.1.3.

Future study at the second step of harmonization will concentrate in a single solution taking into account the various requirements of the Administrations and future technologies.

#### 6.1. Construction of typewriter-type terminals

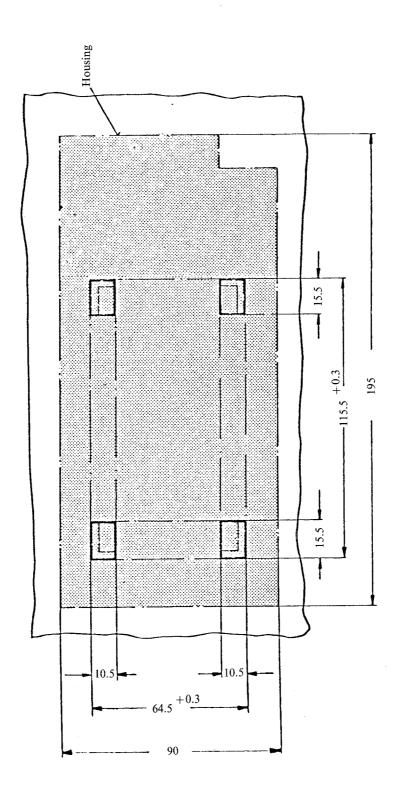

#### 6.1.1. Dimensions of the plug-in DCE

The dimensions of the plug-in DCE to be used in typewriter-type terminals must be no larger than the following:

It is up to each Administration to decide which of the two alternatives applies.

#### 6.1.2. Cabinet

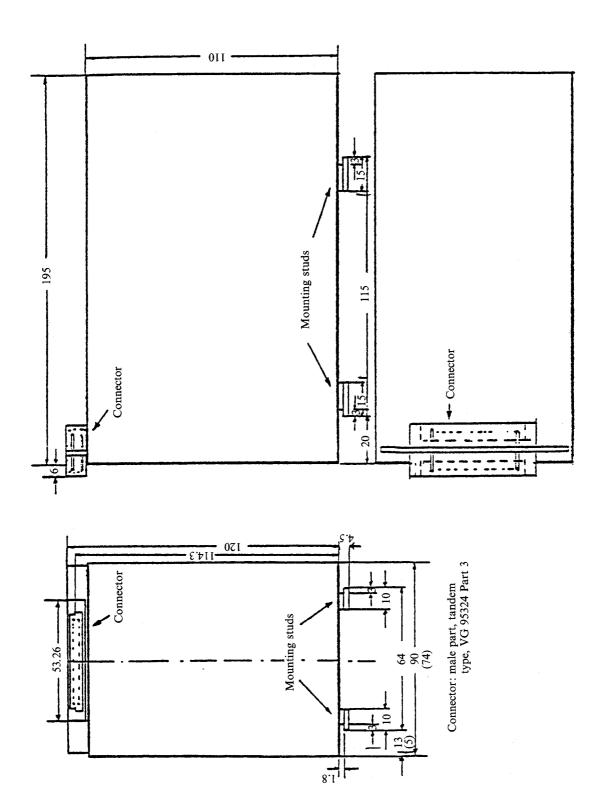

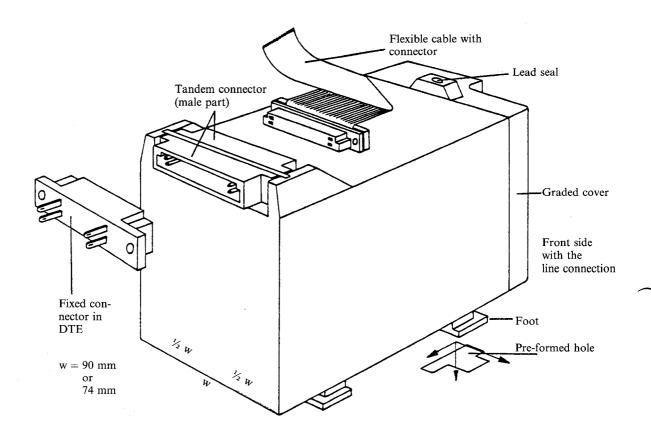

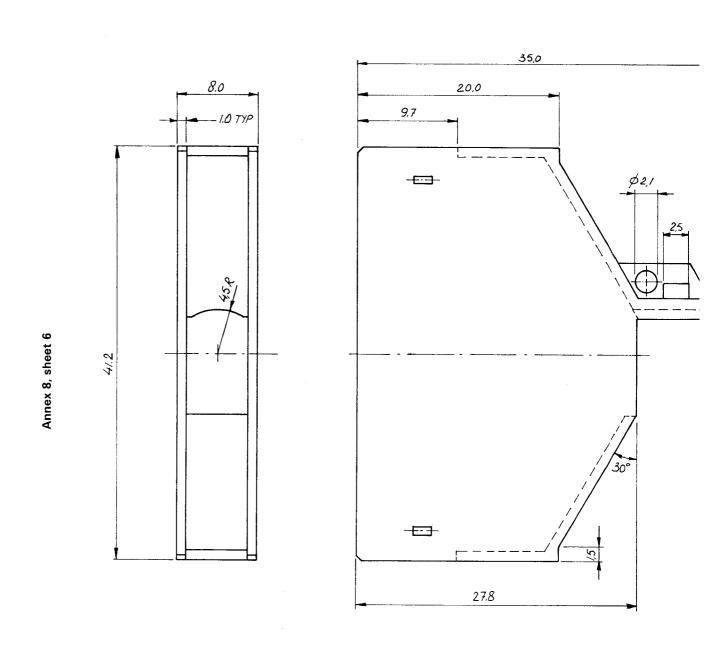

Where a number of separate modules comprise the DCE (e.g. when the two functional blocks, CU and TU, are realized separately) the preferred method of housing the modules is the use of a cabinet as specified in Figure 8. More details of this are given in Annex 7.

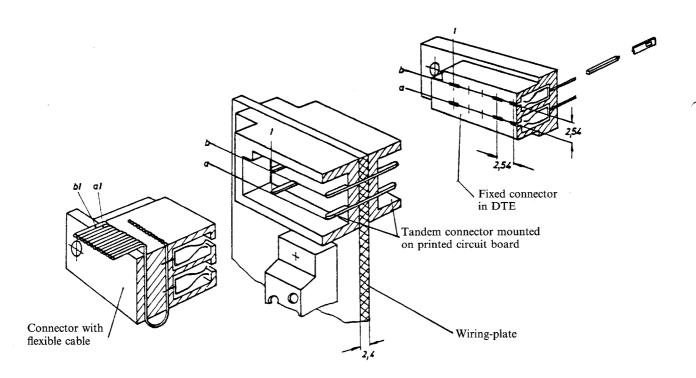

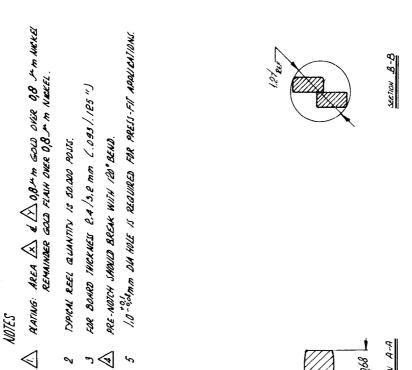

### 6.1.3. Connector (DTE to DCE)

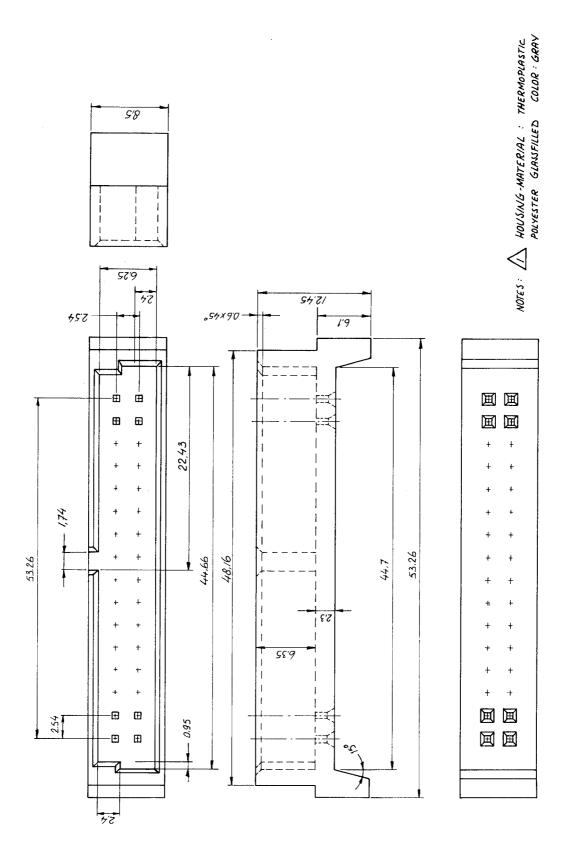

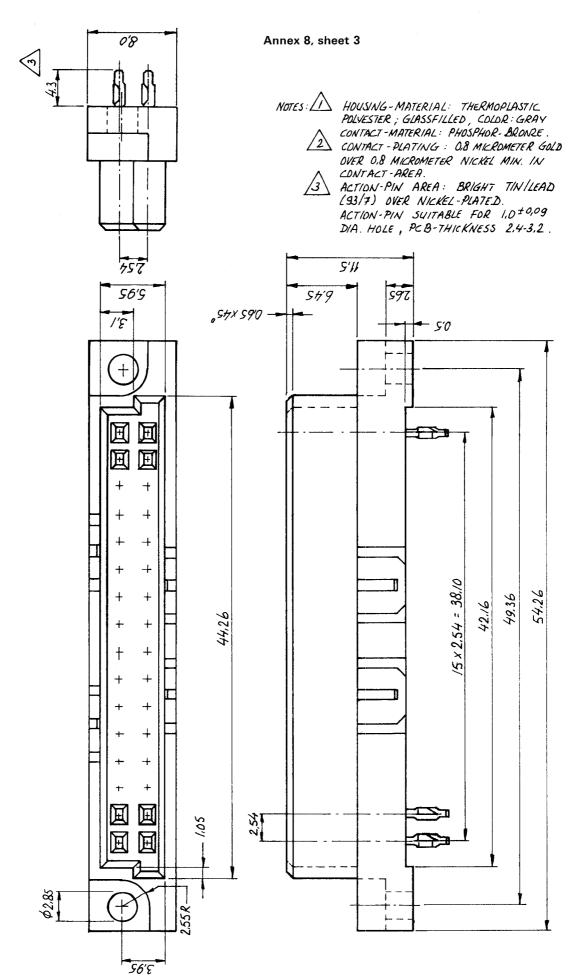

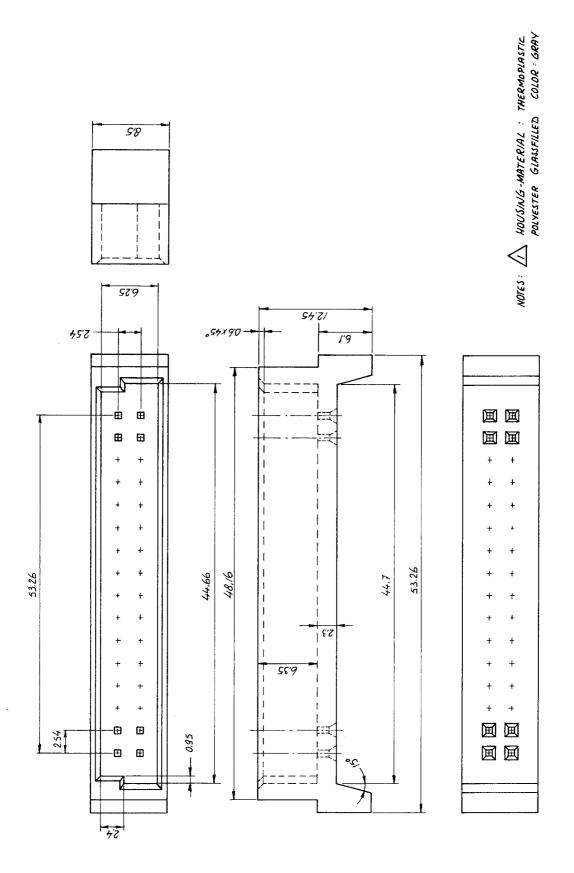

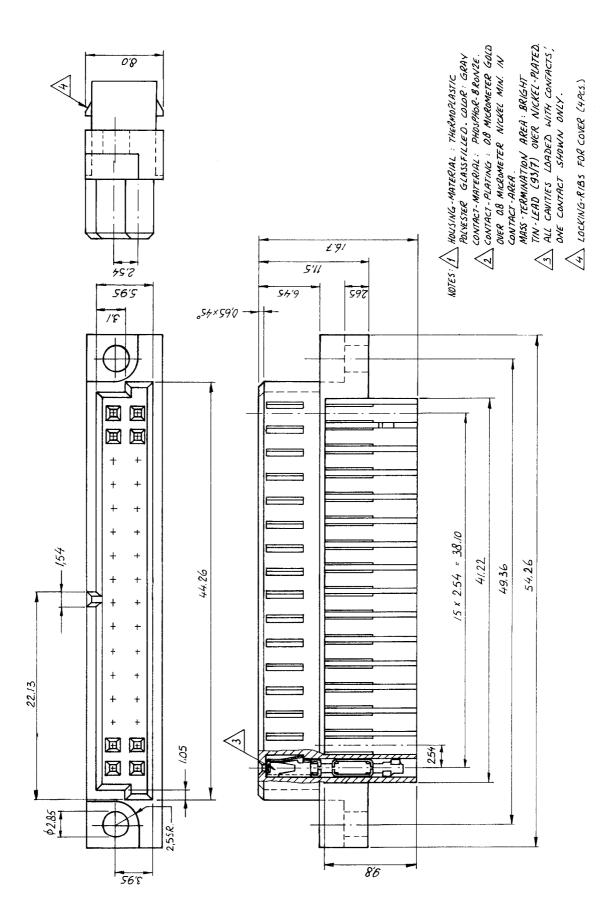

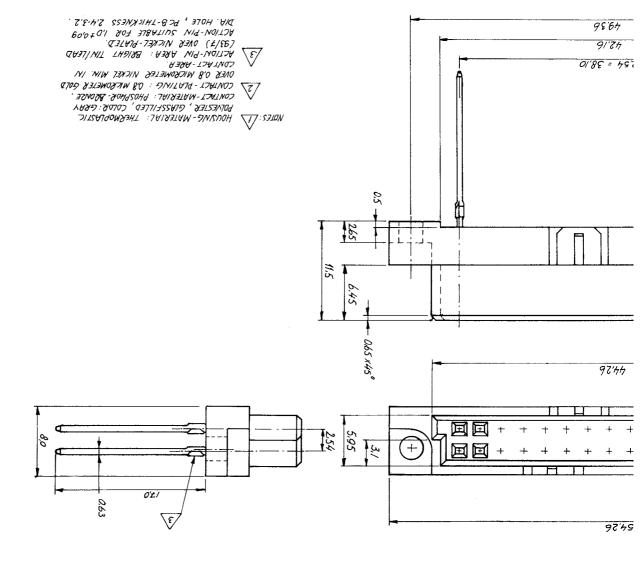

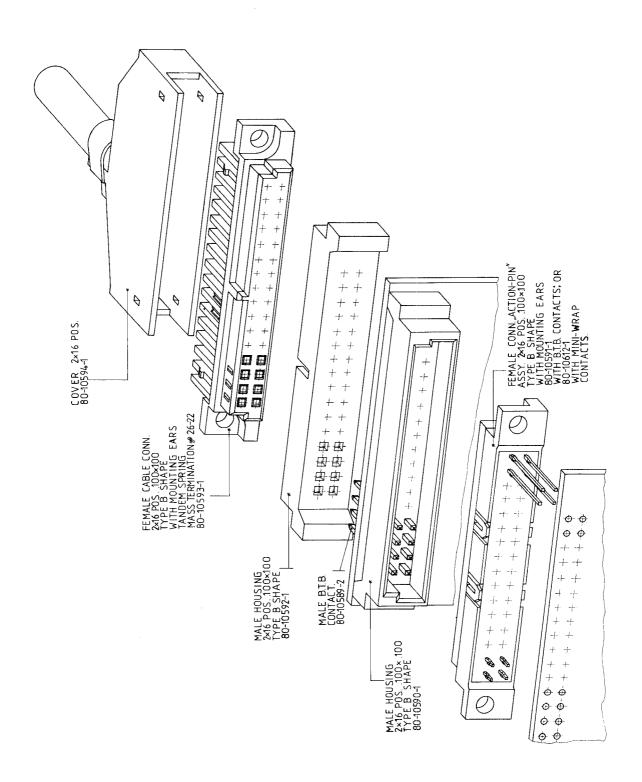

The equipment is electrically connected (digital interface, power supplies) to the terminal by means of a connector in accordance with Figures 9 and 10. The mechanical characteristics of this connector shall be as defined in standard VG 95324, part 3, connector for printed circuit, blade and socket connectors, 32 pin, grid 2.54 mm (for further details see Annex 8).

Figure 9 shows the general connector arrangements with two options for connecting the DCE to the DTE:

- (a) a female connector mounted in a fixed position in the DTE (where a cabinet is used to house the DCE, Figure 8 shows the positioning of the connector at the DCE),

- (b) a female connector on a flexible cable. Figure 10 shows the allocation of the connector rows and the pin numbering scheme.

The pin assignment for the interface connector is given in Annex 9.

#### 6.1.4. Connector (CU to TU)

This connector is not specified, however an example is given in Section B, item 9.

### 6.1.5. Connector (DCE to transmission line)

The transmission line cord shall be fixed within the DCE or connected by a connector at the front of the DCE (see e.g. Figure 9).

#### 7. ENVIRONMENTAL REQUIREMENTS

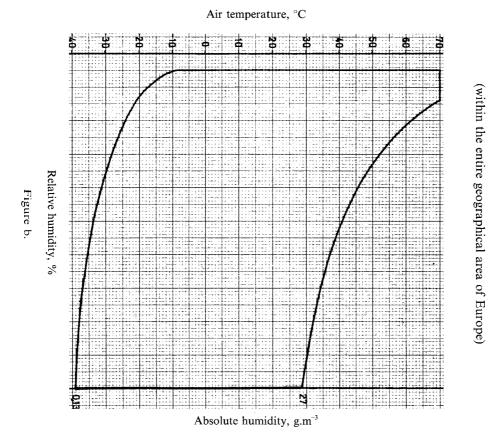

The full performance of the plug-in DCE shall be maintained when operating in an environment of ambient temperature and relative humidity as described in Annex 10.

Climatogram for operation. Annex 10, Figure a

Climatogram for transport. Annex 10, Figure b

Climatogram for warehousing. Annex 10, Figure c

Annex 10, Figures b and c are identical with the requirements of the Recommendation T/TR 02-03 concerning equipments for telecommunication centres.

Note 1: It could be necessary to protect the plug-in DCE against electrical and magnetical disturbances caused by the terminal.

Figure 8. Overall dimensions of the cabinet used for housing the built-in DCE, and positioning of the connector.

Figure 9. Connector arrangement.

Figure 10. Allocation of connector rows and counting scheme.

#### Section B

#### 1. **GENERAL**

This section specifies national network dependent requirements which may be included in a plug-in DCE at the discretion of the Administration concerned.

#### 2. TRANSMISSION UNIT BASE BAND (TUB)

In addition to the following network dependent requirements, the common requirements of Section A, item 2.2. shall apply.

#### 2.1. Alternative C1 (British Telecom)

### 2.1.1. Modulation and coding

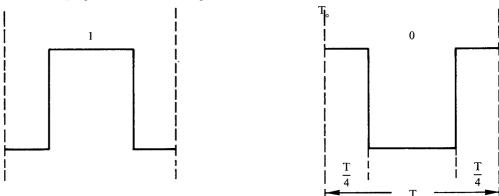

- (a) All timing signals for the modulator shall be derived from the receive line signal.

- (b) The modulation system shall be a modified form of diphase transmission known as  $Wal_2$  carrier transmission. This consists of phase reversals of a rectangular carrier signal whose fundamental frequency in Hz is nominally equal to the line bit rate in bit/s. The carrier will be such taht its transitions occur at  $t = t_o + \frac{T}{4}$  and  $t = t_o + \frac{3T}{4}$ , where T =one line data element period and the period of one carrier

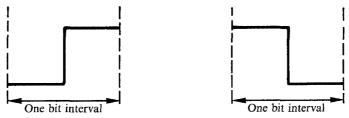

cycle, and  $t = t_0$  is the time of the start of a transmitted data element. The two basic elements of the unfiltered Wal<sub>2</sub> signal are shown in Figure 11.

Figure 11. Wal, basic elements.

(c) The TUB shall be designed to demodulate satisfactorily a line signal generated as described in item 2.1.1.b above, and will be recovered via an unamplified line having an insertion loss of up to 45 dB at a frequency equal to that of the carrier signal.

The line will be standard local line plant and no adjustment facilities shall be required to accommodate line characteristics.

#### 2.1.2. Scrambling

The data received on the data input interconnecting circuit shall be scrambled and differentially encoded before being modulated and transmitted to line. Similarly the demodulated data shall be differentially decoded and descrambled before being presented on the data output interconnecting circuit.

The scrambling and descrambling process shall be as described in CCITT Recommendation V.35 Appendix 1, i.e. the generating polynomial is:

$$1 + x^{-3} + x^{-20}$$

The differential encoding and decoding shall be a scrambling and descrambling process with generating polynomial:

$$1 + x^{-1}$$

#### 2.1.3. Line interface

- (a) In addition to the following requirements, the general requirements of Recommendation T/CD 01-01 shall apply.

- (b) The TUB shall be capable of carrying a wetting current of magnitude in the range 5 to 8 mA.

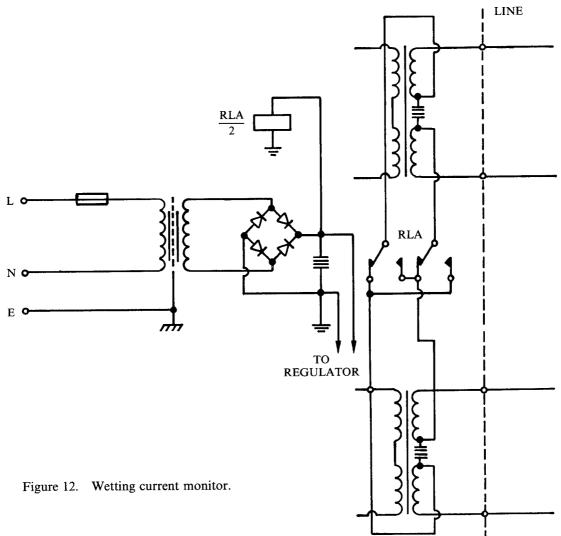

- (c) Failure of the DTE power supply shall cause a change in direction of flow of the wetting current in the second pair of the 4-wire circuit (see Figure 12).

- (d) The use of a line wetting current shall not degrade the performance of the TUB.

#### 2.1.4. Line signal requirements

- (a) The requirements of Recommendation T/CD 01-01 shall apply.

- (b) If the level of the signal at the receive line terminals is below -48 dBm, then the TUB shall take the following action:

- Clamp data on the data output interconnecting circuit to a constant binary 1.

Present a binary 0 condition on the Received Line Signal Detector interconnecting circuit.

The TUB shall not resume normal operation until the level of the signal at the receive line terminals is above -45 dBm.

#### 2.1.5. Equalization

The shape of the Wal<sub>2</sub> modulated line spectrum is such that it can be considered as having pre-equalization, thus a requirement for an equalizer in the receiver is not envisaged.

#### Alternative C2 (Austrian PTT) 2.2.

#### 2.2.1. Coding

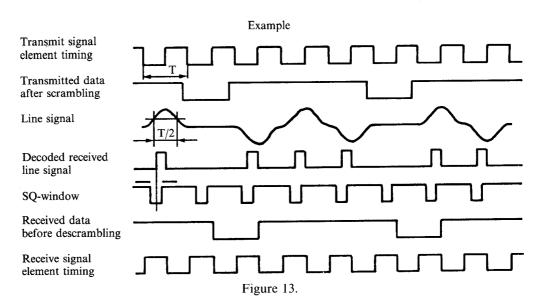

The coding process produces a raised cosine pseudo ternary line signal (Ist order, base band—alternative mark inversion) See Figure 13.

#### 2.2.2. *Timing*

All timing signals for the modulator shall be derived from the received line signal.

#### 2.2.3. Scrambling

The same scrambler is used as in Section A, item 2.1.4. However, the guard circuitry shown in Annex 3 is mandatory.

#### 2.2.4. Line interface

- (a) The requirements of Recommendation T/CD 01-01 shall apply.

- (b) The TUB shall be capable of carrying a wetting current of 3 mA maximum.

- (c) The use of the wetting current shall not degrade the performance of the TUB.

#### 2.2.5. Line signal requirements

- (a) The requirements of Recommendation T/CD 01-01 shall apply.

- (b) Threshold of received line signal detector.

Levels of received line signal:

greater than -40 dBm circuit A "ON"

ess than -41 dBm circuit A "OFF".

(c) Response time of circuit A

A fall in level of the incoming line signal to -41 dBm or lower for more than  $10\pm 5$  ms will cause circuit A to be turned OFF.

An increase in level to -40 dBm or higher will, within  $10\pm5$  ms, turn this circuit ON.

(d) Clamping to binary 1 condition of circuit DR (data output, received data) Circuit DR is held in a marking condition (binary 1), when circuit A is in the OFF condition.

When this condition does not exist, the clamp is removed and circuit DR can respond to the input signals of the TUB.

### 2.2.6. Equalization

- (a) In most applications, no manual adjustment of the equalizer shall be required.

- (b) For exceptional cases, a manual fine adjustment of the equalization shall be possible to achieve optimum signal quality, particularly with longer subscriber lines. The manual adjustment would also be needed if, for any reason, a higher transmit level were used (3 dB is suggested in cases of severe electrical noise).

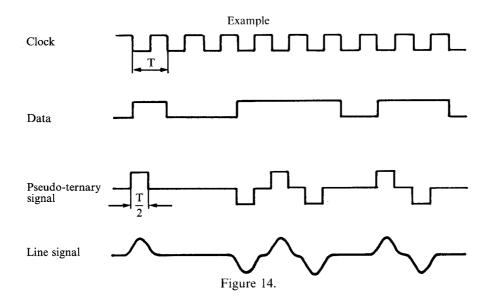

#### 2.3. Alternative C3 (Deutsche Bundespost)

#### 2.3.1. *Coding*

The coding process produces a raised cosine half-bauded pseudo-ternary line signal (alternate mark inversion code AMI). The wave shaping is depicted below (Figure 14).

#### 2.3.2. *Timing*

All timing signals for the modulator shall be derived from the received line signal except for the case of a test loop 3a being activated, in which case the TUB has to maintain all necessary timing signals towards the CU with a frequency tolerance of  $\pm 0.01\%$  from nominal value.

#### 2.3.3. Scrambling

The same scrambler is used as described in Section A, 2.1.5. The guard circuitry shown in Annex 3 is mandatory.

#### 2.3.4. Line interface

- (a) In addition to the following requirements, the general requirements of Recommendation T/CD 01-01 shall apply.

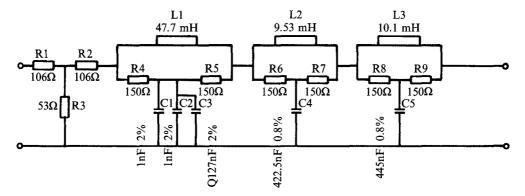

- (b) The nominal impedance shall be jumper-selectable: either 150 ohms or 1,000 ohms.

#### 2.3.5. Line signal requirements

- (a) In addition to the following requirements, the general requirements of Recommendation T/CD 01-01 shall apply.

- (b) The peak-to-peak line signal voltage shall be 1.4 Vp-p with tolerances of +10%/-20% measured with an 150 ohms non-inductive load resistance.

- (c) If the voltage of the received signal is below 7 mVp-p, than the TUB shall take the following actions:

- Clamp data on interchange access point Do to a constant binary 1.

- Present an OFF condition on interchange access point Ao.

The TUB shall not resume normal operation until the voltage of the received signal is above 14 mVp-p.

#### 2.3.6. Equalization

The TUB shall be equipped with an automatic adaptive equalizer which shall cater for both the equalization of the attenuation distortion of unloaded cables and the attenuation and phase distortion of loaded cables. The phase equalizer may be switched in manually.

### 2.4. Alternative C4 (NPDN)

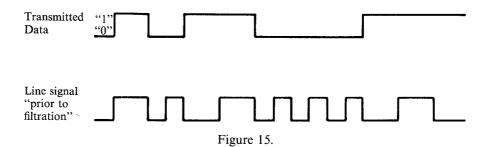

#### 2.4.1. Modulation and coding

- (a) All timing signals for the modulator shall be derived from the received line signal.

- (b) The modulation system is based on differential biphase modulation (biphase-space) of a square wave carrier with fundamental frequency in Hz nominally equal to the data signalling rate in bit/s.

The line signal shall consist of a two-level signal with the following transitions:

"1" transition at  $t = t_o$

"0" transition at  $t = t_0 + \frac{T}{2}$  and  $t = t_0$ ,

where T signifies the period of one data element, and t<sub>o</sub> is the time at which a data element begins (see Figure 15).

- (c) The following maintenance functions shall be included. If the received line signal detector is in the OFF condition, transmission in the opposite direction shall cease either after a time delay of 2.5 seconds or alternatively controlled by the CU via the use of interchange circuit LEA.

- (d) The TUB shall be designed to demodulate satisfactorily a line signal generated as described in item 2.4.1.c) above and transmitted via an unamplified line having an insertion loss of 40 dB at a frequency equal to that of the carrier signal.

The received line signal detector shall have a hysteresis of a least 2 dB.

#### 2.4.2. Scrambling

Data scrambling is not employed.

#### 2.4.3. Line interface

- (a) In addition to the following requirements the general requirements of Recommendation T/CD 01-01 shall apply.

- (b) The TUB shall be capable of carrying a wetting current of magnitude in the range 5-15 mA.

- (c) The use of a line wetting current shall not degrade the performance of the TUB.

- (d) When a timer within the TUB is used to control the "transmit inhibit" function specified in item 2.4.1.c) above this function shall be implemented in such a way that the MTBF for all the circuitry of concern for this function is at least one magnitude greater than the MTBF for the whole TUB.

- (e) The TUB shall be provided with a "power-off" generator with the characteristics described in Section B, item 6. The generator shall be powered from the wetting current in the receiver line.

#### 2.4.4. Line signal requirements

- (a) In addition to the following requirements, the general requirements of Recommendation T/CD 01-01 shall apply.

- (b) The transmit level shall be 0 dBm or -6 dBm (strappable) when measured with pseudo-random (511-bit pattern) data against a resistive impedance of 600 ohms. Tolerance at nominal level:  $\pm 1$  dB.

- (c) If the received line signal detector is in the OFF condition, then the TUB shall clamp data in the data output interconnecting circuit to a constant binary 1.

#### 2.4.5. Equalization

The TUB should be preferably equipped with an adaptive equalizer in the receiver.

#### 2.4.6. Performance

- (a) The receiver clock in the TUB shall maintain its phase and frequency for at least 500 ms in order to avoid resynchronization in case of short breaks on the line. This also implies that the TUB shall not produce a bit slip when the line signal returns after a short break on the line.

- (b) Amplitude hits on the line of up to 10 V and with a duration of up to 15-bit lengths shall not cause any bit slip in the TUB.

#### 2.5. Alternative C5 (Italian PTT)

#### 2.5.1. Modulation and coding

- (a) All timing signals for the modulator shall be derived from the received line signal.

- (b) The modulation system is based on differential diphase modulation of a square wave carrier with fundamental frequency in Hz nominally equal to the data rate in bit/s.

The following relation is forecast:

Digit 0 – No phase inversion

Digit 1 - Inversion of the phase.

(c) The TUB shall be designed to demodulate satisfactorily a line signal generated as described above, and will be recovered via an unloaded line having an insertion loss of up to 40 dB at the frequency equal to the data rate.

#### 2.5.2. Scrambling

Data scrambling is not employed.

#### 2.5.3. Line interface

- (a) In addition to the following requirements, the general requirements of Recommendation T/CD 01-01 shall apply.

- (b) The TUB shall be capable of carrying a wetting current of 3 mA maximum, without decreasing the performance of the TUB.

#### 2.5.4. Line signal requirements

- (a) The requirements of Recommendation T/CD 01-01 shall apply.

- (b) If the level of the signal at the receive line terminals is 6-12 dB below the minimum level, the TUB shall take the following action:

- Clamp data on the data output interconnecting circuits to a constant binary 1.

- Present a binary 0 condition on the received Line-Signal-Detector interconnecting circuit.

The TUB shall not resume normal operation until the level of the signal at the receive line terminals is 6 dB above the minimum level.

The minimum level is the level received at the output of an artificial line (Figures 16 and 17) having an attenuation loss of 40 dB at the frequency equal to the data rate, the transmitted signal shall be +6 dBm with a pseudo-random sequence of 511-bits.

#### 2.5.5. Equalization

A simple amplitude equalizer is used without manual adjustment.

#### 2.6. Alternative D1 (Deutsche Bundespost)

Alternative D1 is a 2-wire duplex TUB using the echo cancellation technique.

### 2.6.1. *Coding*

The same coding is used as for alternative C3 (item 2.3.1.).

#### 2.6.2. *Timing*

The same requirements as for alternative C3 apply (item 2.3.2.).

#### 2.6.3. Scrambling

The scrambling and descrambling process shall be as described in CCITT Recommendation V.35, Appendix 1, i.e. the generating polynomial is:

$$1 + x^{-3} + x^{-20}$$

#### 2.6.4. Line interface

- (a) In addition to the following requirements, the general requirements of Recommendation T/CD 01-01 shall apply.

- (b) The nominal impedance of the line interface shall be 150 ohms.

### 2.6.5. Line signal requirements

- (a) In addition to the following requirements, the general requirements of Recommendation T/CD 01-01 shall apply.

- (b) The peak-to-peak line signal voltage shall be 1.0 Vp-p with a tolerance of  $\pm 15\%$ , measured with an 150 ohms non-inductive load resistance.

- (c) If the voltage of the received signal is below 40 mVp-p, then the TUB shall take the following action:

- Clamp-data on interchange access point Do to constant binary 1.

- Present on OFF condition on interchange access point A0.

The TUB shall not resume normal operation until the voltage of the received signal is above 60 mVp-p.

#### 2.6.6. Equalization

The TUB shall be equipped with an automatic adaptive equalizer capable of equalizing the attenuation distortion of unloaded cables.

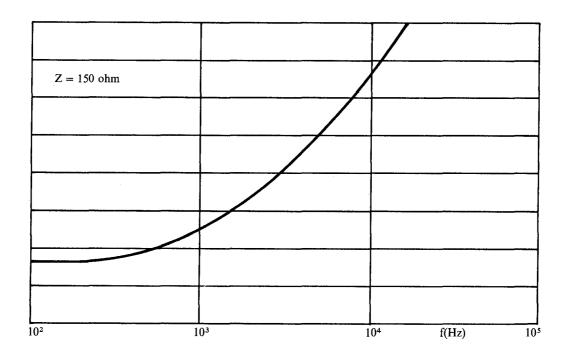

Figure 16. Artificial network.

Tolerance of resistance  $\leq 0.5\%$

Figure 17. Electric scheme.

#### 2.7. Alternative D2 (Norway)

#### 2.7.1. Modulation and coding

- (a) The 2-wire duplex TUB uses the echo cancellation method.

- (b) All timing signals for the modulation shall be derived from the line signal.

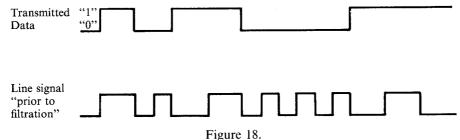

- (c) The modulation system is based on differential biphase modulation (biphase-space) of a square wave

The line signal shall consist of a two-level signal with the following transitions:

"1" transition at  $t = t_0$

"0" transition at  $t = t_0 + \frac{T}{2}$  and  $t = t_0$ ,

where T signifies the period of one data element and t<sub>o</sub> is the time at which the data element begins (see Figure 18).

- (d) The signalling rate on the line is fixed at 12 kbit/s.

- To convert the original 3,000 bit/s envelope structured bit stream into the 12,000 bit/s bit stream, each bit of the original bit stream is transmitted 4 times.

- (e) The following maintenance functions shall be included. If the received line signal detector is in the OFF condition, transmission in the opposite direction shall cease either after a time delay of 2.5 seconds or be alternatively controlled by the CU via the use of interchange circuit LEA (loss of envelope alignment).

- (f) The TUB shall be designed to demodulate satisfactorily a line signal generated as in item 2.7.1.c) above and transmitted via an unamplified line having an insertion loss of 40 dB at a frequency equal to that of the carrier signal.

The received line signal detector shall have a hysteresis of at least 2 dB.

#### 2.7.2. Scrambling

The TUB will require scrambling of the line signals using scrambler polynoms of different lengths for the two transmission directions.

Scrambler in the transmitter is characterizer by:

Polynom:  $1 + x^{-6} + x^{-7}$

Scrambler in the receiver is characterized by:

Polynom:  $1 + x^{-3} + x^{-5}$

#### 2.7.3. Line interface

- (a) In addition to the following requirements, the general requirements of Recommendation T/CD 01-01 shall apply.

- (b) The TUB shall be capable of carrying a wetting current of magnitude in the range 5-15 mA.

- (c) The use of line wetting current shall not degrade the performance of the TUB.

- (d) When a timer within the TUB is used to control the "transmit inhibit" function specified in item 2.7.1.e) above this function shall be implemented in such a way that the MTBF for all the circuitry of concern for this function is at least one magnitude greater than the MTBF for the whole TUB.

- (e) The TUB shall be provided with a "power-off" generator with the characteristics described in Section B, item 6. The generator shall be powered from the wetting current in the line.

### 2.7.4. Line Signal Requirements

- (a) In addition to the following requirements, the general requirements of Recommendation T/CD 01-01 shall apply.

- (b) The transmit level shall be 0 dBm or -6 dBm (strappable) when measured with pseudo-random (511-bit pattern) data against the nominal impedance. The tolerance is  $\pm 1$  dB.

- (c) The nominal impedance consists of a resistor of 120 ohms connected in cascade with a 820 ohm resistor. The 820 ohm resistor is shunted with a 110 nF capacitor.

- (d) If the received line signal detector is in the OFF condition then the TUB shall clamp data on the data output interconnecting circuit to a constant binary 1.

#### 2.7.5. Equalization

The TUB should be equipped with an adaptive equalizer in the receiver.

#### 2.7.6. Receiver clock requirement

The receiver clock in the TUB shall maintain its phase and frequency for at least 100 ms in order to avoid resynchronization. This also implies that the TUB shall not produce a bit slip when the line signal returns after a short break on the line.

### 3. TESTING AND MEASURING REQUIREMENTS

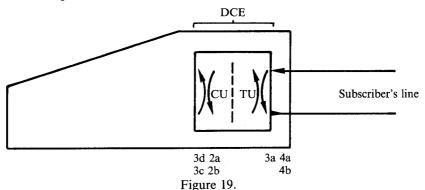

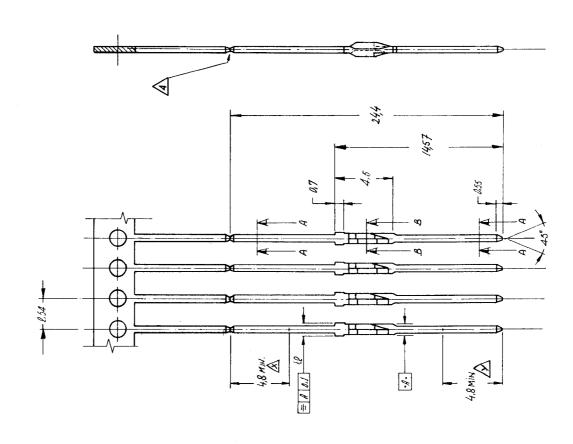

#### 3.1. **Test loops** (see Figure 19)

The definitions of the loops are set out in CCITT Recommendation X.150.

Two types of additional test loops (in addition to loop 2a/2b, see Section A, item 4) shall be provided in the DCE:

#### (a) Test loop towards the DTE

Loop 3a: this loop is automatically activated, locally controlled (see also Section A, item 2.1.5., Note 4);

Loop 3c/3d: this loop is manually or automatically activated, locally controlled.

#### (b) Test loops towards the network

Loop 4a or 4b: this loop is manually activated, locally controlled.

If the loop is activated, the DCE will signal "DCE not ready" towards the terminal.

The following Table 3 gives the various additional test loop which are used in the different networks as identified so far:

| Network | Test loops<br>3a   3c/3d   4b |   |   |

|---------|-------------------------------|---|---|

| FRG     | X                             |   |   |

| I       |                               | X | X |

| NPDN    |                               | X |   |

| A       |                               | X |   |

| UK      | $\mathbf{X}^{1)}$             | X |   |

<sup>1)</sup> Administration use only.

Table 3.

#### 3.2. Test-call facility

#### 3.2.1. Alternative A (NPDN)

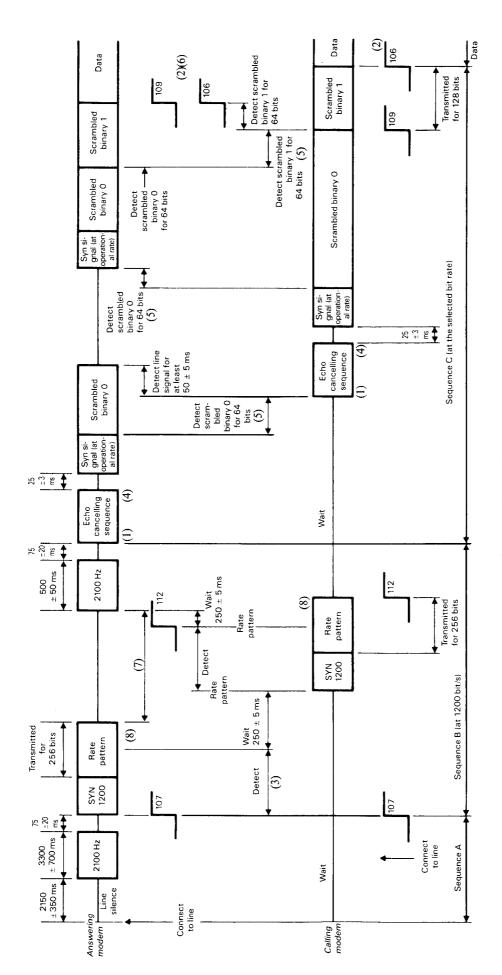

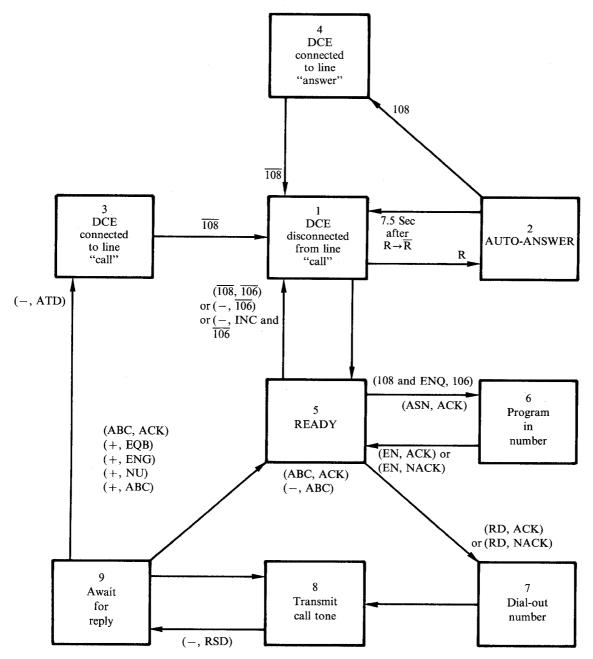

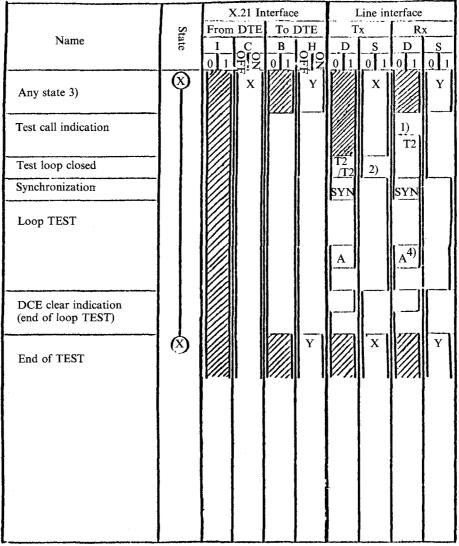

3.2.1.1. Test call from the DCE (loops 3d and 2a) (see Annex 11).

#### Test initiation

The test is initiated by pressing the TEST key on the DCE, whereupon 3 envelopes of CLEAR are sent to the network. Thereafter READY (at least 3 envelopes) is sent to the network until the DCE receives READY from the network. The DCE sends this sequence of CLEAR followed by READY to guarantee that the DCE, including the subscriber's circuit, changes to READY state, i.e. that any encapsulations are cancelled

When the DCE has detected READY from the network, it proceeds automatically to send TEST CALL T1 to the network. The network answers the test call by sending T2.

When the DCE has detected T2, loop 2a is closed to the network. The loop is placed in the interface to the terminal and includes also the interface generators and receivers towards the terminal. The loop implies that the interchange circuits Receive and Transmit as well as the circuits Control and Indication are interconnected.

#### Loop test

For the DCE's which are strapped for SYN-synchronization to the terminal the looped information is displaced 1 bit relative to the network. The 1-bit displacement continues until SYN-synchronization has occurred in the DCE. The SYN-synchronization circuits were activated when the DCE detected T2. The exchange can now test the SYN-synchronization circuits by sending SYN to the DCE, whereupon the bit displacement from the DCE will no longer be performed.

The loop test continues by sending 1, ON (READY FOR DATA) from the network. When the network detects 1, ON from the DCE, the network sends two envelopes of SYN', ON (SYN' is SYN displaced 1 bit relative to the envelope) and then changes to 0, ON.

If the network then detects these envelopes of SYN', ON followed by 0, ON, the network will send 1, OFF to the DCE. When these are returned and detected by the network, the loop test is complete. It has then been tested that the SYN-synchronization circuits are not activated in data phase, and that status bits and data bits are transmitted without distortion.

For the DCE's which are strapped for byte timing synchronization, no displacement of the returned test call character takes place on closure of the loop.

After the network has tested the loop, the loop connection is deactivated by sending CLEAR to the DCE, whereupon the DCE sends the test call character T1 to the network.

If no fault has been detected in the loop test, the network sends from special envelopes which is interpreted by the DCE as TEST OK. When this signal from the network is detected by the DCE, this is indicated by flashing of the TEST lamp as long as the TEST key is depressed. If the test to the network fails, the TEST lamp will glow steadily as long as the TEST key is depressed. Test call character T1 is sent to the network as long as the TEST key is pressed.

The subscriber connection will be encapsulated until the TEST key is depressed and READY state exists. When the TEST key is depressed, the DCE sends the test call character T1 to the network for another 100 ms before the actual through-connection in the DCE takes place in order to avoid generation of a false call to the network by contact bounce or the like.

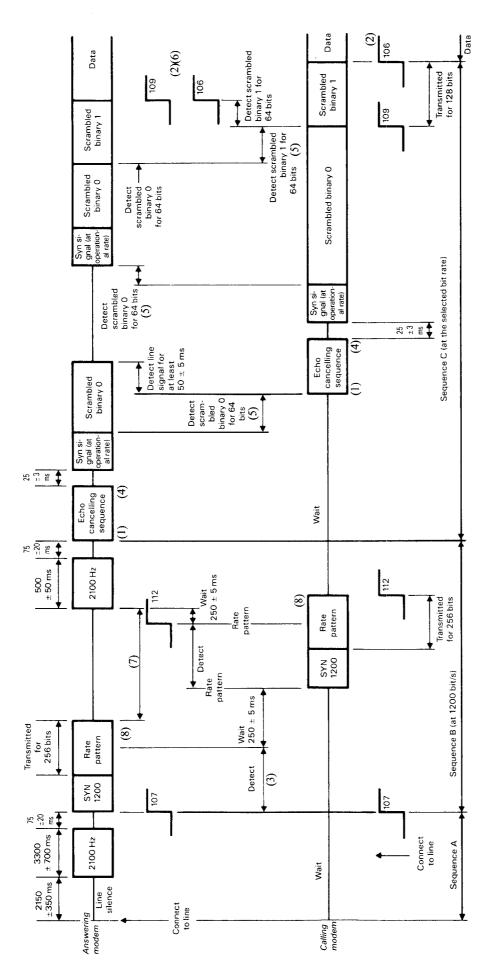

#### 3.2.1.2. Test call from the network (loop 2b)

#### See Annex 12

As for the test from the DCE, this test can be initiated regardless of the original state of the DCE or DTE. A test will, however, never be initiated to a subscriber who is already engaged in a call to the network. The test is initiated by the network sending four envelopes of CLEAR (0/OFF) followed by test indication T2, whereupon the loop 2b is closed in the DCE.

On closure of the test loop, the test of the DCE follows the same procedure as when the test is initiated from the DCE.

The test from the network terminates with opening of the test loop by sending of CLEAR to the DCE. No TEST OK is sent to the DCE. The test is interrupted when a fault in the procedure or the signal is detected by the network. This results in encapsulation of the subscriber connection.

During the test Receive and Indication are set to 0 and OFF respectively.

#### 3.2.2. Alternative B (Austrian PTT)

### 3.2.2.1. Test call from the subscriber to the network (loop 2a and 3d)

A test key in the terminal is used to initiate the test call by controlling the interchange circuit TA (test activation) to ON. (ON will be maintained as long as the TEST key is depressed.)

If the network is able to accept a call (that means that the state "DCE Ready" is given), the interchange circuit TI1 (test indication) is set to ON and the terminal shall indicate by means of a TEST lamp that a test is in progress.

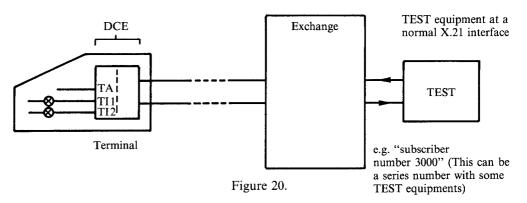

If the TA is ON (and TI1 is ON), the DCE automatically dials a certain number (standardized for the whole country, e.g. 3,000) in order to get a connection with a TEST-equipment (see Figure 20).

After the connection is established, the DCE transmits a TEST word W (a special envelope, status bit is set to "0").

If 8 TEST words W are received by the TEST-equipment, this equipment transmits a TEST word W' (status bit is set to 0 and TEST word W is incremented by 1) as long as the TEST key is depressed.

The CU detects the TEST words W' and controls the interchange circuit TI2 to ON. If one of the received TEST words is wrong, the CU controls the interchange circuit TI2 to OFF and holds this state for 0.5 s, independent of the fact whether right words have been received during this time or not.

The terminal shall indicate the situation "TEST OK" by means of a second TEST lamp depending on the state of interchange circuit TI2 (see Figure 20).

While the test is in progress, DNR will be sent to the terminal.

When the TEST key is released, the test is interrupted and the DCE clears the call automatically.

#### 3.2.2.2. Test between 2 subscribers

This test is only possible, if the "testing DTE" is able to generate a test pattern in a certain format, synchronized with the byte timing, and is able to interpret the receiving test pattern.

The test will be initiated after the connection is established to the "tested DTE".

The following test pattern will be transmitted while C = OFF:

The DCE of the "tested DTE" will send back the following test pattern, if the DCE has received 8 test patterns from the "testing DTE" without failures:

If transmission errors are detected, another test pattern will be sent back:

If the DCE of the "tested DTE" cannot find a valid test pattern in 4 consecutively received bytes, it will go back to state 13 (Data transfer).

The test period is limited to 1 s (After this time the connection will be cleared by the "testing DCE".) During the test, loop 3 of the "tested DCE" will be activated.

#### 3.2.2.3. Test call from the network

From a TEST-equipment in the exchange a test call can be initiated.

- (a) At first by manual dialling a connection to the relevant subscriber has to be established.

- Afterwards the TEST word W with status bit "0" will be sent to the subscriber, in order to be able to distinguish between TEST pattern and normal data in the data phase of a connection.

- If 8 TEST words W are received by the CU, the CU checks if during this time the interchange circuit SQ (signal quality, *Note 1*) is set to ON (if a certain threshold of quality for all received bits is given).

- If this is the case, the TEST word W' is sent back (loop 2a) to the network.

- If this is not the case, the TEST word W'' (status bit is set to "0", TEST word W is incremented by 2) is sent back (loop 2a) to the network.

- If during the test the CU detects a wrong TEST word W, a TEST word W''' (status bit is set to "0", TEST word W is incremented by 3) is sent back (loop 2a) to the network.

The TEST-equipment interprets the incoming signals.

(b) If the connection to the relevant subscriber cannot be established by dialling, another TEST-equipment can be directly connected to the subscriber's line, and the same tests as described in item a) can be made. While the test is in progress, from the DCE DNR will be sent to the terminal, and the interchange circuit TI1 is set to ON.

Note 1: The signal quality is regarded as unsatisfactory, if—in the case of a TUM—the phase deviation is greater than 22.5° for a period of at least 5-20 ms. The signal quality is regarded as satisfactory if the phase deviation is less than 22.5° for a period of at least 40-100 ms.

If a TUB is used, the signal quality is regarded as unsatisfactory, if the "decoded received line-signal" is more than T/4 too early or too late with respect to the nominal position. The signal quality is regarded as satisfactory, if a least 1,000 consecutive bits are within the "time window of T/2".

#### 3.2.3. Alternative C (Deutsche Bundespost)

#### 3.2.3.1. General

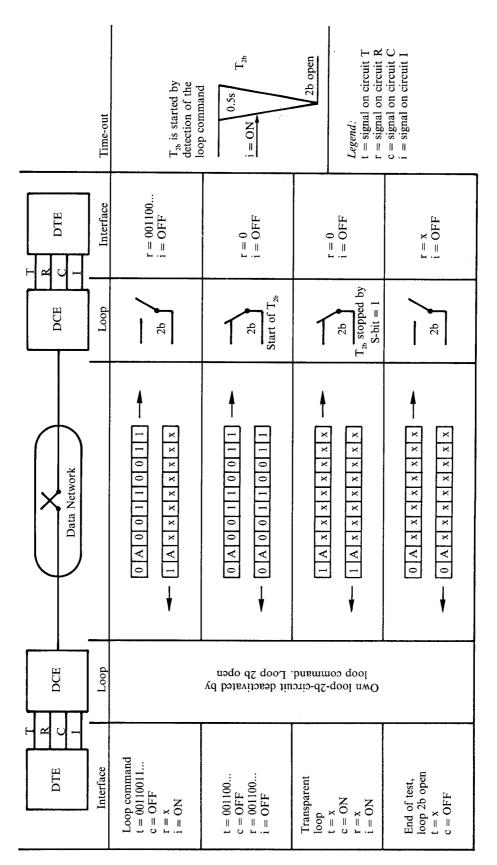

Besides other means of network maintenance, provision for a transparent loop 2b is made in the IDN of the DBP. This loop may be activated at any time during the data transfer phase of a data connection.

Note 1: In this respect, "data connection" is also to be understood in conjunction with a connection established to or from a network test center.

#### 3.2.3.2. Loop activation

The DTE wishing to activate loop 2b, in the far-end DCE transmits the loop command

$$t = 001100..$$

$c = OFF$

By detecting the incoming loop command pattern in an 8+2-envelope

$$S-bit = 0$$

data bits = 001100...

the remote DCE closes its loop 2b thus reflecting the loop command to the initiating station. This station now has the choice of either making the loop transparent by turning ct. C from OFF to ON or letting time-out  $T_{2b}$  expire which, after 0.5 s, will automatically cause the loop 2b to open.

In the other case, c = ON ( $\triangleq$  S-bit = 1) will keep the loop 2b closed until it is released by incoming envelopes with S-bit = 0 ( $\triangleq$  c = OFF in the initiating station).

Figure 21 illustrates the loop activation procedure.

### 3.2.4. Alternative D (Italian Administration)

(a) Loop activation

The DTE wishing to activate loop 2b in the far-end DCE transmits the loop command

$$c = OFF$$

$$t = 111100$$

The DCE detecting the incoming loop pattern in a 6+2-envelope

$$S-bit = 0$$

data bits = 111100

for a minimum of 8 envelopes (when the loop is activated from the network, 32 envelopes will be transmitted) closes its loop 2b (see Figure 22).

(b) Test phase

A maximum of 7 test characters continuously can be transmitted. When the loop is activated from the network, a sequence of 2 test characters and 2 loop characters will be transmitted.

(c) Termination phase

At least a sequence of 8 characters different by loop character must be transmitted.

Figure 21. Remote control of loop 2b in the PDN of the Deutsche Bundespost.

Figure 22.

#### 4. EQUALIZER TO BE PROVIDED IN THE TUM

A compromise equalizer or manually adjustable equalizers shall be provided which are capable of equalizing the following line conditions:

1 to 3 carrier links

0 to 5 km unloaded cable

0 to 30 km loaded cable (different national loading rules apply).

If a compromise equalizer will be used, this equalizer shall always be located at the receiver side.

If manually adjustable equalizers will be used, there are 2 possibilities of location:

- (a) In order to minimize unit cost on manually adjustable equalizer shall be located in each receiver. Both ends of a links must be adjusted during installation.

- For the unloaded cable a compromise equalizer will be used also at the receiving side only.

- (b) In order to have the possibility of equalizing both directions of transmissions at one side 2 manually justable equalizers shall be provided in each unit. Both can be involved in one link at a time.

For the unloaded cable a compromise equalizer will be used at the receiving side only.

The following Table 4 gives the various kinds of equalizing which are used in different networks:

| Network | Only compromise equalizer | Manually adjustable equalizer one (a) two (b) |   |

|---------|---------------------------|-----------------------------------------------|---|

| A       |                           | X                                             |   |

| FRG     | X                         |                                               |   |

| I       | X                         |                                               |   |

| NPDN    |                           |                                               | X |

Table 4.

### 5. LINE WETTING

From the network side a wetting current will be injected on each pair of the 4-wire line to the TU, according to the following table. Besides preventing corrosion in contacts, the wetting current can be used to supply a "Power-off" generator in the DCE-TU.

The following requirements related to the wetting current arrangement apply (see Table 5).

| Network | Max. line wetting current |

|---------|---------------------------|

| A       | 3 mA                      |

| I       | 3 mA                      |

| NPDN    | 15 mA                     |

Table 5.

- the DC-resistance of the line transformers shall be less than 300 ohms (less than 400 ohms can be accepted if the 1,600-ohm line impedance option at the network side is applicable);

- the absence of wetting current shall not have any influence on the performance of the TU.

- 6. **DCE POWER-OFF SIGNAL** (used in the NPDN for the purpose of causing the appropriate call progress signal (47) to the calling DTE)

The TU shall be provided with a "Power-off" generator which shall be connected to the line, if one or more of the power supply voltages fail(s) for more than 30 ms.

When the power-off generator is activated, a square wave oscillator shall be switched on and connected to the line, transmitting a signal with the frequency  $1,000\pm100$  Hz for the TUB and  $1,800\pm200$  Hz for the TUM. This signal shall be modulated with a square wave of the frequency 1.7-3 Hz, so that the signal is ON 35-65% of the time, and OFF 65-35% of the time. The modulation shall always start with an OFF-period longer than 100 ms. The transmit level shall be the same as with the data signal.

The power-off generator shall be able to work with a current supply of 5-15 mA. The power-off generator will be powered either from accumulators situated in the DCE or from the wetting current on the receiver line. When powered from the accumulators these shall be able to power the power-off generator for at least 70 continuous hours. When powered from the wetting current in the receiver line, it shall be independent of the branch polarities. The TU shall function properly until the power-off generator is turned ON. The voltage drop over the power-off generator shall be within the range 5-8 V.

7. **CHARACTER ALIGNMENT** (applies only if character alignment is established in the DCE) (Used in the NPDN)

The DCE synchronizes on the first SYN-character from the DTE with control = ON after passing clearing and having detected READY (data = 1 and the status bit = 0 in one envelope) in both directions. All SYN-characters are sent to the network. If the DCE has synchronized on a SYN-character, the DTE can take place until READY has been redetected in both directions after clearing.

When tested, the DCE synchronizes on the first SYN-character occurring after initiation of the test.

As long as the DCE regards itself as being in data transfer phase, no synchronization on SYN-characters takes place. The DTE will then be responsible for establishing its own alignment, e.g. by using the byte timing or by SYN-characters.

When the DCE detects an envelope with data = 1 and status = 1 in both directions to and from the DCE, the DCE is regarded as being in data transfer phase.

When the DCE detects CLEAR from the network (data and status = 0 in two envelopes) or CLEAR from the DTE, or receives time-out after loss of envelope alignment, the DCE is regarded as no longer being in data transfer phase.

8. **ELECTRICAL CHARACTERISTICS AND SIGNIFICANT LEVELS** of the interchange circuits between the TU and the CU (see also the note under Section A, item 2.1.2.).

#### 8.1. Possibility A

The same electrical characteristics and significant levels are used as for the interface between the CU and the terminal (see Section A, item 3.2.3.).

#### 8.2. Possibility B (Deutsche Bundespost)

For the IDN a particular set of characteristics for an unbalanced single-current interface was developed and is described below (the so-called EDS-A-interface).

#### 8.2.1. Generator characteristics

The generator in an interchange circuit shall withstand an open circuit and a short circuit condition between itself and any other interchange circuit (including generators and loads) without sustaining damage to itself or its associated equipment.

The open circuit voltage (U<sub>0</sub>) shall be

for the OFF/ZERO condition  $U_o = 0 \ V \ {}^{+0.5}_{-1.5} \ V$

for the ON/ONE condition  $U_{o} = 5~V~ {+1.5~V \over -0.5~V} \label{eq:U0}$

The generator impedance is  $R_A = 100 \text{ ohms } \pm 10\%$

The maximum generator shunt capacitance is  $C_{A max} = 2 nF$

The rise time shall be  $S\!\geq\!0.2~V/\mu s~\text{within the range}\\ U_A = +1.2~V~...~+2.8~V$

(When terminated with the nominal load as defined in 8.2.2.)

#### 8.2.2. Load characteristics

The load circuitry recognizes

the OFF/ZERO condition at an input voltage  $U_F \triangleq +1.2 \text{ V}$

the ON/ONE condition at an input voltage  $U_E \ge +2.8 \text{ V}$

The region between +1.2 V and +2.8 V is defined as the transition region. The maximum tolerable input voltage is  $\pm 8$  V.

The load impedance is  $R_{\rm E} = 400 \text{ ohms} \frac{+10\%}{-40\%}$

The load shunt capacitance is  $C_E = 10 \text{ nF } \pm 25\%$

A power-off condition at the input of the load shall be recognized as OFF/ZERO condition.

#### 8.2.3. Positions of the Timing Signal Transitions

For the EDS-A-interface the relationship between either timing signal and the corresponding data signal is such that a transition from the OFF to ON conditions of the timing signal shall nominally indicate the centre of each signal element of the data stream.

Note: This is contrary to the regulation in CCITT Recommendation V.24.

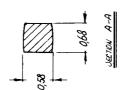

#### 9. CONNECTOR (CU TO TU) USED BY THE DEUTSCHE BUNDESPOST

The connector is a 31-pin connector according to DIN 41617. The pin assignment is given in Table 6.

| Pin No. | Access point designation | Circuit name                                         |

|---------|--------------------------|------------------------------------------------------|

| 1       | G                        | Signal ground or common return                       |

| 2       | +5 V                     | Power supply circuit                                 |

| 3       | Di                       | Transmitted data                                     |

| 4       | G                        | Signal ground or common return                       |

| 5       | TS1i                     | Transmitter signal element timing (CU)               |

| 6       | G                        | Signal ground or common return                       |

| 7       | Do                       | Receiver Data                                        |

| 8       | G                        | Signal ground or common return                       |

| 9       | RS10                     | Receiver signal element timing                       |

| 10      | G                        | Signal ground or common return                       |

| 11      | Ao                       | Received line signal detector                        |

| 12      | LA1i                     | Loop 3a activation                                   |

| 13      | TS2o                     | Transmitter signal element timing (TU)               |

| 14      | G                        | Signal ground or common return                       |

| 15      |                          | D and a standard                                     |

| 16      | +12 V                    | Power supply circuit                                 |

| 17      | (RS1i)                   | (not used)                                           |

| 18      | RS2o                     | Signal ground or common return 8× or 6× clock of RS1 |

| 19 20   | K520                     | 8 × OF 6 × Clock of RS1                              |

| 21      |                          |                                                      |

| 21 22   | TS3o                     | 8× or 6× clock of TS2                                |

| 23      | 1330                     | 8 × 01 0 × clock 01 132                              |

| 24      | Lo a (La)                | Line outgoing a-wire (Line a-wire for 2-wire TUB)    |

| 25      | Lo b (Lb)                | Line outgoing b-wire (Line b-wire for 2-wire TUB)    |

| 26      | G                        | Signal ground or common return                       |

| 27      | Li a                     | Line incoming a-wire                                 |

| 28      | Li b                     | Line incoming b-wire                                 |

| 29      | G                        | Signal ground or common return                       |

| 30      | G                        | Signal ground or common return                       |

| 31      | -12 V                    | Power supply circuit                                 |

Table 6.

### 10. TRANSMIT INHIBIT FUNCTION

The following maintenance function shall be included. If the received line signal detector is in the OFF condition, transmission in the opposite direction shall cease either after a time delay of 2.5 seconds or be alternatively controlled by the CU via the use of interchange circuit LEA. When a timer within the modem is used to control the transmit inhibit function, this function shall be implemented in such a way that the MTBF for all the circuitry of concern for this function is at least one magnitude greater than the MTBF for the whole modem.

#### Section C

#### 1. **GENERAL**

This section specifies optional requirements which may be included in a plug-in DCE.

#### 2. OPTIONAL INTERCHANGE CIRCUITS

#### 2.1. Interface between TU and CU

(a) The following Table 7 gives a list of optional circuits for the interface between TU and CU.

| Circuit<br>designation | Circuit name                                                | Access point designation CU   TU |

|------------------------|-------------------------------------------------------------|----------------------------------|

| DT <sub>2</sub>        | Transmitted data (line receiver)                            | Do <sub>2</sub> →Di <sub>2</sub> |

| DR <sub>2</sub>        | Received data (line driver)                                 | Di₂←Do₂                          |

| RS1 <sub>2</sub>       | Receiver signal element timing                              | $RS1i_2 \leftarrow RS1o_2$       |

| RS2 <sub>2</sub>       | $8 \times$ or $6 \times$ clock of RS1                       | $RS2i_2 \leftarrow RS2o_2$       |

| TS1                    | Transmitter signal element timing (CU) (Note 1)             | TS1o→TS1i                        |

| TS2                    | Transmitter signal element timing (TU) (Notes 1 and 2)      | TS2i←TS2o                        |

| TS3                    | $8 \times$ or $6 \times$ clock of TS2 ( <i>Notes 1, 2</i> ) | TS3i←TS3o                        |

| МС                     | Master clock                                                | MCo→MCi<br>or or<br>MCi←MCo      |

| SQ                     | Signal quality                                              | SQi←SQo                          |

| RC                     | Relais control (Note 1)                                     | RCo→RCi                          |

| LEA                    | Loss of envelope alignment                                  | LEAo→LEAi                        |

| LA1                    | Loop 3a activation                                          | LA1o→LA1i                        |

| -12 V                  | Power supply circuit                                        | -12   -12                        |

| +12 V                  | Power supply circuit                                        | +12 +12                          |